Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

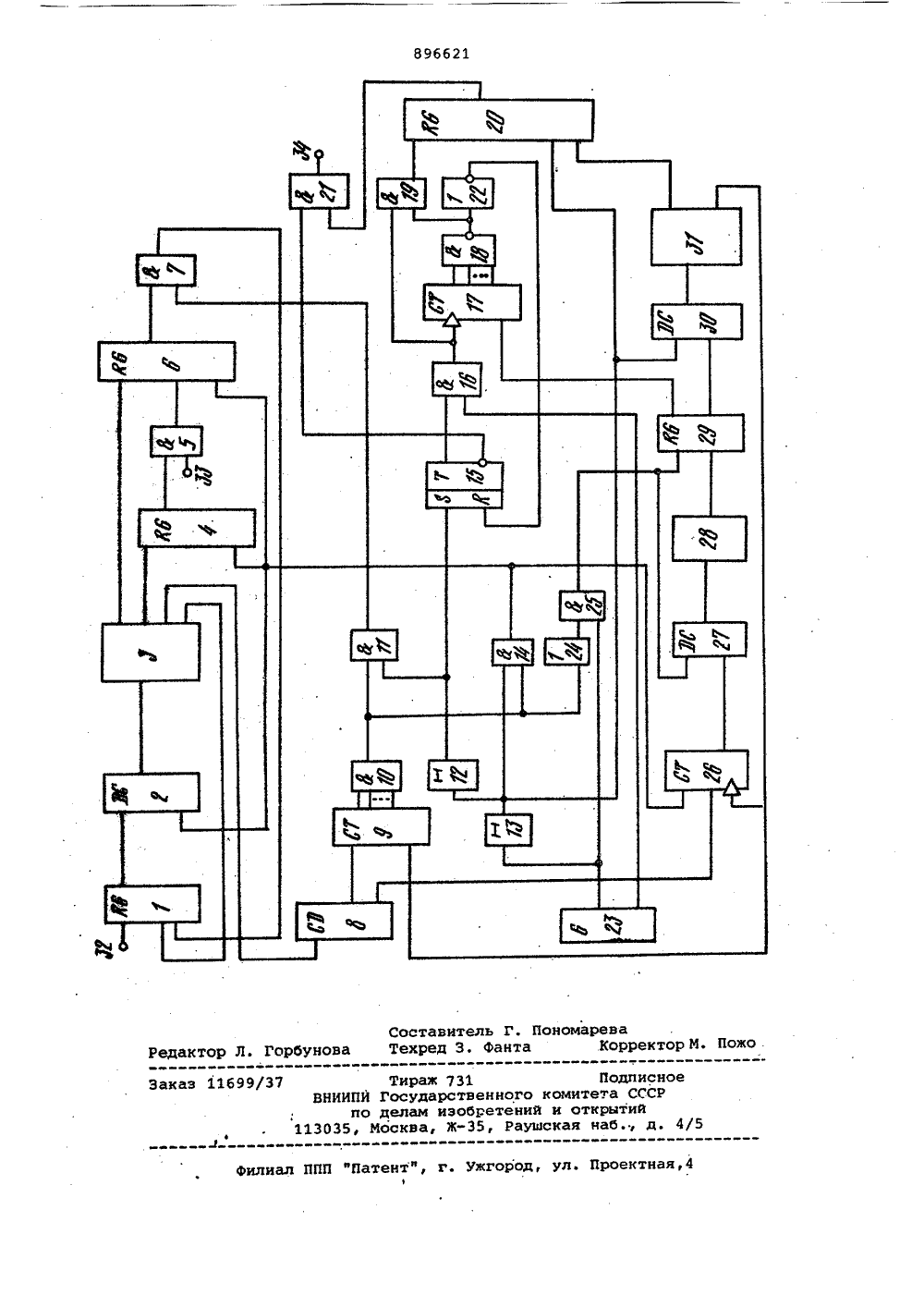

Союз Советскик Соцналистическик Республик(22) Заявлено 28.04.80 (21) 2915890/18-24с присоединением заявки йо(23) ПриоритетОпубликовано 070182 Бюллетень НоДата опубликования описания 07. 01, 82(51)М. КлЗ 6 06 Г 9/22 Государстаеииый комитет СССР по делам изобретеиий и открытий(54) УСТРОЙСТВО МИКРОПРОГРАММНОГО УПРАВЛЕНИЯ Изобретение относится к цифровой вычислительной технике и может быть использовано в качестве микропрограммного устройства управления ЭВМ.Известно устройство микропрограм.много управления, содержащее запоминающие блоки для хранения адресов микрокоманд и их операционных частей, адресный и буферный регистры, регистр логических условий,. дешифраторы,счетчики адресов и микрокоманд, элементы И, НЕ, элементы задержки и генератор тактовых импульсов 1.Недостатком указанного устройства является низкая экономичность,обусловленная избыточностью третьего запоминающего блока, где записаны операционные части всех микрокоманд микропрограммы.Наиболее близким к предлагаемому по технической сущности и достигаемому положительному эффекту является устройство микропрограммного управления, содержащее регистр логических условий, выход которого соединен с первым входом первого блока элементов И, выход которого соединен со входом логических условий буферного регистра, выход которого соединен с первым входом второго блока элемен- З 0 тов И, выход которого соединен с информационным входом первого регистраадреса, вход кода операции которогоявляется входом кода операции устройства, выход первого регистра адреса соединен с информационным входом первого дешифратора, выход которого соединен со входом первого запоминающего блока, первый адресныйвыход первого запоминающего блокасоединен с адресным входом буферногорегистра, второй адресный выход -со входом шифратора, выход логических условий - с информационным входом регистра логических условий, авыход сброса - со входом установкив нуль первого регистра адреса,второй вход первого блока элементов ИсоЕдинен со входом логических условий устройства, второй вход второгоблока элементов И соединен с выходом первого элемента И, первый входкоторого через первый и второй элементы задержки соединен с первымвыходом генератора тактовых импульсов, второй вход первого элемента Исоединен с выходом третьего элемента И, с первым входом четвертогоэлемента И, и через первый элементНЕ с первым входом второго элементаНедостатком укаэанного устройства является его низкая экономичность, обусловленная большой избыточностью третьего запоминающего блока.Цель изобретения - повышение экономичности устройства микропрограммного управления.Укаэанная цель достигается тем, что устройство дополнительно содержит счетчик импульсов,регистр сдвига, элемент И-НЕ и третий блок элементов И,причем информационный вход счетчика импульсов соединен со вторым разрядным выходом регистра адреса, счетный вход счетчика импульсов - с выходом пятого эпемента И ипервым входом шестого элемента И,первый вход пятого элемента И соединен с единичным выходом триггера управления, а второй вход - со вторым выходом генератора тактовых .импульсов, единичный вход триггера управления соединен с выходом второго элемента задержки, а нулевой вход - черезвторой элемент НЕ соединен со вторым входом шестого элемента И и выходом .элемента И-НЕ, группа входов которого соединена с группой выходов счетчика импульсов выход шестого эле" мента И соединен с первым входом регистра сдвига, второй вход которого соединен с выходом первого элемента задержки; третий, вход - с первым выходом третьего запоминающего блока, а выход - с первым входом третьего 35 40 455560 И, второй вход которого соединен спервым входом генератора тактовыхимпульсов, выход второго элемента Исоединен со входом установки в нульвторого регистра адреса и входомзапуска второго дешифратора,группавходов третьего элемента И соединена с группой выходов счетчика микрокоманд, первый вход которого соединен с первым выходом шифратора,второй выход которого соединен с информационным входом счетчика адреса, вход установки в нуль которогосоединен со входами установки в нульрегистра логических условий, буферного регистра, входом запуска первого дешифратора и выходом четвертого элемента И, а выход счетчикаадреса - с информационным входомвторого дешифратора, выход которогосоединен со входом второго запоминающего блока, выход которого сое- щдинен с информационным входом второго регистра адреса, первый разрядный выход которого соединен с инфор"лационным входом третьего дешифратора, вход запуска которого соединен с выходом первого элемента задержки, а выход третьего дешифратора соединен со входом третьего запоминающего блока, первый выход которого соединен со счетным входом счетчика адреса и вторьп, входом счетчикамикрокоманд 2 3. блока элементов И, второй вход которого соединен с нулевым выходом триггера управления, выход третьего блока элементов И является выходом устройства.Предлагаемое устройство обеспечивает повышение экономичности за счет записи в третий запоминающий блок только базовых операционных микрокоманд и формирования полного множества операционных микрокоманд путем циклического сдвига соответствующих базовых операционных микро- команд на заданное количество разрядовеНа чертеже представлена функциональная схема устройства микропрограммного управления.устройство содержит первый регистр 1 адреса, первый дешифратор 2, первый запоминающий блок 3, регистр 4 логических условий, первый блок 5 элементов И, буферный регистр 6, второй блок 7 элементов И, шифратор 8, счетчик 9 микрокоманд, третий элемент И 10, первый элемент И 11, первый элемент 12 задержки, второй элемент 13 задержки, четвертый элемент И 14, триггер 15 управления, пятый элемент И 16, счетчик 17 импульсов, элемент И-НЕ 18, шестой элемент И 19, регистр 20 сдвига, третий блок 21 элементов И, второй элемент НЕ 22, генератор 23 тактовых импульсов, первый элемент НЕ 24, второй элемент И 25, счетчик 26 адреса, второй дешифратор 27, второй запоминающий блок 28, второй регистр 29 адреса, третий дешифратор 30, третий. запоминающий блок 31,вход 32 кода операции, вход 33 логических условий, выход 34 устройства.Считывание операционной микрокоманды с выхода устройства микропрограммного управления осуществляется в два цикла.Первый цикл начинается считыванием информации из первого запоминающего блока 3: выхода кода адреса первой микрокоманды очередной микрокоманды, кода адреса первой микрокоманды текущей последовательности, кода проверяемых логических условий.Заканчивается первый цикл работы считыванием информации из третьего запоминающего блока 31 с первого выхода базовой операционной микрокоманды.В счетчике 9 микрокоманд после считывания адреса первой микрокоманды текущей последовательности записывается код числа микрокоманд,входящих в последовательность. В процессе работы устройства микропрограммного управления нулевое состояние счетчика 9 микрокоманд является признаком выполнения текущей последовательности микрокоманд.Содержание счетчика 9 микрокоманд изменяется в процессе реализации последовательности уменьшением на единицу сигналами со второго выхода третьего запоминающего блока 31 каждый раэ после считывания из него базовой операционной микрокоманды.Считывание .базовых операционных микрокоманд из третьего запоминающего блока 31 осуществляется тактовыми импульсами низкой частоты с первого выхода генератора 23 тактовых импульсов.Счетчик 26 адреса предназначен для 10 Формирования адресов очередных микро- команд путем изменения его содержимого, увеличением на единицу. Формирование адреса очередной микрокоманды происходит всякий раэ после, 15 считывания базовой операционной микрокоманды из третьего запоминающего блока 31.формат микрокоманды второго запоминающего блока 28 разбит на два 20 поля: в первом поле записывается адрес базовой операционной микрокоманды, во втором поле - количество импульсов сдвига, необходимых для Формирования операционной микроко манды.Второй регистр 29 адреса имеет два выхода в соответствии с назначением каждого. поля второго запоминающего блока 28.В третьем запоминающем блоке 31 записываются все базовые операционные микрокоманды, необходимые для Формирования операционных микрокоманд, входящих в.микропрограмму.Считыванием базовой операционной микрокоманды с первого выхода третьего запоминающего блока 31 и записью ее в регистр 20 сдвига заканчивается первый и начинается второй цикл устройства микропрограммного управления. 40В течение второго цикла работы устройства микропрограммного управления происходит уменьшение содержимого счетчика 17 импульсов на единицу по каждому тактовому импульсу высокой частоты со второго выхода генератора 23 тактовых импульсов. В регистре 20 сдвига происходит Формирование операционной микрокоманды.0Нулевое состояние счетчика 17 импульсов является признаком окончания формирования операционной микрокоманды из базовой путем ее циклического сдвига и разрешает считывание сформи- рованной операционной микрокоманды иэ регистра 20 сдвига.Считыванием информации из регистра .20 сдвига управляет триггер 15 управленияУстройство работает следующим об- Щ разом.В исходной состоянии все элементы находятся в нулевом состоянии.Код (номер) операции поступает через вход 32 в регистр 1 адреса и эадает адрес соответствующей ячейкипамяти в первом запоминающем блоке 3.Генератор 23 тактовых импульсовс первого выхода через элемент 13задержки при наличии разрешающегосигнала с выхода третьего элементаИ 10 производит установку и нульсчетчика 26 адреса, буферного регистра и регистра 4 логических условийи осуществляет запуск первого дешифратора 2.По сигналу с первого дешифратора2 иэ соответствующей ячейки памятипервого запоминающего блока 3 происходит считывание кода первой микрокоманды очередной линейной последовательности, кода проверяемых логических условий и кода адреса первоймнкрокоманды текущей линейной последовательности, а также происходитобнуление регистра 1 адреса по сигналу с выхода первого запоминающегоблока 3.Сигнал с выхода генератора 23 тактовых импульсов через элемент 12задержки при наличии разрешающегосигнала с выхода счетчика 9 микрокоманд, соответствующего нулевомуего состоянию, поступает на второйвход второго блока 7 элементов И ипроизводит запись кода номера следующей линейной последовательностив регистр 1 адреса с выхода буферного регистра 6.После считывания адресной части микрокоманды и записи в счетчик 9 микрокоманд кода числа микрокоманд содержимое счетчиха отлично от нуля. Сигнал на выходе третьего элемента И 10 принимает нулевое значение и через первый элемент НЕ 24 открывает второй элемент И 23.Этим же сигналом с выхода элемента 12 задержки происходит установка в "1" триггера 15 управления, который своим единичным выходом открывает пятый элемент И 16.Сигналом с первого выхода генератора 23 тактовых импульсов через открытый второй элемент И 25 происходит обнуление регистра 29 адреса и запуск второго дешифратора 27.По сигналу с выхода второго дешифратора 27 иэ второго запоминающего блока 21 происходит считывание информации из соответствующей ячейки и запись содержимого в регистр 29 адреса.Код номера базовой операционной микрокоманды с первого выхода регистра 29 поступает на первый вход третьего дешифратора 30. Со второго выхода регистра 29 в счетчик 17 импульсов записывается информация о количестве сдвигов, необходимых для формирования соответствующей операционной микрокоманды. При этом содержимое счетчйка 17 отлично от нчля.По сигналу с выхода генератора 23 тактовых импульсов через. элемент 13 задержки происходит запуск третьего дешифратора 30, обнуление регистратора 20 сдвига.Из третьего запоминающего блока 31 по сигналу с выхода третьего дешифратора 30 происходит считывание соответствующей базовой операционной микрокоманды и ее запись в регистр 20 сдвигов.3 ОПосле записи базовой операционной микрокоманды в регистр 20 сдвигов через открытый единичным сигналом с триггера 15 управления пятый элемент И 16 начинается сдвиг базовой операционной микрокоманды в регистре 20 сдвига и уменьшение со. - держимого из счетчика 17 импульсов тактовыми импульсами высокой частоты со второго выхода генератора 23 тактовых импульсов. 2 ОВ течение всего времени сдвигов базовой операционной микрокоманды в регистре 20 сдвига сигнал на выходе элемента.И-НЕ 18 равен единице, и он поддерживает шестой элемент И 19 в открытом состоянии, пропуская импульсы сдвига с выхоца пятого элемента И 16 в регистр 20 сдвига.После того,как в регистре 20 сдви- ЗО га заканчивается процесс формирования операционной микрокоманды, о чем свидетельствует нулевой сигнал на выходе элемента И-НЕ 18, шестой элемент И 19 закрывается, и триггер 15 управления устанавливается в нулевое состояние, При этом единичным сигналом с его нулевого выхода открывается третий блок 21 элементов И.Операционная микрокоманда, записанная в регистре 20 сдвига, поступает на 40 выход 34 устройства.После считывания базовой операционной микрокоманды из третьего запоминающего блока 31 содержимое счетчика 26 адреса увеличивается на 45 единицу, тем самым формируется адрес очередной микрокоманды последовательности, а содержимое счетчика 9 микрокоманд уменьшается на единицу.Очередным тактовым импульсом с выхода генератора 23 через открытый второй элемент И 25 происходит запуск третьего дешифратора 30 и обнуление регистра 20 сдвига. В дальнейшем работа устройства микропрог" раммного управления повторяется.После считывания последней микро- .команды текущей последовательности происходит обнуление счетчика 9 микрокоманд, на выходе третьего элемента И 10 появляется единичный сиг- бо нал, который закрывает второй элемент И 25 и открывает четвертый 1.4 и первый 11 элементы И.По сигналу с выхода элемента 13 задержки тактовый импульс с первого 65 выхода генератора 23 тактовых импульсов происходит обнуление регистра 4 логических условий и буферного регистра 6, счетчика 26 адреса и запуск первого дешифратора 2.Таким образом, введение указанных элементов и связей позволяет существенно повысить экономичность.При этом сохраняются неизменными другие характеристики, такие как функциональные воэможности и быстродействие, поскольку операции сдвига осуществляются частотой, значительно превышающей частоту считывания информации из запоминающих блоков.Формула изобретенияУстройство микропрограммного управления, содержащее регистр логических условий, выход которого соединен с первым входом первого блока элементов И, выход которого соединен со входом логических условий буферного регистра, выход которого соединен с первым входом. второго блока элементов И, выход которого соединен с информационным входом первого регистра адреса, вход кода операции которого является входом кода операции устройства, выход первого регистра адреса соединен с информационным входом первого дешифратора, выход которого соединен со входом первого запоминающего блоке, первый адресный выходпервого запоминающего блока соединен с адресным входом буферного регистра, второй адресный выход - со входом шифратора, выход логических условий с информационным входом регистра логических условий, а выход сбросасо входом установки в нуль первого регистра адреса, второй вход первого блока элементов И соединен со входом логических условий устройства, второй вход второго блока элементов И соединен с выходом первого элемента И, первый вход которого через первый и второй элементы задержки соединен с первым выходом генератора тактовых импульсов, второй вход первого элемента И соединен с выходом третьего элемента И, с первым входом четвертого элемента И, и через первый элемент НЕ с первым входом второго элемента И, второй вход которого соединен с первым входом генератора тактовых импульсов, выход второго элемента И соединен со входом установки в нуль второго регистра адреса и входом запуска второго дешифратора,группа входов третьего элемента И соединена с группой выходов счетчика микро- команд, первый вход которого соединен с первым выходом шифратора, второй выходкоторого соединен с информационным входом счетчика адреса, вход установки в нуль которого соединен совходами установки в нуль регистра логических условий, буферного регистра,входом запуска первого дешифратора ивыходом четвертого элемента И, а выход счетчика адреса - с информационным входом второго дешифратора,выходкоторого соединен со входом второгозапоминающего блока, выход которогосоединен с информационным входомвторого регистра адреса, первый разрядный выход которого соединен с ин-формационным входом третьего дешифратора, вход запуска которого соединенс выходом первого элемента задержки,а выход третьего дешифратора соединен со входом третьего запоминающегоблока, первый выход которого соединен со счетным входом счетчика адреса и вторым входом счетчика микрокоманд, о т л и ч а ю щ е е ся тем,что, с целью повышения экономичности,оно дополнительно содержит счетчик 20импульсов, регистр сдвига, элементИ-НЕ и третий блок элементов И,при"чем информационный вход счетчикаимпулвсов соединен со вторым разрядным выходом регистра адреса, счетный вход счетчика импульсов - с вы"ходом пятого элемента И и первымвходом шестого элемента И, первый вход пятого элемента И соединен сединичным выходом триггера управления, а второй вход. - со вторым выходом генератора тактовых импульсов,единичный вход триггера управлениясоединен с выходом второго элементазадержки, а нулевой вход - через второй элемент НЕ соединен со вторымвходом шестого элемента И и выходомэлемента И-НЕ, группа входоз которого соединена с группой выходов счетчика импульсов, выход шестого элемента И соединен с первым входом регистра сдвига, второй вход которогосоединен с выходом первого элементазадержки, третий вход - с первым выходом третьего запоминающего блока,а выход - с первым входом третьегоблока элементов И, второй вход которого соединен с нулевым выходом триггера управления, выход третьего блока элемента И является выходом устройства.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРР 763898 кл С 069/16 19782. Авторское свидетельство СССРпо заявке Р 2802977/18-24,кл. С 06 Г 9/16, 1979 (прототип).896621 Состави Техред 3 мареваКорр ь Г. фант ар М, Пожо. Редан Го Тираж 731 ПоддисноВНИИПИ Государственного комитета СССРпо делам изобретений и открытий3035, Москва, Ж, Раушская наб.; д аказ 1169 4/5 филиал ППП фОатент", г. Ужгород, ул. Проектна1

СмотретьЗаявка

2915890, 28.04.1980

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНОЕ УЧИЛИЩЕ

ХАРЧЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ТИМОНЬКИН ГРИГОРИЙ НИКОЛАЕВИЧ, БАРБАШ ИВАН ПАНКРАТОВИЧ, ТКАЧЕНКО СЕРГЕЙ НИКОЛАЕВИЧ, САМАРСКИЙ ВИКТОР БОРИСОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 07.01.1982

Код ссылки

<a href="https://patents.su/6-896621-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Устройство для умножения по модулю

Следующий патент: Устройство микропрограммного управления

Случайный патент: Поточная линия для обработки текстильного полотна