Устройство для умножения десятич-ных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

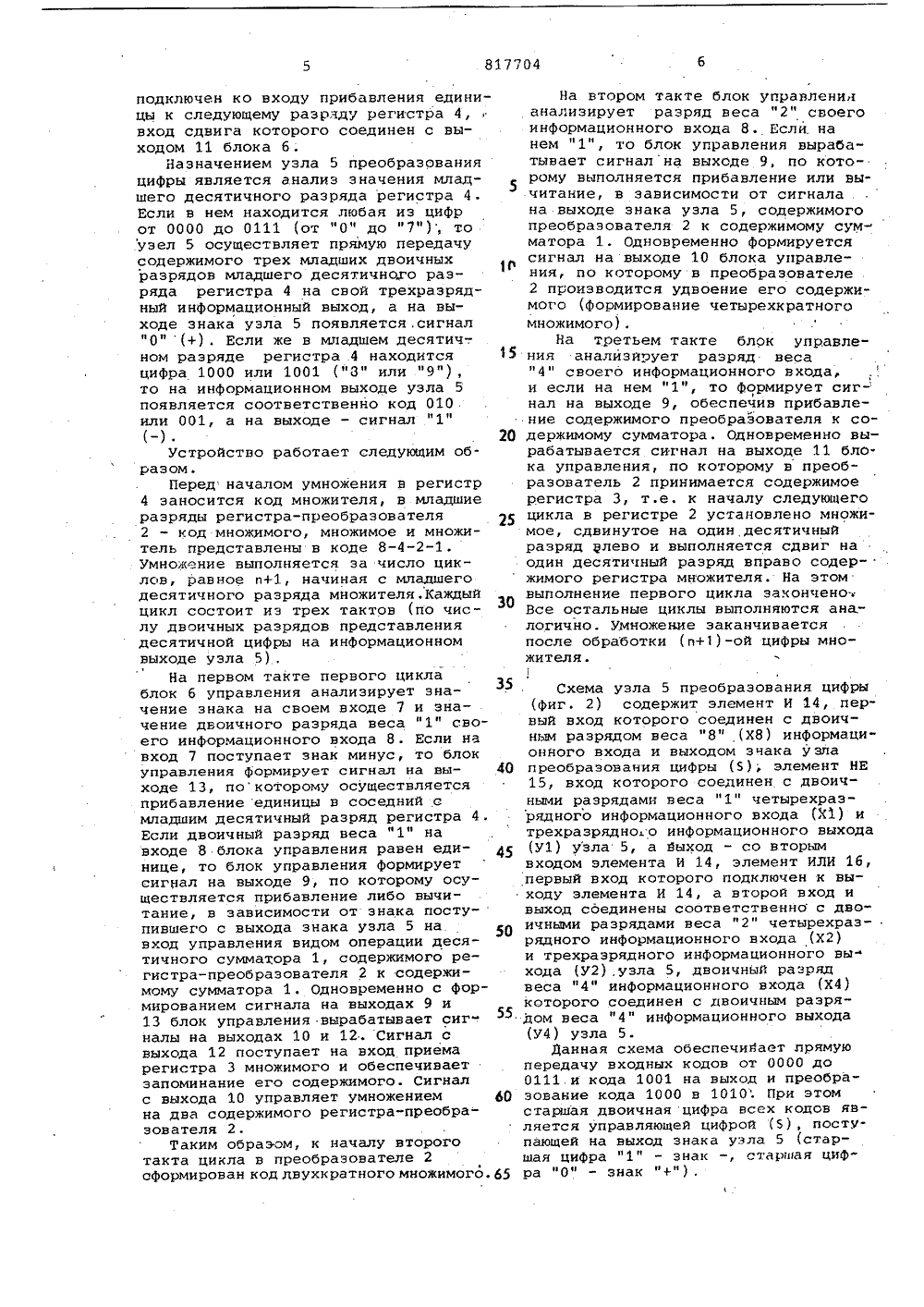

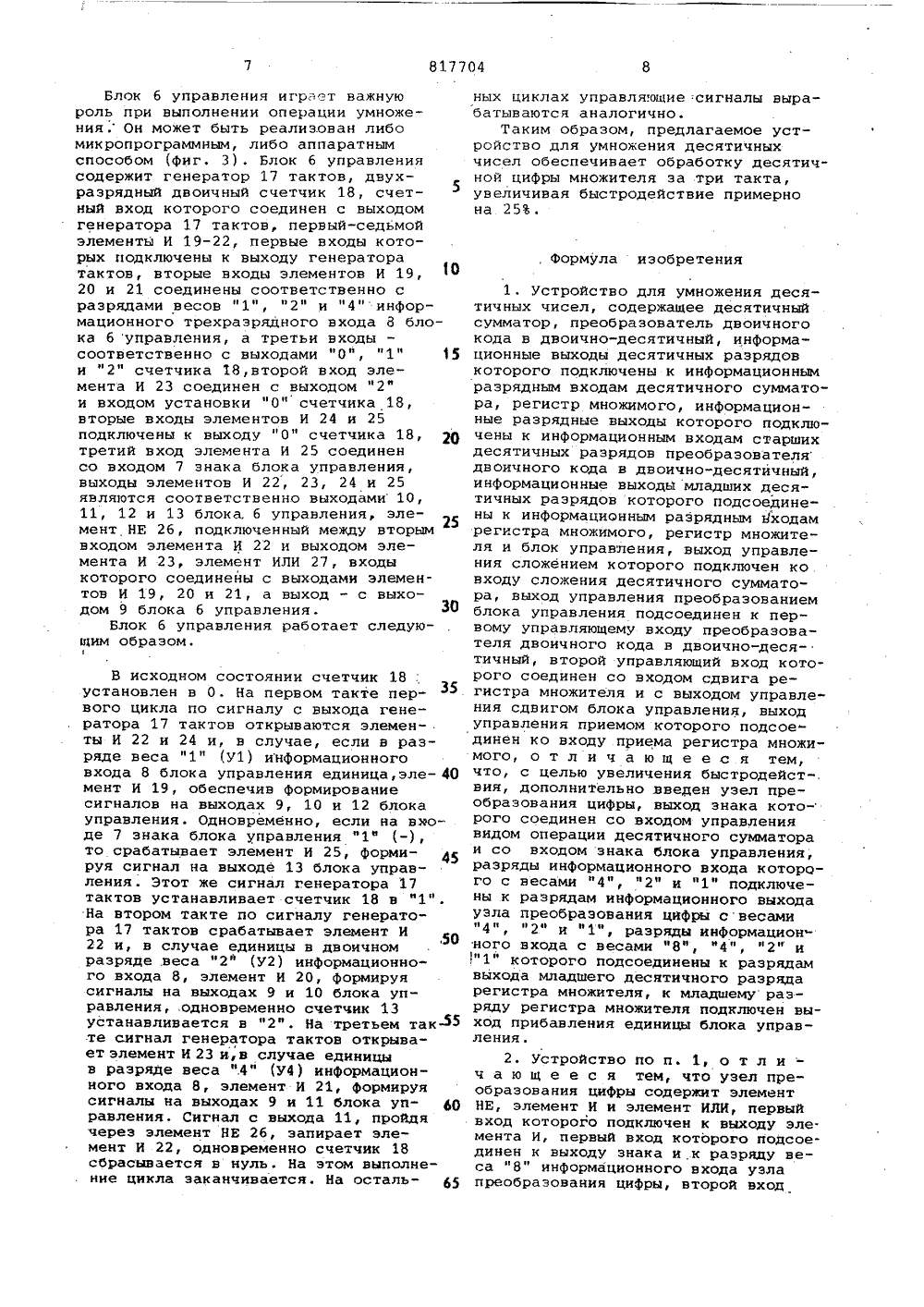

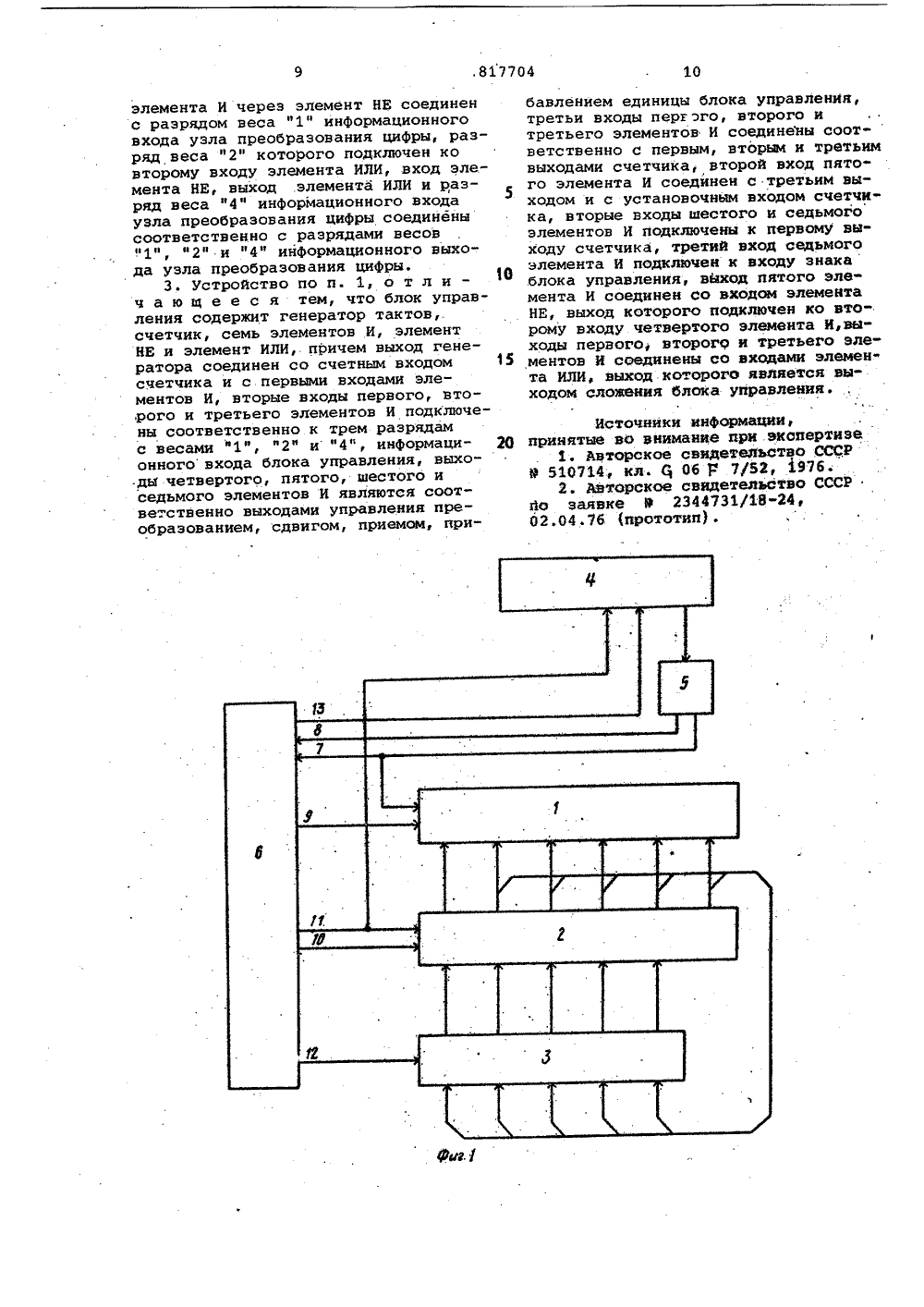

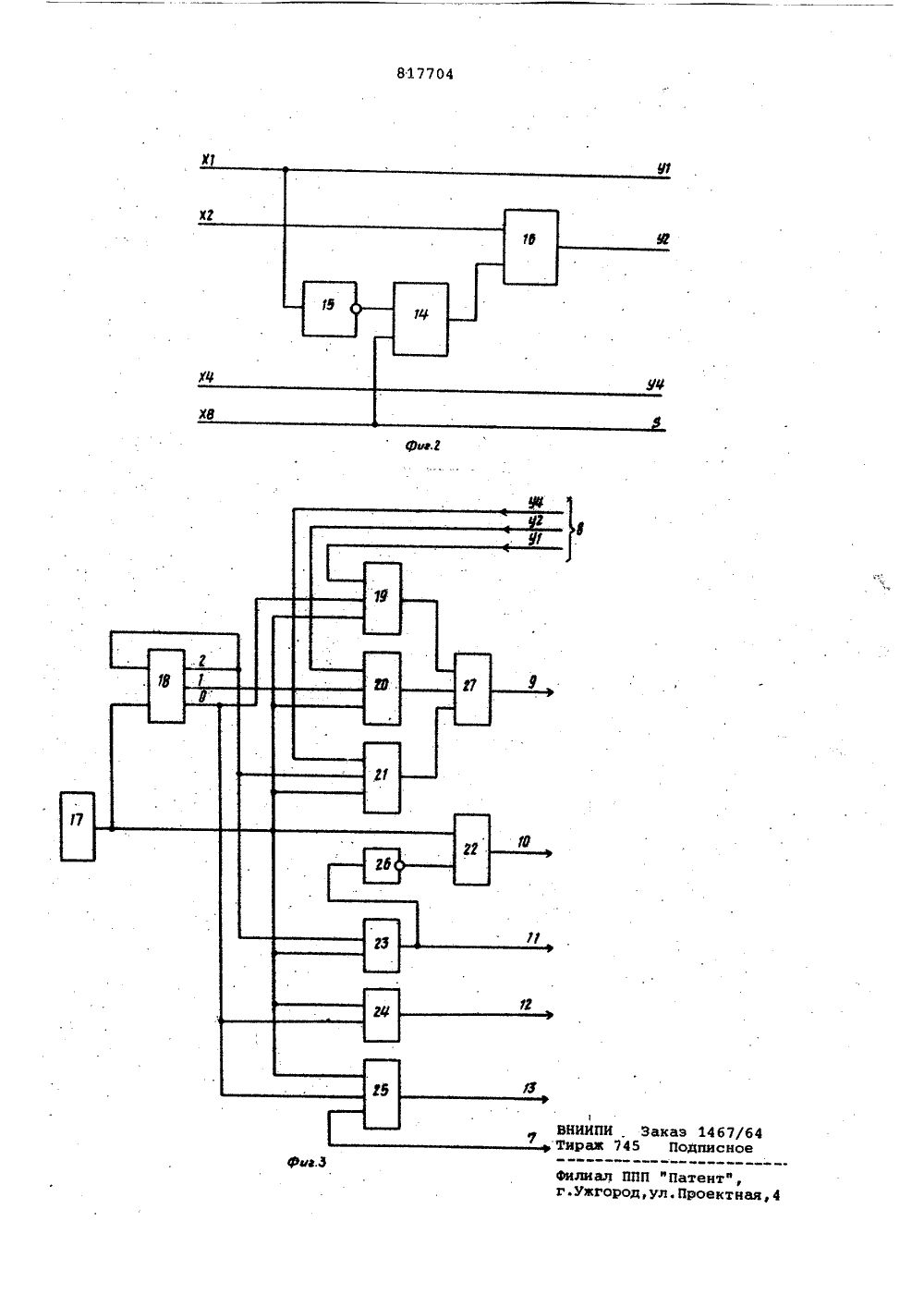

ОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИ ЕТВЛЬСТВУ Союз СоветскикСоциалистическихРеспублик н 1) 817704 Фс,(61) Дополнительное к авт. свид-ву(23) Приоритет Государственный коинтет СССР по делам нзобретеннй н открытнйДата опубликования описания 300381 .т(71) Заявитель Минский радиотехнический инсгитут(54) УСТРОЙСТВО ЦЛЯ УМНОЖЕНИЯ ДЕСЯТИЧНЦХ ЧИСЕЛ Изобретение относится к вычислительной технике и может быть использовано при построении двоично-десятичных арифметических устройств5Известно устройство умножения, содержащее регистр множимого, блок последовательного накопления чисел, кратных множимому, блок сдвига, блок суммирования частичных произведений, регистр множителя, блок определения цифр 1) .Однако известное устройство слож-. но.Наиболее близким к предлагаемому является устройство, содержащее десятичный сумматор, регистр-преобразователь, информационные разрядные выходы которого подключены к информационным входам сумматора, регистр множимого, информационные выходы которого подключены к информационным входам старших десятичных разрядов регистра-преобразователя, информационные выходы младших десятичных разрядов которого подключены к информационным входам регистра множимого, регистр множителя и блок управления, выход сложения которого подключен ко входу сложения десятичного сумматора, выход преобразования блока управ- ЗО ления подсоединен к первому управляю"щему входу регистра-преобразователя,второй управляющий вход которого сое-динен со входом сдвига регистра множителя и с выходом управления сдвигом блока управления, выход управления приемом которого подсоединен ковходу приема в регистр множимого21 .Недостаток данного устройства "большое время выполнения операции(каждая десятичная цифра множителяобрабатывается за четыре такта).Цель изобретения - увеличениебыстродействия устройства,Поставленная цель достигается тем)что в устройство для умножения десятичных чисел, содержащее десятичныйсумматор, преобразователь двоичногокода в двоично-десятичный, информационные выходы десятичных разрядовкоторого подключены к информационным разрядным входам десятичного сумматора, регистр множимого, информационные разрядные выходы которогоподключены к информационным входамстарших десятичных разрядов преобразователя двоичного кода в двоичнодесятичный, информационные выходымладших десятичных разрядов которогоподсоединены к информационным разрядным входам множимого, регистр множителя и блок управления, выход управ.ения сложением которого подключен ко нходу сложения десятичного сумматора, выход управления преобразованием блока управления подсое 5 динен к первому управляющему входу преобразователя двоичного кода в . двоично-десятичный, второй управляющий вход которого соединен со входом сдвига регистра множителя и с выходом управления сдвигом блока управления, выход управления приемом которого подсоединен ко входу приема регистра множимого, дополнительно введен узел преобразования цифры, 15 выход знака которого соединен с входом упРавления видом операции десятичного сумматора и со входом знака блока управления, разряды информационного входа которого с весами 20 "4", "2" и "1" подключены к разрядам информационного выхода узла преобразования цифры с весами "4", "2" и "1", разряды информационного входа с весами "8", "4", "2" и "1" которого подсоединены к разрядам выхода младшего десятичного разряда регистра множителя, к младшему разряду регистра множителя подключен выход прибавления единицы блока управления, Узел преобразования цифры содержит элемент НЕ, элемент И и элемент ИЛИ, первый вход которого подключен к выходу элемента И, первый вход которого подсоединен к выходу знака и к разряду веса "8" информационного входа узла преобразования цифры,второй вход элемента И через, элемент НЕ соединен с разрядом веса "1" информационного входа узла преобразования цифры, разряд веса "2" которого 40 подключен ко второму входу элемента ИЛИ, вход элемента НЕ, выход элемента ИЛИ и разряд веса "4" информационного входа узла преобразования цифры соединены соответственно с разрядами весов "1", "2" и "4" информационного выхода узла преобразования цифры. Кроме того, блок управления.содержит генератор тактов, счетчик, семь элементов И, элемент НЕ и элемент ИЛИ, причем выход генератора соединен со счетным входом счетчика и с первыми входами элементов И, вторые входы первого, второго и третьего элементов И подключенысоответственно к. трем разрядам с55весами "1", "2", "4" информационного входа блока управления, выходычетвертого, пятого, шестого и седьмого элементов И являются соответственно выходами управления преобразованием, сдвигогл, приемом, прибавлением единицы блока управления,третьи входы первого, второго итретьего элементов И соединены соответстненно с первым, вторым и третьим б 5 выходами счетчика, второй нход пятого элемента И соединен с третьим выходом и с установочным входом счетчика, вторые входы шестого и седьмого элементов И подключены к первому выходу счетчика, третий вход седьмого элемента И подключен к входу знака блока управления, выход пятого элемента И соединен со входом элемента НЕ, выход которого подключен ко второму входу четвертого элемента И, выходы первого, второго и третьего элементов И соединены со входами элемента ИЛИ, выход которого является выходом сложения блока управления.На фиг. 1 представлена структурная схема устройстна для умножения десятичных чисел", на фиг. 2 - схема узла преобразования цифры, на фиг,3- схем блока управления.Устройство (фиг. 1) содержит десятичный сумматор 1, содержащий 2 п десятичных разрядов, где и разрядность десятичных операндов, преобразователь 2, содержащий 2 и десятичных разрядов, информационные выходы которого подключены к информационным входам сумматора, данный блок представляет собой регистр сдвига с цепями коррекции, необходимыми для умножения десятичного числа на дна, и служит для последовательного получения во время выполнения умножения необходимых кратных мйожимого, н качестве преобразователя может быть использован преобразователь двоичного кода н дноично-десятичный, регистр 3 множимого, содержащий 2 идесятичных разрядов, входы которого подключены к выходам младших разрядон регистра-преобразователя, а выходы - ко входам старших разрядов его регистр 4 множителя, содержащий и+1 десятичный разряд, причем старшие и выполнены н виде десятичных. счетчиков, узел 5 преобразования цифры, четырехразрядный инфорглационный вход которого подключен к выходу младшего десятичного разряда регист; ра 4, а выход знака - ко входу управления видом операции десятичного сумматора, блок б управления, вход 7 знака которого соединен с выходом знака узла 5, трехразрядный информационный выход которого соединен с трехразрядным информационным входом 8 блока б, выход 9 управления сложением, которого подключен ко входу сложения сумматора 1, выход 10 .преобразования блока управления соединен с первым управляющим входом преобразователя 2, второй управляющийвход которого подсоединен к выходу11 управления сдвигом блока управления, выход 12 управления, приемомкоторого соединен со входом приемарегистра 3, выход 13 улранления прибавлением единицы блока управленияподключен ко входу прибавления единицы к следующему разряду регистра 4,вход сдвига которого соединен с выходом 11 блока 6.Назначением узла 5 преобразованияцифры является анализ значения младшего десятичного разряда регистра 4.Если в нем находится любая иэ цифрот 0000 до 0111 (от "0" до "7"), тоузел 5 осуществляет прямую передачусодержимого трех младших двоичныхразрядов младшего десятичного разряда регистра 4 на свой трехразрядный информационный выход, а на выходе знака узла 5 появляется, сигнал"0" (+). Если же в младшем десятич-.ном разряде регистра 4 находитсяцифра 1000 или 1001 ("3" или ф 9"),то на информационном выходе узла 5появляется соответственно код 010или 001, а на выходе - сигнал "1"(-)Устройство работает следующим образом.Перед началом умножения в регистр4 заносится код множителя, в младшиеразряды регистра-преобразователя2 - код множимого, множимое и множитель представлены в коде 8-4-2-1.Умножение выполняется за число циклсв, равное и+1, начиная с младшегодесятичного разряда множителя, Каждыйцикл состоит из трех тактов (по числу двоичных разрядов представлениядесятичной цифры на информационномвыходе узла 5),На первом такте первого циклаблок 6 управления анализирует значение знака на своем входе 7 и значение двоичного разряда веса "1" своего информационного входа 8. Если навход 7 поступает знак минус, то блокуправления формирует сигнал на выходе 13, покоторому осуществляетсяприбавление единицы в соседний смладшим десятичный разряд регистра 4,Если двоичный разряд веса "1" навходе 8 блока управления равен единице, то блок управления Формируетсигнал на выходе 9, по которому осуществляется прибавление либо вычитание, в зависимости от знака поступившего с выхода знака узла 5 навход управления видом операции десятичного сумматора 1, содержимого регистра-преобразователя 2 к содержимому сумматора 1. Одновременно с Формированием сигнала на выходах 9 и13 блок управления вырабатывает сигналы на выходах 10 и 12. Сигнал свыхода 12 поступает на вход приемарегистра 3 множимого и обеспечиваетзапоминание его содержимого. Сигналс выхода 10 управляет умножениемна два содержимого регистра-преобразователя 2.Таким образом, к началу второготакта цикла в преобразователе 2сформирован код двухкратного множимого. 6 На втором такте блок управленияанализирует разряд веса "2" своегоинформационного входа 8. Если, нанем "1", то блок управления выраба"тывает сигнална выходе 9, по которому выполняется прибавление или вычитание, в зависимости от сигналана выходе знака узла 5, содержимогопреобразователя 2 к содержимому сумматора 1. Одновременно Формируетсясигнал на выходе 10 блока управления, по которому в преобразователе2 производится удвоение его содержимого (Формирование четырехкратногомножимого).На третьем такте блок управле 15 ния анализирует разряд веса"4" своего информационного входа,и если на нем "1", то формирует сиг-нал на выходе 9, обеспечив прибавление содержимого преобразователя к со 20 держимому сумматора. Одновременно вырабатывается сигнал на выходе 11 бло"ка управления, по которому в преобразователь 2 принимается содержимоерегистра 3, т.е. к началу следующего25 цикла в регистре 2 установлено множимое, сдвинутое на один десятичныйразряд влево и выполняется сдвиг наодин десятичный разряд вправо содер- .жимого регистра множителя. На этомвыполнение первого цикла закончено-Все остальные циклы выполняются ана. -логично. Умножение заканчиваетсяпосле обработки (и+1)-ой цифры множителя.ЪСхема узла 5 преобразования цифры(фиг. 2) содержит элемент И 14, пер"вый вход которого соединен с двоичным разрядом веса "8" (Х 8) информационного входа и выходом зчака узла40 преобразования цифры (5), элемент НЕ15, вход которого соединен с двоичными разрядами веса "1" четырехразрядного информационного входа (Х 1) итрехразрядно.о информационного выхода45 (У 1) узла 5, а выход - со вторымвходом элемента И 14, элемент ИЛИ 16,первый вход которого подключен к выходу элемента И 14, а второй вход ивыход соединены соответственно с дво 50ичными разрядами веса "2" четырехразрядного информационного входа (Х 2)и трехразрядного информационного вы"хода (У 2),узла 5, двоичный разрядвеса "4" информационного входа (Х 4)которого соединен с двоичным разря 55 дом веса "4" информационного выхода(У 4) узла 5.Данная схема обеспечивает лрямуюпередачу входных кодов от 0000 до0111.и кода 1001 на выход и преобраб 0 зование кода 1000 в 1010. При этомстаршая двоичная цифра всех кодов является управляющей цифрой (5), поступающей на выход знака узла 5 (старшая цифра "1" - знак в , старшая циф"5 ра "0" - знак "+"),Блок б управления играет важную роль при ныполнении операции умножения, Он может быть реализован либо микропрограммным, либо аппаратным способом (фиг. 3), Блок 6 управления содержит генератор 17 тактов, двух- разрядный двоичный счетчик 18, счетный вход которого соединен с выходом генератора 17 тактов, первый-седьмой элементы И 19-22, первые входы которых подключены к выходу генератора тактов, вторые входы элементов И 19, 20 и 21 соединены соответственно с разрядами весов "1", "2" и "4" информационного трехразрядного входа 8 блока б управления, а третьи входы соответственно с выходами "0", "1" 15 и "2" счетчика 18,второй вход элемента И 23 соединен с выходом "2" и входом установки "0" счетчика 18, вторые входы элементов И 24 и 25 подключены к выходу "0" счетчика 18, 20 третий вход элемента И 25 соединен со входом 7 знака блока управления, выходы элементов И 22, 23, 24 и 25 являются соответственна выходами 10, 11, 12 и 13 блока, б управления, элемент НЕ 26, подключенный между вторым входом элемента И 22 и выходом элемента И 23, элемент ИЛИ 27, входы которого соединены с выходами элементов И 19, 20 и 21, а выход - с выходом 9 блока 6 управления. 30Блок б упранления работает следующим образом.В исходном состоянии счетчик 18установлен в О. На первом такте первого цикла по сигналу с выхода генератора 17 тактов открываются элементы И 22 и 24 и, в случае, если в разряде веса "1" (У 1) информационного входа 8 блока управления единица,эле мент И 19, обеспечин формирование сигналов на выходах 9, 10 и 12 блока управления. Одновременно, если на входе 7 знака блока управления "1 ф (-), то срабатывает элемент И 25, форми руя сигнал на выходе 13 блока управления . Этот же сигнал генератора 17 тактов устанавливает счетчик 18 н "1".На втором такте по сигналу генератора 17 тактов срабатывает элемент И 0 22 и, в случае единицы в двоичном разряде .веса "2" (У 2) информационного входа 8, элемент И 20, формируя сигналы на выходах 9 и 10 блока управления, одновременно счетчик 13 устанавливается в 12 ф. На третьем такте сигнал генератора тактов открывает элемент И 23 и,в случае единицы в разряде веса ".4" (у 4) информационного входа 8, элемент И 21, формируя сигналы на выходах 9 и 11 блока уп- щ равления, Сигнал с выхода 11, пройдя через элемент НЕ 26, запирает элемент И 22, одновременно счетчик 18 сбрасывается в нуль. На этом выполнение цикла заканчивается. На осталь- д ных циклах упранля.ощие:сигналы вырабатываются аналогично.Таким образом, предлагаемое устройство для умножения десятичныхчисел обеспечивает обработку десятичной цифры множителя за три такта,увеличивая быстродействие примернона 25.Формула изобретения1, Устройство для умножения десятичных чисел, содержащее десятичный сумматор, преобразователь двоичного кода в двоично-десятичный, информационные выходы десятичных разрядовкоторого подключены к информационнымразрядным входам десятичного сумматора, регистр множимого, информационные разрядные выходы которого подключены к информационным входам старшихдесятичных разрядов преобразователя двоичного кода в двоично-десятичный, информационные выходЫ младших десятичных разрядов которого подсоединены к информационным разрядным входамрегистра множимого, регистр множителя и блок управления, выход управления сложением которого подключен ко входу сложения десятичного сумматора, выход управления преобразованиемблока управления подсоединен к первому управляющему входу преобразователя двоичного кода н двоично-десятичный, второй управляющий вход которого соединен со входом сдвига регистра множителя и с выходом управления сдвигом блока управления, выход управления приемом которого подсоединен ко входу приема регистра множимого, о т л и ч а ю щ е е с я тем, что, с целью увеличения быстродейст-. вия, дополнительно введен узел преобразования цифры, выход знака кото- рого соединен со входом управления видом операции десятичного сумматора и со входом знака блока управления, разряды информационного входа которого с весами 4 ф, "2" и 11 ф подключены к разрядам информационного выхода узла преобразования цифры с весами "4", "2" и ф 1", разряды информационного входа с весами ф 8", 14", ф 2 ф и "1" которого подсоединены к разрядам выхода младшего десятичного разряда регистра множителя, к младшему разряду регистра множителя подключен выход прибавления единицы блока управления.2. Устройство по п. 1, о т л и ч а ю щ е е с я тем, что узел преобразования цифры содержит элемент НЕ, элемент И и элемент ИЛИ, первый вход которого подключен к выходу эле.мента И, первый вход которого подсоединен к выходу знака и к разряду веса "8" информационного входа узла преобразования цифры, второй входэлемента И через элемент НЕ соединен с разрядом веса "1" информационного входа узла преобразования цифры, разряд веса "2" которого подключен ко второму входу элемента ИЛИ, вход элемента НЕ, выход элемента ЙЛИ и разряд веса ф 4" информационного входа узла преобразования цифры соединены соответственно с разрядами весов "1 ф, ф 2 ф и ф 4 ф информационного выхода узла преобразования цифры.3. Устройство по и. 1, о т л и - ч а ю ш е е с я тем, что блок управления содержит генератор тактов, счетчик, семь элементов И, элемент НЕ и элемент ИЛИ,.причем выход генератора соединен со счетным входом 15 счетчика и с первыми входами элементов И, вторые входы первого, второго и третьего элементов И подключены соответственно к трем разрядам с весами ф 1 ф, "2 ф иф 4", информаци онного входа блока управления, выходы четвертого, пятого, шестого и седьмого элементов И являются соответственно выходами управления преобразованием, сдвигом, приемом, прибавлением единицы блока управления,третьи входы пергэго, второго итретьего элементов И соединены соответственно с первым, вторьм и третьимвыходами счетчика, второй вход пятого элемента И соединен с третьим выходом и с установочным входом счетчика, вторые входы шестого и седьмогоэлементов И подключены к первому выходу счетчика, третий вход седьмогоэлемента И подключен к входу знакаблока управления, вйход пятого элемента И соединен Со входом элементаНЕ, выход которого подключен ко второму входу четвертого элемента И,выходю первого, второго и третьего элементов И соединены со входами элемен"та ИЛИ, выход которого является выходом сложения блока управления,Источники информациипринятые во внимание при экспертизе1, Авторское свидетельство СССРВ 510714, кл. С О 6 Р 7/Ьйт 976.2. Авторское свидетельство СССРйо заявке В 2344731/18-24,О 2.04,76 (прототип).ИПИ, Заказ 1467/баж 745 Подписное филиал ППП ффПатентф,г.Ужгород,ул.Проектная,4

СмотретьЗаявка

2764246, 11.05.1979

МИНСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ

ГЛУХОВА ЛИЛИЯ АЛЕКСАНДРОВНА, ПЕШКОВ АНАТОЛИЙ ТИМОФЕЕВИЧ

МПК / Метки

МПК: G06F 7/52

Метки: десятич-ных, умножения, чисел

Опубликовано: 30.03.1981

Код ссылки

<a href="https://patents.su/6-817704-ustrojjstvo-dlya-umnozheniya-desyatich-nykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения десятич-ных чисел</a>

Предыдущий патент: Устройство для умножения и деленияпоследовательно параллельногодействия

Следующий патент: Множительное устройство

Случайный патент: Пресс для непрерывного изготовления древесностружечных плит