Устройство для моделирования сетевых графиков

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 636635

Авторы: Голованова, Додонов, Ралдугин, Федотов, Хаджинов

Текст

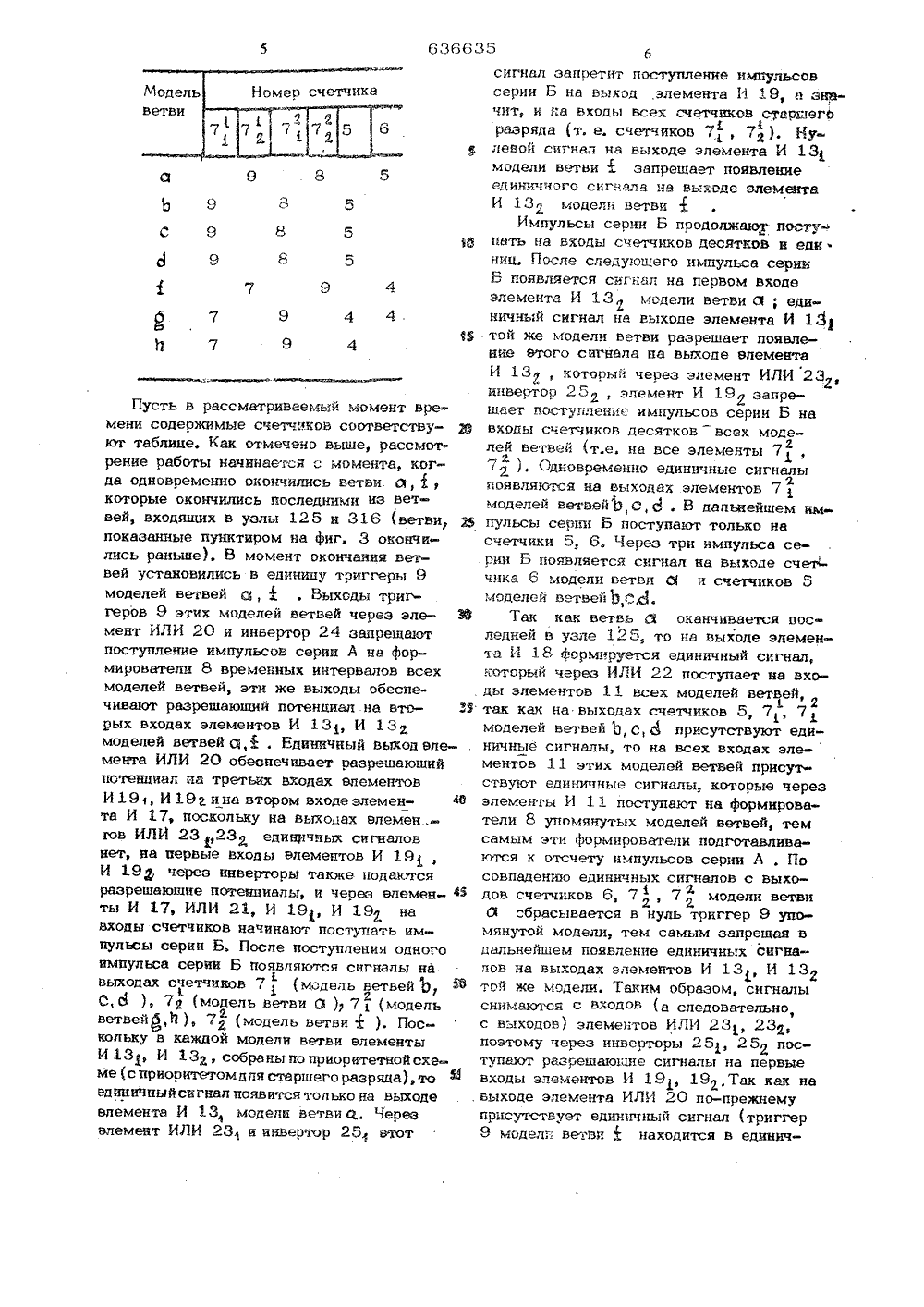

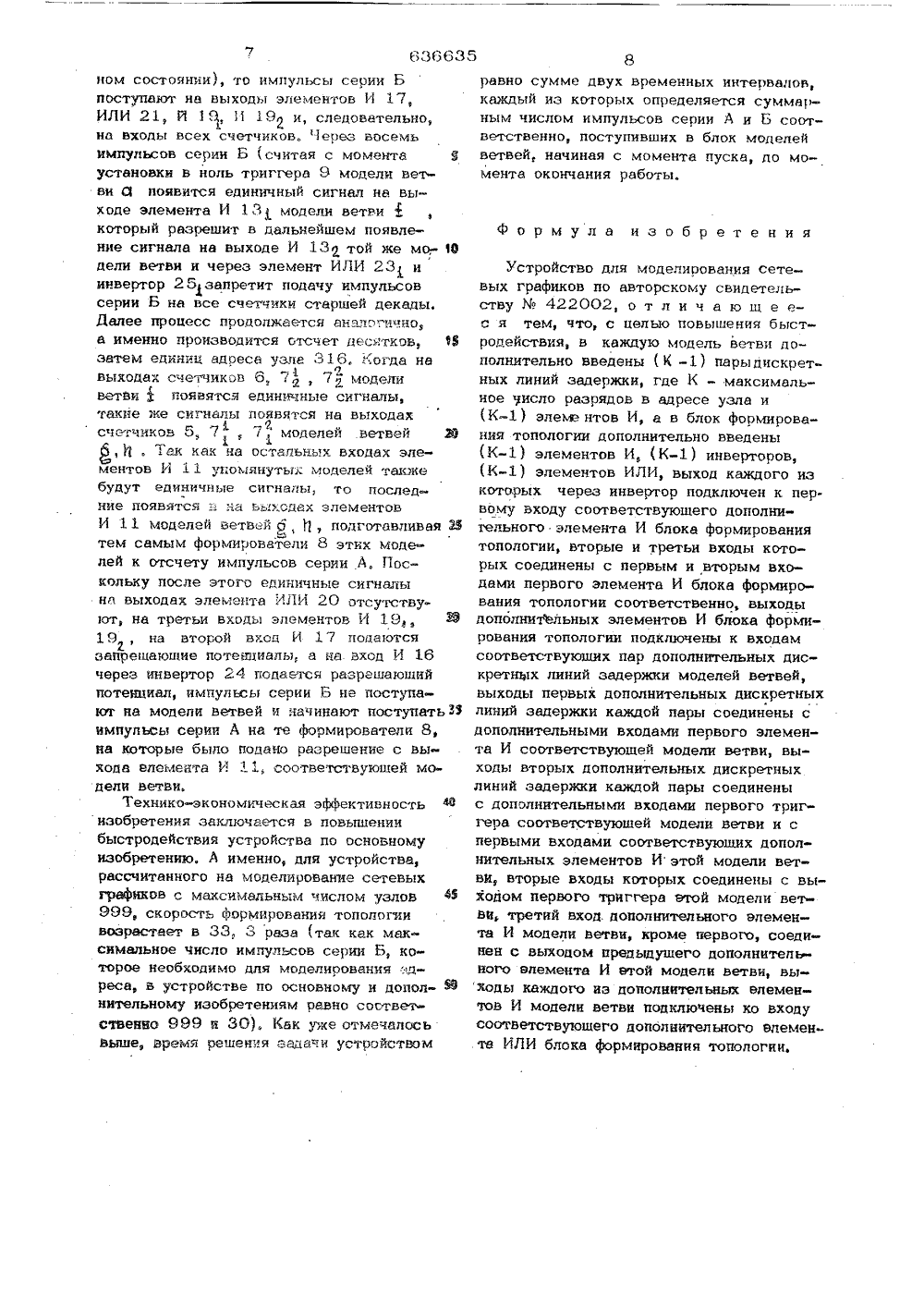

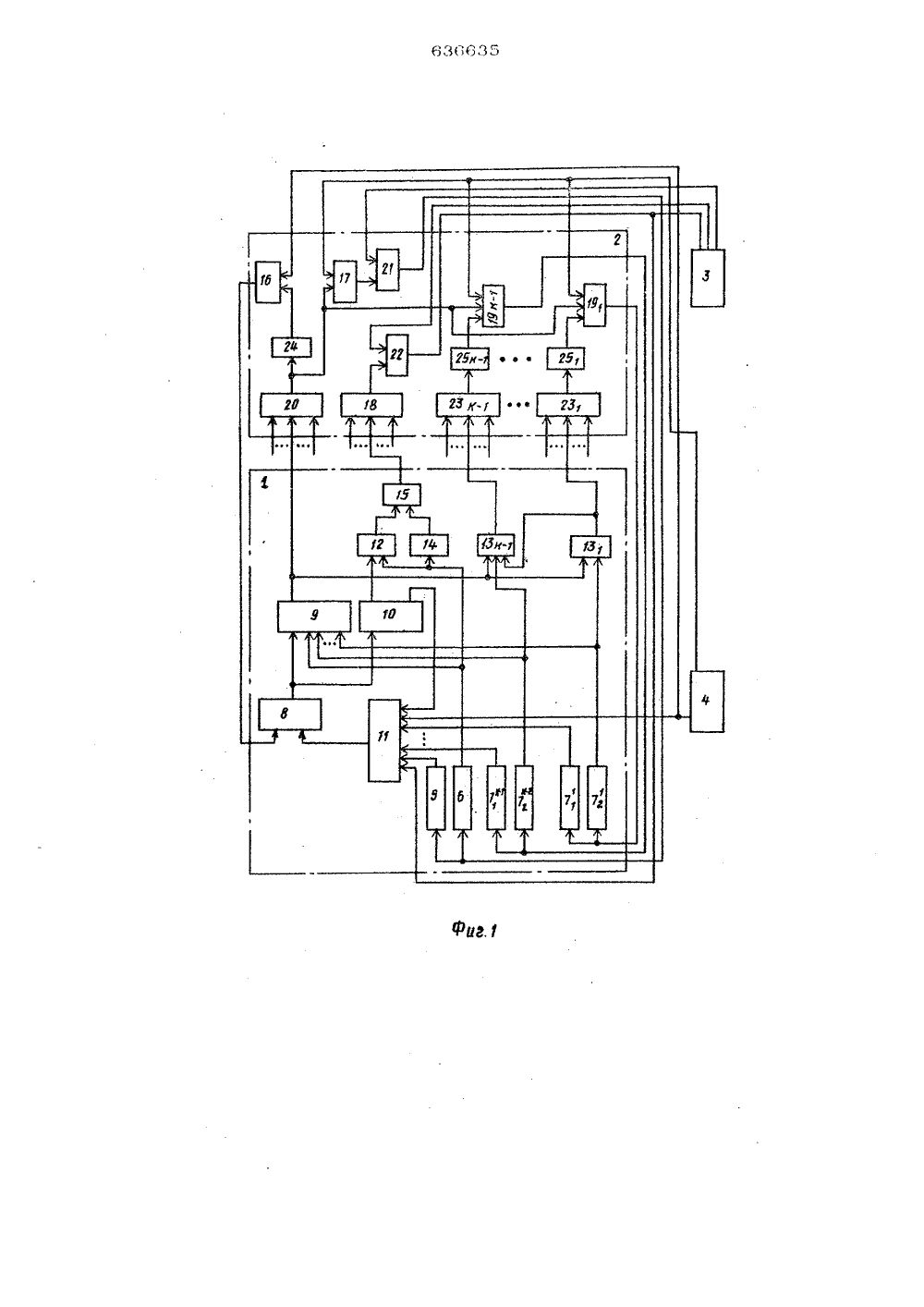

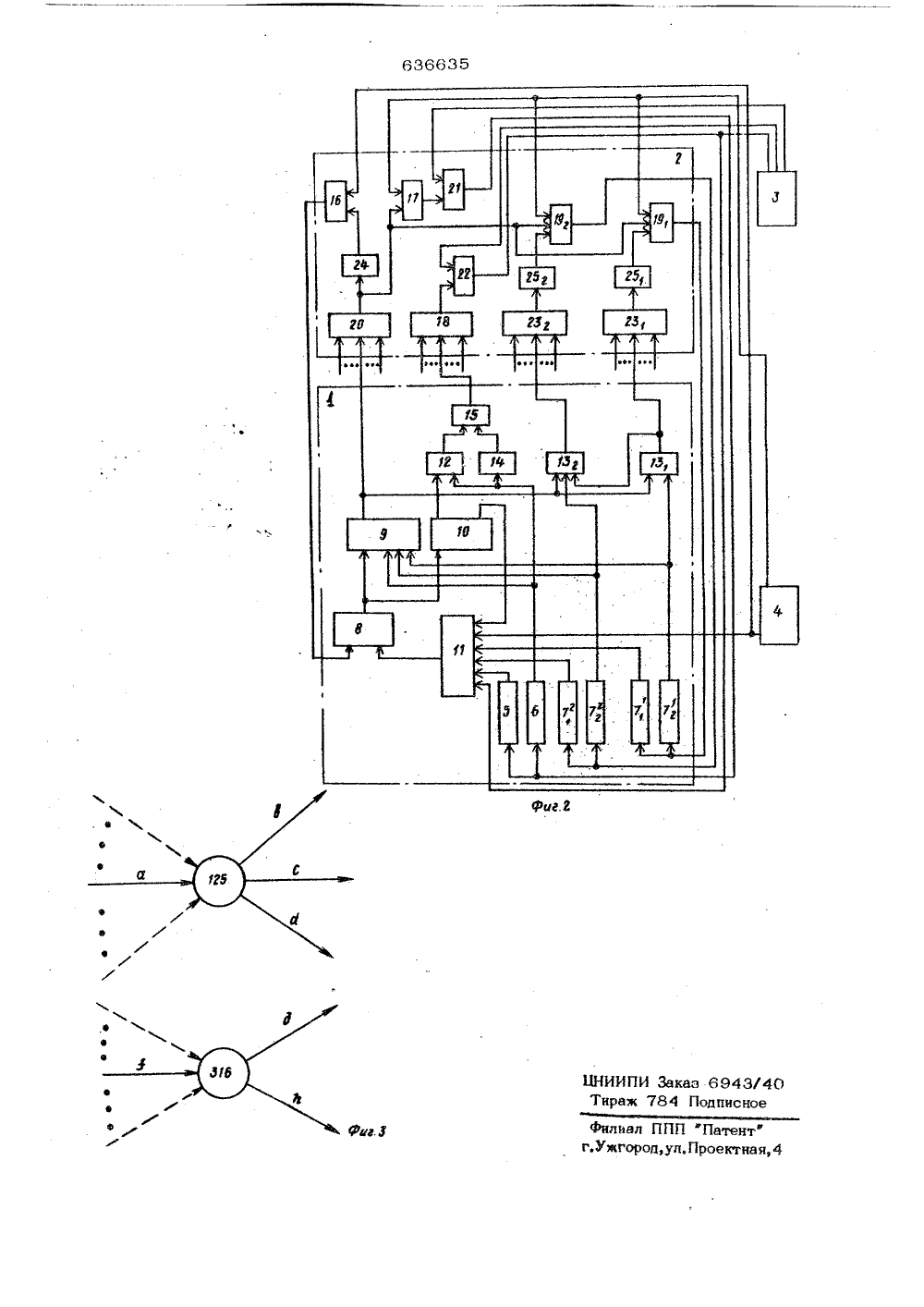

О Й Й С А Н Й Е пщ 636633Й ЗОБ РЕ 3 Е Й Й Я Союз Советских Социалистическими Республик(5) М, Кл6 06 7/48С 067/122 Всемрбтминц 9 веют608 йтй Мнирр 08 Шм днам на 5 рввей ипяй43) Опубликовано 05,12.78 Бюллетень Л публикования описания 15.12.78 Голованова, Е, А. Рали В. В, Хаджинов цки АН Украинской Институт элек) Заявитель 4) УСТРОЙСТВО ДЛЯ МОДЕЛИРОВАНИЯ СЕТЕВЫХ РАФИКОВО Изобретение относится к области вичислительной техники, е именно, к электронным моделирующим устройствам, и является усовершенствованием известного устройства, описанного в авт. св, И. 422002,В основном изобретении по авт.св. 5 М 422002 описано устройство для моделирования сетевых графиков, содержащее блок управлении, первый выход которого подключен к первому входу первого элемента ИЛИ блоке формирования тополо гии, блок моделей ветвей по числу работ сетевого графика, каждая из которых выполнена в виде задатчиков адресов, выходами соединенных с элементами И, причем выход первого элемента И соединен с входом формирователя временных интервалов, вход второго элемента И соединен чеоез инвертор с первым входом элемента ИЛИ, к второму входу которого подключен выход второго элемента И, генератор импульсов, первый и второй выходы которого подключены соответственно ко второму входу первого элемента И каждой модели ветви н к первому входу первого элемента И блоке формирования топологии,второй вход которого соединен с входоминвертора блока формировення топологии,каждая модель ветви содержит триггеры,входы которых соединены с формирователем временных интервалов, причем второйвход первого триггера подключен к первому входу второго элемента И, к второмувходу которого и к третьему входу первого элемента И подключены выходы второго триггера, входы задатчиков адресов,.каждой модели ветви соединены с выходом первого элемента ИЛИ блока формирования топологии, содержашего втооойэлемент ИЛИ, подключенный через инвертор к второму элементу И, и последовательно соединенные третий элемент И итретий элемент ИЛИ, выход и вход которого подключены соответственно к входуи второму выходу блока управления причем первый выход генератора импульсовсоединен с вторым входом второго элемента И блока формирования топологии,ВЫХОД КОТОРОГО ПОДКЛЮЧЕН К ВХОДУ фОР " мирователя временных интервалов каждой моделиветви, вход блока управления соединен с четвертым входом первого элемента И каждой модели Ветви, выход 3 первого триггера каждой модели ветви подключен к входу второго элемента ИЛИ блока формирования топологии, а выход второго элемента ИЛИ каждой модели ветви соединен с входом третьего эле- й мента И блока формирования топологии.Недостатком устройства являются большие затраты времени на модкщрование адресов, снижающие быстродействие устройстВа В целом, ЦБелью дополнительного изобретения является повышение быстродействия уст ройстВаеЗта цель достигается путем сокрашения времени моделирования адресов, за счет последовательно-параллельного моделирования адресов, а именно, последовательно по оазрядам и параллельно по одинаковым разрядам всех адресов.Для этого в каждую модель ветви дополнительно введены (К) пары дискретных линий задержки, где К - максималь ное число разрядов в адресе узлаи (К 1 ) элементОВ И а в блок формирова нйя топологии дополнительно введены В (К -1) элементов И, (К) инверторов; (К) элементов ИЛИ, выход каждого из которых через инвертор подключен к первому Входу соответсгвуошего дополнительного элемента И блока формирования топологии, вторые и третьи входы которых соединены с первым и вторым входами первого элемента И блока формирования топологии соответственно, выходы дополнительных элементов И блоке ф формирования топологии подключены к входам соответствующих пар дополнительных дискретных линий задержки моделей ветвей, выходы первых дополнительных дискретных линий задержки каждой пары соединены с дополнительными входами первого элемента И соответствующей модели ветви, выходы вторых дополнительных дискретных линий задержки каждой пары соединены с дополнительными входами первого триггера соответствующей модели ветви и с первыми входами соответствующих дополнительных элементов И этой модели ветви, вторые входы которых соединеиы с выходом первого триггера этой модели Ветвир третий Вход дополнитель ного элемента И модели ветви, кроме первого, соединен с Выходом предыдушего дополнительного элемента И этой модели ветви, выходы каждого из дополнительных элементов И модели ветви подключены ко входу соответствующего донолнительного элемента ИЛИ блока формирования топологци.На фиг. 1 изображена функциональнаясхема устройства; на фиг. 2 - функциональная схема устройства для 1 =3;на фиг. 3 показан фрагмент сетевогографика, рассмотренный в качестве примераНа фиг. 1 Обозначены: блок 1 моделей ветвей, блок 2 формирования топологии, блок 3 управления, генератор 4импульсов. Каждая модель ветви содержитдискретные линии задержки (ДЛЗ) 5,6 -задатчики адресов начального и конечного узлов соответственно, дополнительныедискретные линии задержки (ДЛЗ) 71,К 7 ", 7, формирователь 8 временныхинтервалов, триггеры 9, 10, элемент И11, 12, дополнительные элементы И 131"13(и инвертор 14, элемент ИЛИ15, Блок формировани топологии содержит элементы И 16, 17, 18, донолнительные элементы И 1919 р ), элементы ИЛИ 20, 21,22, дополнительные элементы ИЛИ 231 23(, 1), инвертор24, дополнительные инверторы 25 ,.25(ц )Работа устройства рассматриваетсядля схемы на фиг. 2 на примере фрагмента сетевого графика (фиг, 3). На фрагменте показаны 2 узла сетевого графикас ветвями, узлы показаны кружками, аветви - стрелками, при этом адреса узлов (125 и 316) показаны в кружках,а номера ветвей проставлены над их изображениями, Пунктиром показаны ветви,которые окончились до рассматриваемогомомента, а сплошными линиями (ветвиО, 1 ) показаны ветви, которые окончились одновременно в рассматриваемыймомент, (ВетвиЬ,С,Й,й еше не начались).Пусть В качестве ЙЛЗ используютсядекадные счетчики импульсов с потенциальным выходом (далее упомянутыеэлементы будем называть счетчиками).Пусть, далее адреса узлов представленыв дополнительном коде (т.е. в счетчикахзаписаны числау дополняющие разряд адреса до полной емквгти счетчика, т.е,до 1 О), Причем сотни записываются вДЛЗ первой пары, тогда первоначальноесодержимое счетчиков соответствует таблице,636635 сигнал запретит поступление импульсовсерии Б нв выход элемента И 19, в яичит, н нв входы всех счетчиков старшегоразряда (т. е. счетчиков 7 7). Булевой сигивд иа выходе элемента И 131модели ветви х запрещает появлениеедньлчиого сигнала нв выходе элементаИ 13 модели ветвиИмпульсы серии Б продолжают посту- р пать нв входы счетчиков десятков и единиц, После следующего импульса серииБ появляется сигнал нв первом входеэлемента И 13 модели ветви с 3; единичный сигнал нв выходе элемента И 13 у Б той же модели ветви разрешает появденве этого сигнала на выходе элементаИ 13, которьш через элемент ИЛИ 23инвеотор - , элемент И 19 зацреЯ уивет поступление импульсов серии Б на 26 входы счетчиков десятков всех моделей ветвей (т,е. нв все элементы 71,-7 Й1 .дновременно единичные сигналыпоявля 1 отся на выходах элементов 712моделей ветвейЬ,С, д . В дальнейшем нм пудьсы серии Б поступают только нвсчетчики 5, 6. Через три импульса серьп Б появляется сигнал нв выходе счет- чика 6 модели ветви О и счетчиков 5моделей ветвей Ь С,3.Ж Так как ветвь д оканчивается последней в узле 125, то нв выходе элемента И 18 формируется единичный сигналкоторый чеоез ИЛИ 22 поступает на входы элементов 11 всех моделей ветвей,3 так квк нв выходах счетчиков 5, 71, 71 Фмоделей ветвей Ь, С, Й присутствуют единичные сигналы, то на всех входах элементов 11 этих моделей ветвей присутствуют единичные сигналы, которые через 46 элементы И 11 поступают на формирователи В упомянутых моделей ветвей, темсамым эти формирователи подготавливаются к отсчету импульсов серии А . Посовпвденко единичиык сигналов с выхо З дов счетчиков 6, 7, 7 модели ветвиО сбрасывается в нудь триггер 9 упомянутой модели, тем свмым запрещая вдальнейшем появдение единичных сигнаыходах эдемей той же модели. Таким образом, сигналыснимаются с входов (в следовательноФс выходов) элементов ИЛИ 231, 23,поэтому через инверторы 251, 25 поступают разрешающие сигналы нв первые ф входы элементов И 191, 19,Твк квк навыходе элемента ИЛИ 20 по-прежнемуприсутствует единичный сигнал (триггер9 модели ветви ( находится в единнчПусть и рассматриваемый момент времени содержимые счетчиков соответствуют таблице. Как отмечено выше, рассмотрение работы начинается с момента, когда одновременно окончились ветви. О1, которые окончились последними нз ветвей, входящих в узлы 125 и 316 (ветви показанные пунктиром на фиг. 3 окончились раньше). В момент окончания ветвей установились в единицу триггеры 9 моделей ветвей а,. Выходы триггеров 9 этих моделей ветвей через элемент ИЛИ 2 О и инвертор 24 запрещают поступление импульсов серии А нв формирователи 8 временных интервалов всех моделей ветвей, эти же выходы обеспечивают разрешающий потенциал на втооых входах элементов И 131, И 13 моделей ветвей О,х, Единичный выход элемента ИЛИ 2 О обеспечивает разрешающий потенциал па третьих входах элементов И 19, И 19 ина втором входе элемента И 17, поскольку на выходах элемен.,- тов ИЛИ 23 ,23 у единичных сигналов нет, на первые входы элементов И 191, И 19 через ннверторы также подаются разрешающие потенциалы, и чеоез элементы И 17, ИЛИ 21, И 191, И 19 на входы счетчиков начинают поступать импульсы серии Б, После поступления одного импульса серии Б появляются сигналы нв выходах счетчиков 7, (модель ветвей Ью , 1 у С,о ), 7 д (модель ветви Д ) 7 (модель ветвейф,И ), 7 (модель ветви х ). Посдьку в каждой модели ветви элементы И 131, И 13, собрвныпопрнорнтетнойсхеме (с прноритетомддя старшего разряда), то единичныйсигнвл появится только нв выходе элемента И 13 модели ветви а,. Через элемент ИЛИ 23 и инвертор 25 этот636635ном состоянии), то импульсы серии Б поступают на выходы элементов И 17, ИЛИ 21, й 1, И 19 и, следовательно, на входы всех счетчиков. Через восемь импульсов серии Б (считая с момента Я установки в ноль триггера 9 модели ветви О появится единичный сигнал на выходе элемента И 131 модели ветви х который разрешит в дальнейшем появление сигнала на выходе И 13 той же мо,; 16 дели ветви и через элемент ИЛИ 23 и инвертор 251 запретит подачу импульсов серии Б на все счетчики старшей декады.Далее процесс продолжается анино.-инно, а именно производится отсчет десятков, 1 затем единиц адреса узла 316, Когда наЛ 4 , мвыходах счетчиков о. (, 7 модели ветвипоявятся единичные сигналы, такие же сигналы появятся на выходах счетчиков 5, 7, 7 моделей .ветвей Я2б ,ц . Так как на остальных входах элементов И 11 уцомянутьи. моделей также будут единичные сигналы, то последние появятся:; на выходах элементов И 11 моделей ветвей а, ), подготавливая Б тем самым формирователи 8 этих моделей к отсчету импульсов серии А, Поскольку после этого единичные сигналы на выходах элемента ИЛИ 20 отсутствуют, на третьи входы элементов И 19 Я 1 9 на второй вход И 1 7 подаютсяээапрещаюшие потенциалыа на вход И 16 через инвертор 24 подается разрешаюший потенциал, импульсы серии Б не поступают на модели ветвей и начинают поступать "3 импульсы серии А на те формирователи 8, иа которые было подано разрешение с выхода элемента И 11 соответствуюшей мо дели ветви.Технико-экономическая эффективность И изобретения заключается в повышении быстродействия устройства по основному изобретению. А именно, для устройства, рассчитанного на моделирование сетевых графиков с максимальным числом узлов 4 ф 999, скоросгь формирования топологии возрастает в 33, 3 раза (так как максимальное число импульсов серии Б, которое необходимо для моделирования адреса в устройстве по основному и допол-нительному изобретениям равно соответственно 999 и ЗО). Как уже отмечалось ььзше время решения задачи устройством равно сумме двух временных интервалов, каждый иэ которых определяется суммарным числом импульсов серии А и Б соответственно, поступивших в блок моделей ветвей, начиная с момента пуска, до момента окончания работы.Формула изобретенияУстройство для моделирования сетевых графиков по авторскому свидетельству Ио 422002, от л и ч а ю ш е ес я тем, что, с целью повышения быстродействия, в каждую модель ветви дополнительно введены (К -1) парыдискретных линий задержки, где К - максимальное число разрядов в адресе узла и (К) эдем.нтов И, а в блок формирования топологии дополнительно введены ( К) элементов И, ( К) инверторов, (К) элементов ИЛИ, выход каждого из которых через инвертор подключен к первому входу соответствуюшего дополнигельного элемента И блока формирования топологии, вторые и третьи входы которых соединены с первым и вторым входами первого элемента И блока формирования топологии соответственно, выходы дополнительных элементов И блока формирования топологии подключены к входам соответствуюцсих пар дополнительных дискретных линий задержки моделей ветвей, выходы первых дополнительных дискретных линий задержки каждой пары соединены с дополнительными входами первого элемента И соответствуюшей модели ветви, выходы вторых дополнительных дискретных линий задержки каждой пары соединены с дополнительными входами первого триггера соответствующей модели ветви и с первыми входами соответствующих дополнительных элементов И этой модели ветви, вторые входы которых соединены с выходом первого триггера этой модели ветви, третий вход дополнительного элемента И модели ветви, кроме первого, соединен с выходом предыдушего дополнитель ного элемента И этой модели ветви, выходы каждого из дополнительных элементов И модели ветви подключены ко входу соответствующего дополнительного элемента ИЛИ блока формирования топологии.БНИИПИ Заказ 6943/4 ираж 784 Подписное Фнлиал ППП Патент" Ужгород,ул, Проектная,

СмотретьЗаявка

2478837, 25.04.1977

ИНСТИТУТ ЭЛЕКТРОДИНАМИКИ АН УКРАИНСКОЙ ССР

ДОДОНОВ АЛЕКСАНДР ГЕОРГИЕВИЧ, ГОЛОВАНОВА ОЛЬГА НИКОЛАЕВНА, РАЛДУГИН ЕВГЕНИЙ АЛЕКСАНДРОВИЧ, ФЕДОТОВ ВЛАДИМИР ВАСИЛЬЕВИЧ, ФЕДОТОВ НИКОЛАЙ ВАСИЛЬЕВИЧ, ХАДЖИНОВ ВЛАДИМИР ВИТАЛЬЕВИЧ

МПК / Метки

МПК: G06G 7/48

Метки: графиков, моделирования, сетевых

Опубликовано: 05.12.1978

Код ссылки

<a href="https://patents.su/6-636635-ustrojjstvo-dlya-modelirovaniya-setevykh-grafikov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для моделирования сетевых графиков</a>

Предыдущий патент: Устройство для моделирования сетевых графиков

Следующий патент: Устройство для моделирования коэффициента теплопроводности

Случайный патент: Способ получения дихлордифенилтрихлорэтана