Микропрограммный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

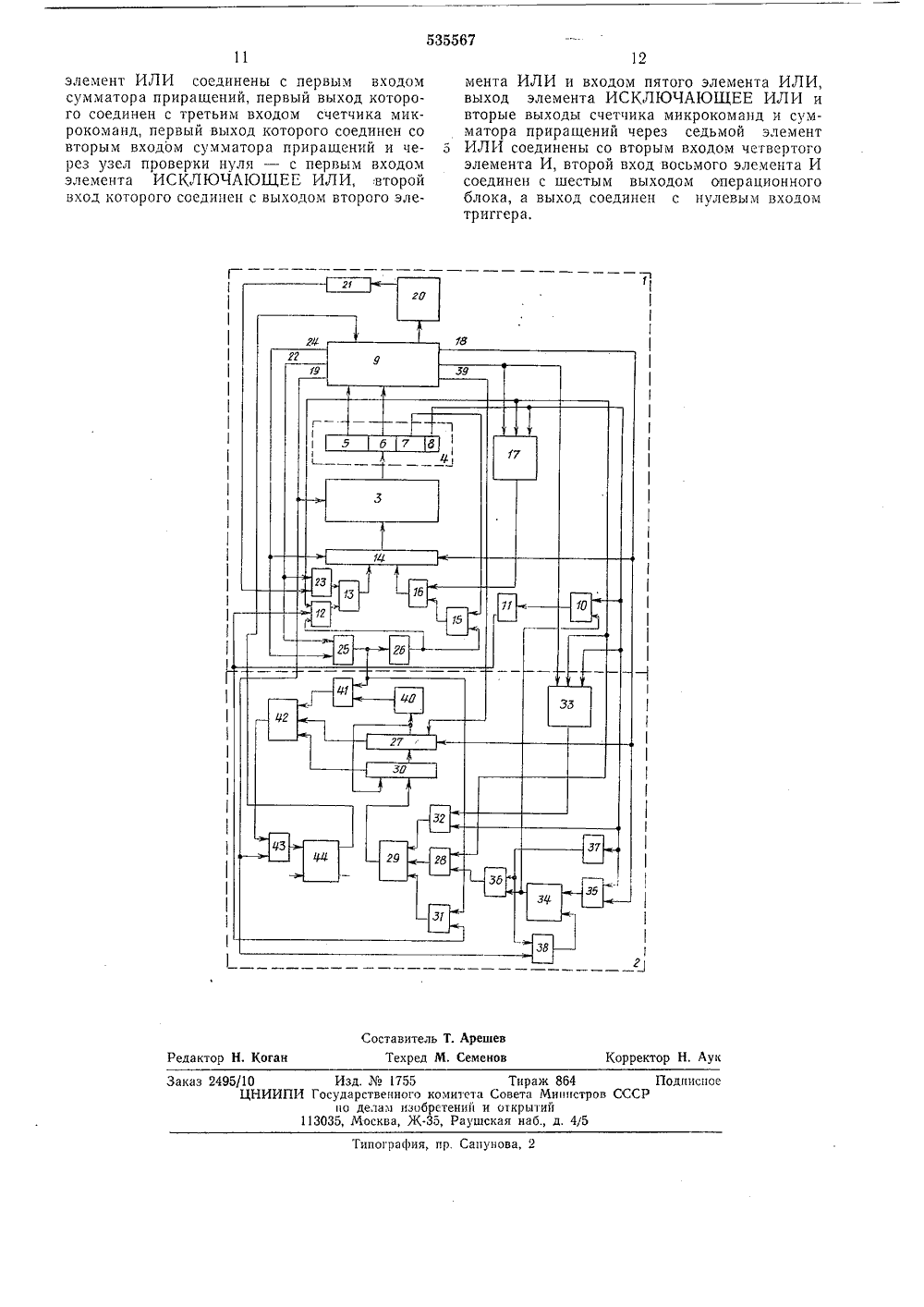

ОПИСАНИЕ ИЗОВРЕТЕН ИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ1 н 1 535562 Соки Советслих Социалистических Республик(21) 2033524 с присоединением заявкиГасударственный комите Совета Министров СССР) УДК 681.326(088,8 елам изобретеиии и открытий ата опубликования описания 30.11.76. Евдолюк, М. М, Каневский и В, Н. Степан лкарт, Ю 1) Заянител Изобретепне относится к вычислительной технике, в частности к проектированию процессоров с контролем.Известны микропрограммные процессоры, содержащие операционный блок, первый выход которого через блок сопряжения с оперативной памятью и регистр кода операций соединен с первым входом первого элемента И, выход которого через первый элемент ИЛИ соединен с первым входом регистра адреса микрокоманд, выход которого через блок памяти микрокоманд соединен со входом регистра микрокоманд, первый и второй выходы которого соединены с первым и вторым входами операционного блока, второй и третий выходы которого шинами начала и конца операции соединены со вторыми входами первого элемента И и регистра адреса микрокоманд соответственно и со входами второго элемента ИЛИ. Выход второго элемента ИЛИ через первый элемент НЕ соединен с первыми входами второго и третьего элементов И, выходы которых через первый и третий элементы ИЛИ соответственно соединены с первым и третьим входами регистра адреса микро- команд, четвертый вход которого соединен с первым входом счетчика микрокоманд и шиной синхронизации с четвертым выходом операционного блока, пятый выход которого соединен со вторым входом счетчика микрокоманд, а шестои выход соединен с управляющим входом блока памяти микрокоманд и спервым входом четвертого элемента И. Выходчетвертого элемента И соединен с единичным5 входом триггера фиксации сбоя, единичныйвыход которого соединен с третьим входомоперационного блока, седьмой выход которогосоединен с первым входом первого узла ветвления, второй вход которого соединен с треть 10 им выходом регистра микрокоманд, третийвход соединен со вторым входом второго элемента И и выходом регистра микрокоманд,четвертый выход которого соединен со вторымвходом третьего элемента И, выход первого15 узла ветвления через третий элемент ИЛИсоединен с третьим входом регистра адресамикрокоманд,Однако в известных процессорах осуществляется контроль микропрограммных последова 20 тельностей параллельно с работой процессоратолько для неразветвленных участков микропрограммы и требует дополнительного времени для выборки проверочных чисел из оперативной памяти, что замедляет работу процес 25 сора. Проверка разветвляющихся участковмикропрограмм производится только в тестовом режиме и отнимает значительную частьрабочего времени процессора.Целью изобретения является повышение на 30 дежности и увеличение быстродействия.Предлагаемый микропрограммный процессор отличается от известных тем, что в негодополнительно введены сумматор приращений,второй узел ветвления, узел проверки нуля,триггер, элементы И, ИЛИ, НЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый вход второгоузла ветвления соедини с одноименным входом первого узла ветвления, второй вход которого соединен с первыми входами пятого ишестого элементов И, через второй элемент 10НЕ - с первыми входами седьмого и восьмогоэлементов И, через четвертый элемент ИЛИи третий элемент НЕ - с третьим входом второго элемента И и с первым входом пятогоэлемента ИЛИ, со вторым входом второго узла ветвления, третий вход которого соединенс третьим входом первого узла ветвления и спервым входом девятого элемента И, а выходвторого узла ветвления соединен со вторымвходом пятого элемента И, второй вход шестого элемента И соединен с четвертым выходом операционного блока, а выход сосдинсн сединичным входом триггера.Единичный выход триггера соединен со входом четвертого элемента ИЛИ и со вторым 25входом седьмого элемента И, выход которогосоединен со вторым входом девятого элемента И,выходы пятого и девятого элементов Ии итого элемента ИЛИ через шестой элементИЛИ соединены с йервым входом сумматора З 0приращений, первый выход которого соединенс третьим входом счетчика микрокомаид, первый выход которого соединен со вторым входом сумматора приращений и через узел проверки нуля - с первым входом элемента ИСКЛЮЧАЮШЕЕ ИЛИ, второй вход которогосоединен с выходом второго элемента ИЛИ ивходом пятого элемента ИЛИ. Выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и вторые выходысчетчика микрокоманд и сумматора приращений через седьмой элемент ИЛИ соединены совторым входом четвертого элемента И, второйвход восьмого элемента И соединен с шестымвыходом операционного блока, а выход соединен с нулевым входом триггера.,Зто позволяет осуществлять контроль микропрограммныхпоследовательностей, включая последовательности с ветвлениями, паралелльно с работойпроцессора и не замедляет его работу,Функциональная схема микропрограммного 50процессора показана на чертеже.Микропрограммный процессор содержитсобственно аппаратуру 1 процессора и аппаратуру 2 контроля последовательности,Микрокоманды выбираются из памяти 3 55микрокоманд в регистр 4 микрокоманды, содержащий поле 5 микрокоманды, поле 6 ветвления, адресное поле 7 и разряд 8 удлиненияадресного поля. Поле 5 микрокоманды управляет работой операционного блока 9. 60Поле 6 ветвления используется в двух назначениях в зависимости от состояния разряда8 удлинения адресного поля, В обычных микрокомандах в разряде удлинения адресногополя записывается нуль и далее 6 ветвления 65 совместно с адресным полем 7 образуют полиоразрядный адрес следующей микрокоманды.Выход четвертого элемента ИЛИ 10 имеет при этом значение нуль и через третий элемент НЕ 11 разрешается работа второго элемента И 12, который передает поле ветвления через первый элемент ИЛИ 13 в старшие разряды регистра 14 адреса микрокоманд, а адресное поле 7 через третьи элементы И 15, ИЛИ 16 передается в его младшие разряды. В микрокомандах, в которых производится ветвление по заданному признаку, в разряде удлинения адресного поля 8 записывается еди ница, а в поле 6 ветвления записывается код, соответствующий проверке заданного признака. Выход разряда удлинения адресного поля 8 через четвертый элемент ИЛИ 10 и третий элемент НЕ 11 блокирует работу второго элемента И 12, запрещая передачу поля ветвления в старшие разряды регистра 14, адреса микрокоманд, и адрес следующей микрокоманды определяется адресным полем 7, передаваемым через третьи элементы И 15, ИЛИ 16 в младшие разряды регистра адреса микрокоманд, старшие разряды которого остаются неизменными. Поле 6 ветвления и проверяемые признаки, вырабатываемые операционным блоком 9 на седьмом его выходе передаются иа первый вход первого узла 17 ветвлений, работа которого разрешается при единичном состоянии разряда удлинения адресного поля 8. Выработанный иа выходе первого узла ветвлений код через вход третьего элемента ИЛИ 16 передается в младшие разряды регистра адреса микрокоманд, изменяя таким образом адрес следующей микрокоманды в соответствии с результатами проверки заданного признака. При этом замещаемые кодом ветвления младшие разряды адреса, записанные в адресном поле 7, должны содержать нули,Прием информации в регистр 14 адреса микрокоманд стробируется синхронизирующим сигналом, вырабатываемым операционным блоком 9 в процессе выполнения текущей микрокоманды на шине 18 синхронизации.Выборка микрокоманды управляется операционным блоком 9 с помощью передачи сигналов по шине 19 чтения микрокоманд в память 3 микрокоманд. Связь с оперативной памятью осуществляется с помощью блока 20 сопряжения с оперативной памятью.Операционный блок 9 осуществляет арифметические и логические преобразования информации и контролирует правильность их выполнения. Правильность считывания информации из памяти 3 микрокоманд в регистр 4 микрокоманды также контролируется по четности операционным блоком 9.Выполнение команды разделено на два цикла: цикл выборки команды из оперативной памяти и адресных преобразований и цикл исполнения команды в соответствии с кодом операции, Цикл выборки команды и адресных преобразований является общим для всех команд, цикл исполнения команды включаетразличные микропрограммы для разных команд.В конце цик,ча выборки команды и адресных преобразований ее код операции передается в регистр 21 кода операции и операционный блок 9 возбу ждает сигнал ца шине 22 начала операции, Прц этом код операции команды через первые элементы И 23, ИЛИ 13 передается в старшие разряды регистра 14 адреса микрокоманд и начинает выполняться микропрограмма цикла исполнения команды.В конце микрокомапды исполнения команды операционный блок 9 возбуждает сигнал на шине 24 конца операции, который гасит регистр адреса мцкрокомацд ц осуществляет переход к выполненьцо микропрограммы цикла выборки следующей команды, начинающейся с н(левого адреса.При наличии сигнала на шине начала операции или на шине конца операции выход второго элемента ИЛИ 25 имеет единичное значение, выход первого элемента НЕ 26 имеет нулевое значение и прием информации в регистр 14 адреса микрокоманд из регистра 4 микро- команд через второй элемент И 12 и третий элемент И 15 блокируется, а осуществляется либо путем информации в регистр 14 адреса микрскоманд из регистра 21 кода операции через первые элементы И 23, ИЛИ 13 либо гашение регистра адреса микрокоманд соответственно.В ходе выполнения циклов выборки и исполнения команды сигналы на шинах начала операции и конца операции отсутствуют, выход второго элемента ИЛИ 25 имеет нулевое значение, а первого элемента НЕ 26 имеет еди ничное значение и прием информации в регистр 14 адреса микрокоманд осуществляется через второй элемент И 12, первый элемент ИЛИ 13, и третьи элементы И 15, ИЛИ 16 из соответствующих полей регистра 4 микро- команды, как описано выше, Для возоуждения сигналов на шинах 22 начала операции и шинах 24 конца операции используются фиксированные значения кодов ветвления. При работе микропрограммного процессора весьма важнь(м является контроль р а боты схем образования адреса следующей микро- команды и схем управления выборкой памяти 3 микрокоманд, так как сбои этой аппаратуры могут привести к нарушениям последовательности мцкроксмацд в микропрограмме, которые не будут обнаружены схемами контроля счцтывацця цнфсрмацц(1 цз памяти мцкрокоманл.1 онтрол(-, микропрограммных последовательностей осуществляется следующим образом.Все микропрограммы представляот собой мцкроподпрограммы, внутри которых отсутствуют ветвления, Ветвлецця Осуществляются прц переходах От Одноц м 1 крсцоднрОГрамГы и другим. Циклы реализуются обычными, етодами ветвлений,При правильной работе процессора к началу микропрограммы цикла выборки цлц цикла исполнения команды счетчик 27 микрокоманд должен быть погашен.5 Рассмотрим выполнение микропрограммыцикла зыборки команды. В первой микрокоманде первой микропрограммы цз поля ветвленя через девятый элемент И 28, шестой элемент ИЛИ 29 и сумматор приращений 30 в 10 счетчик 27 микрокомацд заносится уменьшенное на единицу (исло мцкрокоманд в этойнмикроподпрограмме. В каждой псследующеи микрокоманде через пятый и шестой элементы ИЛИ 31, ИЛИ 29 ц сумматор прццащений 30 15 из счетика микроксмянд Вьчитается единица.В последней микрокоманде этой мцксоподпрограммы, в которой осуцествляется ветвление, из счетчика 27 микрокоманд не вычитается единица, а чецез пятый элемент И 32, 20 шестой элемент ИЛИ 29 и сумматор приращений 30 добавляется код ветвящихся разрядов адреса, вырабатываемый вторым узлом ветвления 33.В первой микрокоманде следуюцей микро подпрограммы, к которой произошел переход врезультате ветвления, цз содержимого счетчика 27 микрокоманд вычитается увеличенный на единицу код ветвящихся разрядов адреса и дооавляется уменьшенное на единицу число микЗ 0 рокоманд в этой микроподпрогра 1 ое, Эта информация берется из поля 6 ветвления регистра 4 микрокоманды и чепез девять(й элемент И 28 и шестой элемент ИЛИ 29 добавляется в сумматоре приращений 30 к содержю(ому счетЗ 5 чика 27 микрокомацд и результат засылаетсяв счетчик микрокоманд. В каждой послечующей микрокоманде этоц микроподпрогпаммы также вычитается единица, В последней микрокоманде этой микроподпрограммы вместо 40 вь.читанця единицы к счетчику 27 микрокоманд прибавляется код ветвящихся разрядов адреса и т. д.Работа счетчика мцкрокомацд описаннымвыше способа: Ослпествляется да выполнения 45 послечней микро(оманды микропрограммыи(кла вь(борки команды. В последней микрокоманде последней микропо;программы в Отчич(е от всех предшествующих Окончаний м(ткроподпрограмм с ветвлениями пз счетчика 50 микрокоманд вычитается единица. счетчикпринимает значение О, возбуждается сигнал на шине 22 начала операции и происходит пеоеход к микропрограмме цикла исполнения команды. Схемы контпочя проверяОт равец ство цул(о счетчлка 27 микрокоманд и в прот(тном случае фиксируют собой пос.едовательности.Прц несправности в схемах формированияадреса илц в схемах выборки памяти 3 икро команд, или в первом узле ветвления 17 в проЦЕССЕ ВЫПОЛНЕНЦЯ ЦЕРаЗВЕтВЛЯ(спцчХСЯ МЦКРО- подпрограмм и 1 Оисхсд 1 гг царцсцце последовательности, выполняется число мцкрокоманд, отчичное от заданного в счетчике мпкрокоманд 05 и к концу выполнения всей микропрограммысчетчик 27 микрокоманл не оулст равен пулю.При выполнении ветвящихся переходов между микроподпрограммами неисправность в указанных схемах приводит к неправильной коррекции содержимого счетчика микрокоманл в 5конце операции и фиксируется схемами контроля,При неисправности в аппарате 2 контроляпоследовательности происходит неправильныйподсчет, и в конце операции счетчик 27 микрокоманд также не будет равен и лю.Контроль последовательности микропрограммы цикла исполнения команды осуществляется описанным способом. В последней микрокоманде возбуждается сигнал на шине 24конца опепации и проверяется равенство нулюсчетчика 27 микрокомянл.Отсутствие сигнала на шине 22 начала операции или шине 24 конца операции при равенстве нулю счетчика 27 микггокоманл восппинимается аппаратурой 2 контроля как сбой последовательности. Кроме того, появление отринательного знака и переполнение счетчикамикрокоманл также соответствует соою последовательности.25Пеглг.ггг "сел т.ст слег 1 гй 17 ппелнязня генлля гЬормировянчя адреса микпокоманлы, ягтппой узел ветвлеггий 33 - лля ппипащениясолепжимого счетчик." 29 микрокоманл привыполнении условных переходов в микропрограмме. При правильной работе после выполнения условного пепехода это приращение солсржимого счетчика микоокоманл должнобыть скорректировано, Наличие двух д блированных алов ветвлений позволяет контролиповять правильность выполнения ветвлений.При сбое во втором узле ветвлений 33 происхолит прибавление к счетчику 27 микрокоманднеправильного коля ветвящихся разрядов адреса. я при сбое в первом узле ветвлений 17 - 4 Опереход не к залапной микроподпрограмме,что ппиволит к неправильной коррекции счетчика 27 микрокоманл в следующей после ветгления микрокоманде, и. в конечном счете, кггерявенстм нулго счетчика микрокоманд в 45конце никла выборки или исполнениякоягг ы,Пепвая мпкрокоманля каждой микпополппогпаммы содержит в поле 6 ветвления мменьгпенное на елиниггт число микрокоманд в этоймикроппогпямме. Адрес следслощей за неймггкпокомянльг определяется только полем 7,хотя разнял уллиненггя алпесного поля 8 равенгглго. Первая микпокоманда каждой микрополпрогпя ммы оппелеляется по состояниютпиггепа 34. Если триггер находится в единичном состоянии, то это означает, что выполняется пепвая после ветвления микрокоманда, вполе 6 ветвления котовой содержится код дляоопекпнп счетчика 27 микрокоманд. Если 6 Отпггггегг находится в гглевом состоянии, то поле ветвления выполняемой микрокоманды содержит либо кол гетвления, либо старшиеразряды адреса следующей микрокоманды взависимости от значения разряда удлинения 65 адресного поля 8. Каждое ветвление сопровождается единичным значением разряда удлинения адресного поля 8, который при наличии импульса на шине 18 синхронизации открывает шестой элемент И 35 и устанавливает в единичное состояние триггер 34. Единичный выход триггера соединен со вторым входом седьмого элемента И 36, первый вход которого через второй элемент НЕ 37 соединен с раз. рядом удлинения адресного поля 8,Вход гашения триггера 34 соединен с выходом восьмого элемента И 38, первый вход которого через второй элемент НЕ 37 соединен с разрядом удлинения адресного поля 8, а второй вход соединен с шиной 19 чтения микрокоманд. Таким образом триггер 34 устанавливается в единичное состояние в микрокоманде с ветвлением, а гасится в конце следующей за ветвлением микрокоманды Гпри чтении второй после ветвления микрокоманлы). При этом седьмой элемент И 36 бучет открыт только в течение первой после ветвления микрокоманлы и откроет второй вход девятого элемента И 28, первый вход которого связан с полем 6 ветвления регистра 4 микрокоманды Выхол девятого элемента И 28 соелинен со входом шестого элемента ИЛИ 29, выход котопого соелинен с пепвым входом сумматора 30 приращений. второй вход которого соединен с первым выходом счетчика 27 микро- команд, а выход соединен с третьим входом счетчика микпокоманл. Сумматор приращений 30 предназначен для контроля выполнения ветвлений. Через него осуществляется приращение счетчика 27 микрокоманд при выполнении ветвлений и коррекция содержимого счетчика микрокоманд после выполнения ветвлении. Таким образом чепез левятый элемент И 28 и шестой элемент ИЛИ 29 в первой после ветвления Га также после конца и начала операции) микрокоманде в сумматоре приращений 30 к солепжимомч счетчика 27 микро- команд добавляется содержимое поля 6 ветвления и результат помещается в счетчик 27 мгкрокоманд,В процессе выполнения каждой послелующей микрокоманлы, кроме последней в микро- подпрограмме, из счетчика 27 микрокоманл вычитается единица (а также и в микрокоманлах конца операции гг начала операггии).Выход третьего элемента НГ 11. связанного по входу через четвертый элемент ИЛИ 10 с разрядом уллинения адресного поля 8 и триггером 34, имеет единичное значение во всех микрокомяндах, кроме псовой и посггелней микрокоманд каждой микоополппограммы.При этом выход третьего элемента НГ 11 соединен с первым входом пятого элемента ИЛИ 31, выход котопого соелгпген со входом шестого элемента ИЛИ 29. Второй вход пятого элемента ИЛИ 31 соединен с гыхолом гторого элемента ИЛИ 25, котооый возблкляется при наличии сигнала лггбл ия шине 22 начала операции, либо на шине 24 конца операции. В случае возбуждения одного из выходов пятого элемента ИЛИ 31 через шестой элемент ИЛИ 29 в сумматоре приращений 30 происходит вычитание единицы из содержимого счетчика 27 микрокоманд.При выполнении микрокоманды с ветвлением выход разряда 8 удлинения адреса подается на первый вход пятого элемента И 32, на второй вход которого подается код ветвящихся разрядов адреса, вырабатываемых вторым узлом ветвлений 33. Выход пятого элемента И 32 соединен с третьим входом шестого элемента ИЛИ 29. Таким образом при выполнении микрокоманд с ветвлениями код ветвящихся разрядов адреса чеРез пятый элемент И 32 и шестой элемент ИЛИ 29 поступает на вход сумматора приращений 30 и добавляется к счетчику 27 микрокоманд.Гашение счетчика 27 микрокоманд осуществляется сигналом на шине гашения счетчика 39. Работа счетчика 27 микрокоманд синхронизирована сигналом на шине 18 синхронизации,Выход счетчика 27 микрокоманд соединен со входом узла 40 проверки нуля, выход которого соединен с пепвым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 41, второй вход которого соединен с выходом второго элемента ИЛИ 25. Элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 41 возбуждается либо когда содержимое счетчика 27 микрокоманд равно нулю, но нет сигналов на шинах 22 начала операции или шинах 24 конца операции, либо когда есть сигналы на шинах начала операции или конца операции, по счетчик микрокоманд не равен нхлю.Выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 41 соединен с первым входом седьмого элемента ИЛИ 42, второй вход которого соединен с единичным выходом знакового разряда (отрицательный знак) счетчика микрокоманл, третий его вход соединен с выходом переполнения сумматора приращений 30, а выход соединен со вторым входом четвертого элемента И 43, второй вход которого соединен с шиной 19 чтения микпокоманл. Выход четвертого элемента И 43 соединен с единичным входом триггера 44 фиксации сбоя, единичный выход которого соединен с третьим входом операциоппого блока 9,Таким образом триггер 44 фиксации сбоя устанавливается в елиничное состояние при несовпадении сигналов на шинах начала операции или конца операции с сигналом равенства нлю счетчика микрокоманд, а также в случае переполнения сумматора приращений и появления отрицательного солеркимого счетчика микрокоманл. При этом операционный блок 9 прскрагцает выполнение текущей последоватс, ьности.Формула цзобрстснияМикропрогпаммньш процессор, содержащий опсрацпл цый блок, первый выход которого чеосз блок сопряжения с опепативной памятью и регистр кола операций соединен с первым входом первого элемента И, выход которого через первый элемент ИЛИ соединен65 тов И и пятого элемента ИЛИ через шестой с первым входом регистра адреса микро- команд, выход которого через блок памяти микрокоманд соединен со входом регистра микрокоманл, первый и второй выходы кото рого соединены с первым и вторым входамиоперационного блока, второй и третий выходы которого шинами начала и конца операции соединены со вторыми входами первого элемента И и регистра адреса мпкрокоманл соответ ственно и со входами второго элемента ИЛИ,выход которого через первый элемент НЕ соединен с первыми входами второго и третьего элементов И, выходы которых через первый и третий элементы ИЛИ соответственно соедине ны с первым и третьим входами регистра адреса микрокоманд, четвертый вход которого соединен с первым входом счетчика микро- команд и шиной синхронизации с четвертым выходом операционного блока, пятый выход 20 которого соединен со вторым входом счетчикамикрокоманл, а шестой выход соединен с управляющим входом блока памяти микро- команд и с первым входом четвертого элемента И, выход которого соединен с единичным 25 входом триггсра фиксации сбоя, единичныйвыход которого соединен с третьим входом операционного блока, сельмой выход которого соединен с первым входом первого узла ветвления, второй вход которого соединен с тре тьим выходом регистра микрокоманд, третийвход соелинен со вторым входом второго элемента И и выходом регистра микрокоманл, четвертый выход которого соединен со вторым вхолом третьего элемента И, выход пепвого 35 узла ветвления через третий элемент ИЛИсоединен с третьим вхолом регистра адреса микрокоманд, отличающийся тем, что, с целью повышения надежности и увеличения быстродействия, в него дополнительно введе ны сумматор приращений, второй узел ветвления. х зел провепки ю ля. тпиггер. элементы И, ИЛИ. НЕ, ИСКЛЮЧАЮЩЕЕ ИЛИ, причем первый вход второго узла ветвления соединен с одноименным входом первого узла ветвле ния, второй вход которого соединен с первымивходами пятого и шестого элементов И, через второй элемент НЕ - с первыми входами седьмого и восьмого элементов И, через четвертый элемент ИЛИ и третий элемент НЕ - 50 с третьим входом второго элемента И и с первым входом пятого элемента ИЛИ, со вторым входом второго узла ветвления, третий вход которого соелинен с третьим входом первого узла ветвления и с первым вхолом девятого 55 элемента И, а выход второго узла ветвлениясоединен со вторым вхолом пятого элемента И, второй вход цестого элемента 1 Л соединен с четвертым выходом операционного блока, а выход соединен с единичным входом 60 триггера, единичный выход котопого соединенсо вхолом четвертого элемента ИЛИ и со втопым вхолом седьмого элемента И, выход которого соединен со вторым входом девятого элемента И, выходы пятого и девятого элемен535567 12 1 1 Составитель Т. Ареше Техред М. Семено рректор Н. Ау едактор Н, Кога Тираж 864Совета Министроткрыл ийкая наб., д. 4/5 Изд.1755И Государственного комитета по делам изобретений 113035, Москва, Ж, Рауш Заказ 2495/10ЦНИ ПодписпоР Гипография, пр, Сапунова, 2 элемент ИЛИ соединены с первым входом сумматора приращений, первый выход которого соединен с третьим входом счетчика микрокоманд, первый выход которого соединен со вторым входом сумматора приращений и через узел проверки нуля - с первым входом элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, второй вход которого соединен с выходом второго элемента ИЛИ и входом пятого элемента ИЛИ, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и вторые выходы счетчика микрокоманд и сумматора приращений через седьмой элемент 5 ИЛИ соединены со вторым входом четвертогоэлемента И, второй вход восьмого элемента И соединен с шестым выходом операционного блока, а выход соединен с нулевым входом триггера.

СмотретьЗаявка

2033524, 10.06.1974

ПРЕДПРИЯТИЕ ПЯ Г-4128

ДОЛКАРТ ВЛАДИМИР МИХАЙЛОВИЧ, ЕВДОЛЮК ЮРИЙ МАКСИМОВИЧ, КАНЕВСКИЙ МИХАИЛ МАТВЕЕВИЧ, СТЕПАНОВ ВИКТОР НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 11/16, G06F 17/00, G06F 9/22

Метки: микропрограммный, процессор

Опубликовано: 15.11.1976

Код ссылки

<a href="https://patents.su/6-535567-mikroprogrammnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор</a>

Предыдущий патент: Феррорезонансный стабилизатор тока

Следующий патент: Устройство для формирования временных интервалов

Случайный патент: Установка для обработки листового стекла в процессе его изготовления