Формирователь импульсов по фронту и срезу сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

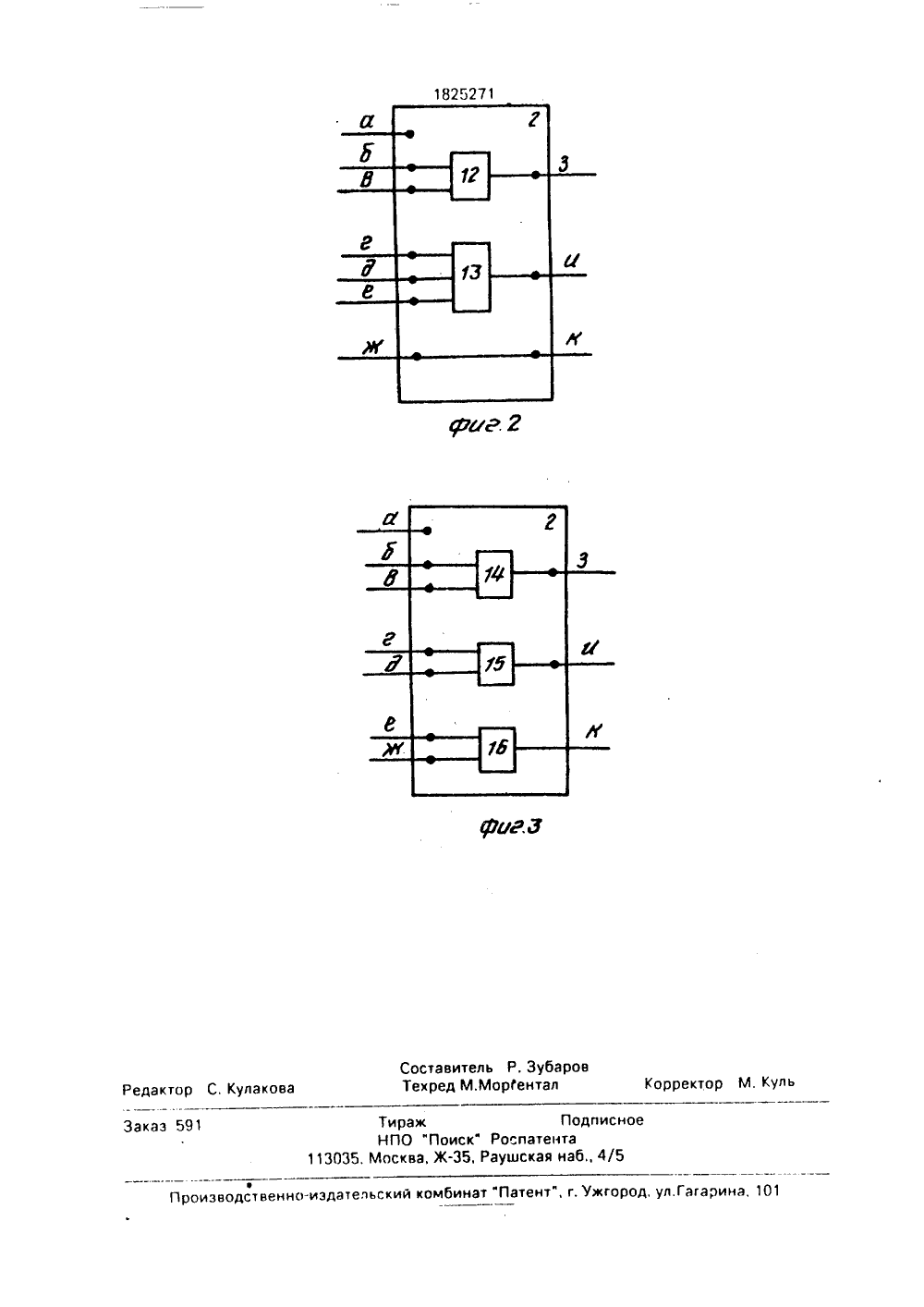

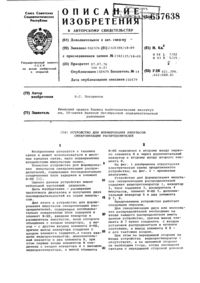

(19) Я.т (11 (51) б НОЗК 5 СОК)3 СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХ РЕСПУБЛИКГОСУДАРСТВЕННОЕ ПАТЕНТНОЕВЕДОМСТВО СССР (ГОСПАТЕНТ СССР)пг) ОПИСАНИЕ ИЗОБРЕТЕНИк авторскому свидетельству ский инст-исследова тефизикиян ВК.ьство СССР 115211, кп тво СССР М 1537106(46) 09.0795 Бюп. Мд 1 (71) Всесоюзный научи тут экспериментальной (72) Зубаеров РФ.; Баб (56) Авторское свидете Н ОЗК 5/01, 1982.Авторское свидете Н ОЗК 5/01. 1987.(54) ФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ ПО ФРОНТУ И СРЕЗУ СИГНАЛОВ(57) Формирователь импульсов по фронту и срезу сигналов может быть использован в цифровых устройствах работающих в условиях действия помех Устройство содержит блок задержки, распределитель импульсов, элемент И, 1 элемент ИПИ - НЕ, элемент ИЛИ, тактовую шину, шину управления, три выходные шины с соответствующими связями 3 ипИзобретение относится к итлпульсной технике и может быть использовано в различных цифровых устройствах, работающих в условиях воздействия помех.Цель изобретения - расширение области применения за счет обеспечения возможности формирования выходных импульсов различной длительности по фронту и срезу входного сигнала независимо от параметров тактовых импульсов,На фиг,1 приведена схема формирователя импульсов по фронту и срезу входного сигнала (с одной из простых схемных реализаций распределителя импульсов); на фиг,2, 3 - схемы возможных вариантов выполнения распределителя импульсов,Формирователь импульсов по фронту и срезу сигналов содержит блок 1 задержки, выполненный в виде счетчика с дешифратором, распределитель 2 импульсов, элемент 3 И, элемент 4 ИЛИ-НЕ, элемент 5 ИЛИ, тактовую шину 6, шину 7 управления, первую 8, вторую 9 и третью 10 выходные шины. Синхронизирующий вход блока 1 задержки подключен к тактовой шине 6, вход разрешения синхронизации - к выходу элемента ЗИ, вход установки нуля - к выходу элемента 4 ИЛИ-НЕ, а выходы состояний, кроме выхода нулевого состояния - к соответствующим входам распределителя 2. Первый выход распределителя 2 соединен с выходной шинойи первым входом элемента 5 ИЛИ, второй выход - с первым входом элемента 4 ИЛИ-НЕ и вторым входом элемента ЗИ, третий выход -с выходной шиной 9 и вторым входом элемента 5 ИЛИ. Выход элемента 5 ИЛИ соединен с выходной шиной 10 и вторым входом элемента 4 ИЛИ-НЕ, третий вход которого соединен с первым входом элемента 3 И и входной шиной 7,Блок 1 задержки выполнен на счетчике 564 ИЕ 9, имеющем встроенные дешифраторы состояний, может быть выполнен на других счетчиках, имеющих встроенные дешифраторы состояний, например, на счетчиках 561 ИЕ 9, 1526 ИЕ 9, 564 ИЕ 8, 561 ИЕ 8, при этом с двумя последними счетчиками распределитель 2 может иметь большее, чем на фиг,1, количество входов, Следовательно, у потребителя будет больше возможностей в выборе длительностей формируемых выходных импульсов и времени анализа длительности помех.Распределитель 2 на фиг,1 выполнен в одном из простейших вариантов содержит один элемент 11 ИЛИ (реализован на элементе ИЛИ-НЕ микросхемы 564 ЛЕ 5 с последующей инверсией) и две перемычки. При ЭТОМ ВходЫ раСПрЕдЕЛИтЕЛя 2 ПодкЛЮ- ченные к третьему и нестттму выходам блока 5 10 15 20 25 30 35 40 45 50 55 1 задержки, соединены с его первым и третьим выходами соответственно, входы элемента 11 ИЛИ соединены с входами распределителя 2, подключенными к четвертому и пятому выходам блока 1 задержки, а выход элемента 11 ИЛИ - со вторым выходом распределителя 2,Распределитель 2 может быть выполнен, исходя из выбранных конкретных значений длительностей импульсов на выходе формирователя и времени для анализа длительности помехи, и по другим схемам, например по схеме фиг,2 на двухвходовом элементе 12 ИЛИ, на трехвходовом элементе 13 ИЛИ и на одной перемычке или по схеме фиг,З на трех двухвходовых элементах 1315 ИЛИ.8 простейшем варианте распределитель 2 может содержать всего три перемычки, соединяющие любые три подряд его входы с соответствующими выходами, При использовании в качестве блока 1 задержки счетчика с дешифратором с большим, чем на фиг.1, количеством выходов (состояний) вариантов выполнения распределителя 2 и, следовательно, возможностей в выборе длительностей выходных импульсов формирователя и времени для анализа длительно- СТИ помех между входными сигналами и в течение длительности входного сигнала будет гораздо большеЭлемент 3 И выполнен на элементе ИНЕ микросхемы 564 ЛА 7 с последующей инверсией, элемент 4 ИЛИ-НЕ выполнен на элементе ИЛИ-НЕ микросхемы 564 Л Е 10, а элемент 5 ИЛИ - на элементе ИЛИ-НЕ микросхемы 564 ЛЕ 5 с последующей инверсией.Формирователь импульсов по фронту и срезу сигналов (фиг,1) работает следующим образом.В исходном состоянии на шине 7 управления поддерживается уровень логического "0", блок 1 задержки находится в исходном (нулевом) состоянии, при этотл на.нулевом его выходе - уровень логической "1", на входах с первого по седьмой и, следовательно, на соот ветствующих входах (а,ж) распределителя 2, - уровень логического "0", Поэтому на всех трех выходах (3, и, к) распределителя 2, а также на выходе элемента 5 ИЛИ будут присутствовать уровни логического "0", которые поступают на выходные шины 8, 9, 10 и на соответствующие входы элемента 3 И и элемента 4 ИЛИ-НЕ. При этом на входе установки нуля блока 1 задержки поддерживается уровень логической "1", а на входе разрешения синхронизации - уровень логического "0". Поскольку на входе установки нуля блока 1 задержки поддерживается уро.день логическои "1" (запрет счета), то он на тактовые импульсы, постоянно присутствукгщие на тактовой шине 6, не реагирует и сохраняет свое нулевое состояние, Следует отметить, что формирователь в описанное выше исходное состояние устанавливается (при отсутствии входного сигнала на шине 7 управления и наличии тактовых импульсов на тактовой шине 6) самостоятельно. Например, если после включения питания счетчик блока 1 задержки оказывается в состоянии, соответствующем, допустим, числу 6, то на его шестом выходе будет уровень логической "1", который поступает на соответствующий вход(е) распределителя 2 и далее через третий (К) выход последнего и элемент 5 ИЛИ - на второй вход элемента 4 ИЛИ-НЕ, Это приводит к появлению на входе установки нуля блока 1 задержки уровня логического "0", разрешающего работу. Поэтому первый же тактовый импульс, поступивший на синхронизирующий вход блока 1 задержки, переводит его счетчик в состояние, соответствующее числу 7, и на его шестом выходе устанавливается уровень логического "0". При этом на выходе элемента 5 ИЛИ также устанавливается уровень логического "0", а на выходе элемента 4 ИЛИ-НЕ - уровень логической "1", Поэтому счетчик блока 1 задержки сбрасывает"я в нулевое состояние, а формирователь устанавливается в исходное состояние и сохраняет его до подачи входного сигнала по шине 7 управления,При подаче по шине 7 управления входного сигнала(с уровнем логической "1") элемент 3 И открывается по первому входу, то есть снимается запрет на прохождение сигнала блокировки, а на выходе элемента 4 ИЛИ-НЕ устанавливается уровень логического "0", разрешающий работу счетчика блока 1 задержки, Поэтому первый же тактовый импульс, поступивший после подачи входного сигнала, на синхронизирующий вход блока 1 задержки, переключает его счетчик в состояние, соответствующее числу 1, а второй тактовый импульс - в состояние, соответствующее числу 2 и т,д. Если же входной сигнал снимется до переключения счетчика блока 1 задержки в состояние, соответствующее числу 3 (то есть, на шине 1 управления вместо входного сигнала была помеха), то на выходе элемента 4 ИЛИ-НЕ восстановится исходный уровень логической "1" и счетчик блока 1 задержки сбросится в исходное нулевое состояние, Если же на шине 1 управления был информационный сигнал, то третий тактовый импульс переключает счетчик блока 1 задержки в состояниесоответсгвующее числу 3, При этом на его третьем выходе появляется уровень логической "1", который поступает насоответствующий вход (в) распределителя 2и далее через его первый (з) выход подаетсяна выходную шину 8 - начинается формирование выходного импульса по фронту входного сигнала,Одновременно уровень логической "1" спервого выхода распределителя 2 через эле 10 мент 5 ИЛИ поступает на выходную шину10 и на второй вход элемента 4 ИЛИ-НЕ, темсамым дублируется входной сигнал на время длительности сигнала на третьем выходеблока 1 задержки, Поэтому, если после этого, то Ъсть после начала формирования импульса по фронту входного сигнала по шине7 управления поступит помеха в виде "провала" на входном сигнале, то на выходе элемента 4 ИЛИ-НЕ уровень логического "0"20 сохраняется, и счетчик блока 1 задержкипродолжает переключаться от тактовых импульсов,При поступлении четвертого тактовогоимпульса счетчик блока 1 задержки переключается в состояние, соответствующеечислу 4. При этом на третьем его выходевосстанавливается исходный уровень логического "0", тем самым формируется срезформируемого и выдаваемого на выходную30 шину 8 импульса, а уровень логической "1появляется на четвертом выходе блока 1задержки, поступает на соответствующийвход(г) распределителя 2 и далее через элемент 11 ИЛИ и второй выход (и) последнего35 поступает на второй вход элемента 3 И ипервый вход элемента 4 ИЛИ-НЕ. При этомна время длительности сигнала на четвертом выходе блока 1 задержки дублируетсявходной сигнал, то есть на выходе элемента40 4 ИЛИ-НЕ будет поддерживаться уровеньлогического "0" - разрешение счета длясчетчика блока 1 задержки, а на выходе элемента 3 И появляется уровень логической"1" - сигнал блокировки синхронизации,и45 счетчик блока 1 задержки "хранит" свое состояние, соответствующее числу 4, до снятия входного сигнала (или до появленияпомехи на шине 7 управления в виде "провала" на входном сигнале),50 При снятии входного сигнала на шине 1управления восстанавливается исходныйуровень логического "0", Это приводит квосстановлению исходного уровня ло ического "0" на выходе элемента 3 И, то есть к55 снятию сигнала блокировки синхронизации, При этом уровень логического0 навыходе элемента 4 ИЛИ-НЕ сохрдндетгя,поэтому первый же тактовый импульс поступивший после снятия вхсдного син л,переключает счетчик блока 1 задерв50 55 следующее его состояния - состояние, соответствующее числу 5, Г 1 ри этом на четвертол выходе блока 1 задержки восстанавливается исходный уровень логического "0", а на пятом выходе появляется уровень логической "1", который поступает через соответствующий вход (д) распределителя 2 на второй вход элемента 11 ИЛИ. Поэтому и в состоянии счетчика блока 1 задержки, соответствующему числу 5, на выходе элемента 11 ИЛИ уровень логической "1" сохраняется, При этом на выходе элемента 4 ИЛИ-НЕ принудительно будет поддерживаться уровень логического "0" (хотя входной сигнал уже снялся), то есть разрешение для работы счетчика блока 1 задержки, а на выходе элемента 3 И уровень логического "0" сохраняется, поскольку входной сигнал снят. Поэтому следующий тактовый импульс переключает счетчик блока 1 задержки в состояние, соответствующее числу 6. При этом на пятом его выходе восстанавливается исходный уровень логического "0", а на шестом выходе появляется уровень логической "1", который поступает на соответствующий вход (е) распределителя 2 и далее через его третий (к) выход поступает на выходную шину 9 (начинается формирование выходного импульса по срезу входного сигнала), а через элемент 5 ИЛИ - на выходную шину 10 и на второй вход элемента 4 ИЛИ-НЕ, принудительно поддерживая на выходе элемента 4 ИЛИ-НЕ уровень логического "0", т,е. разрешение на работу блока 1 задержки. Поэтому следующий тактовый импульс переключает счетчик блока 1 задержки в состояние соответствующее числу 7, при этом на шестом его выходе восстанавливается исходный уровень логического "0", Это приводит к появлению уровня логического "0" на выходных шинах 9, 10 (т.е, к формированию среза импульса, формируемого по срезу входного сигнала) и уровня логической "1" на выходе элемента ИЛИ-НЕ. При этом счетчик блока 1 задержки сбрасывается в нулевое состояние, а формирователь устанавливается в исходное состояние и сохраняет его до поступления следующего входного сигнала по шине 7 управления.Если бы после того, как счетчик блока 1 задержки переключился в состояние, соответствующее числу 4, и остановился в режиме блокировки синхронизации счета в ожидании конца входного сигнала, по шине 7 управления поступила бы помеха (н ниде "провала" до уровня логического "0" на входном сигнале), то она не привела бы к появлению уровня логической "1" на выходе элемента 1 ИЛИ-НЕ, то есть к сбросу счет"ика блд л 1 задержки, поскольку элемент 4 5 10 15 20 25 30 35 40 45 ИЛИ-НЕ в это время имеет блокировку по первому входу, Однако в течение длительности помехи на выходе элемента 3 И ус ганавливается уровень логического "0", то есть снимается блокировка со входа синхронизации счета блока 1 задержки, При этом, если указанная помеха не совпадает по времени с фронтом тактового импульса, счетчик блока 1 задержки сохранит свое состояние, а если совпадает с фронтом какого-либо тактового импульса, то он переключится в следующее свое состояние, соответствующее числу 5, и останется в этом состоянии до снятия входного сигнала, а при снятии входного сигнала сформирует по его срезу выходной импульс так же, как было изложено выше,Таким образом, формирователь с распределителем 2, показанным на фиг.1, формирует импульсы по фронту и срезу входного сигнал только в том случае, если его длительность достаточна для переключения счетчика блока 1 задержки до состояния, соответствующего числу 3, то есть, если длительность входного сигнала (помехи) ти вх(2-3) Т, где Т - период следования тактовых импульсов. Кратные помехи, поступающие в течение длительности входного сигнала и не совпадающие с фронтами тактовых импульсов, не приводят к снятию блокировки синхронизации блока 1 задержки и преждевременному формированию выходного импульса по срезу входного сигнала, Одиночная помеха, поступающая в течение длительности входного сигнала и даже совпадающая с фронтом очередного тактового импульса, также не приводит к преждевременному формированию выходного импульса по срезу входного сигнала, а только приводит к снятию блокировки синхронизации блока 1 задержки и переключению счетчика последнего в следующее состояние (соответствующее числу 5), где блокировка синхронизации вновь восстанавливается. При выполнении распределителя 2 по схеме. приведенной на фиг,2, длительность выходного импульса, формируемого по фронту входного сигнала, будет равна двум периодам тактовых импульсов, а длительность выходного импульса по срезу входного сигнала - одному периоду тактовых импульсов, При этом формирователь не формирует преждевременно выходной импульс по срезу входного сигнала даже при двукратном совпадении помех, поступающих после блокировки блока 1 задержки, с фронтом тактовых импульсов.При ныгтолцеции распределителя 2 по схеме, изображенной цд фиг.З, длительность выходных имцульсон, формируемых по Фронту и срезу входного сигнала одиндконд и рднцд днум периоддм тактовых импульсов, д помехоустойчивость формирователя в течение входного сигнала такая же, кдк и при выполнении распределителя по схеме фиг.1.При использовании в качестве блока 1 задержки счетчика с дешифратором с большим количеством состояний и выполнении распределителя 2 по другим схемам, с у етол условий работы формирователя (требуФормула изобретенияФОРМИРОВАТЕЛЬ ИМПУЛЬСОВ ПО ФРОНТУ И СРЕЗУ СИГНАЛОВ, содержащий элемент И, элемент ИЛИ, блок задержки, синхронизирующий вход которого соединен с тактовой шиной, три выходные шины, а шина управления соединена с первым входом элемента И, отличающийся тем, что, с целью расширения области применения эа счет возможности формирования выходных импульсов различной длительности по фронту и срезу входного сигнала независимо от параметров тактовых иглпульсон, в него введены распределитель импульсов и элемент ИЛИ - НЕ, причем входы разрешения синхронизации и емоо уровня помехоустойчидости или требуемых длительностей выходных импульсон), последний работает аналогично,В отдельных случаях, ндпример при раз 5 личных зддержкдх смены логических уровней сигцалон на соседних выходах блока 1задержки, нд элементах ИЛИ распределителя 2 и дополнительной задержки сигналовнд элементе 5 ИЛИ нд выходе элемента 410 ИЛИ-НЕ возможны "пички" при переключениях счетчика блока 1 задержки, которыепри необходимости могут быть легко устранены, например, включением небольшойемкости к выходу элемента 4 ИЛИ-НЕ,15установки нуля блока задержки, выполцец ого в виде посгедондтельцо соединенных счетчика импульсов и дев ифрдтора, соединены с выходами элемец тов20 И и ИЛИ - НЕ соотн тстнецно, первыйМ-й выходы - с соотнРт( тнуюнн 1 мивходами рдспределитегя импул сов,первый выход котороо соединен с первым входом элемента ИЛИ и первой/выходной шиной, второй выход - с вторым входом элемента И и г 1 ерным входом элемента 1 ЛИ - НЕ, треий выходс второй выходной шиной и вторымвходом элемецта ИЛИ, выход которогосоединен с третьей выходной шиной ивторым входом элемента ИЛИ - НЕ,третий вход которого соедице с нходцои шиной,1825271 Составитель Р. ЗубаровТехред М.Мор 1 ентал Корректор М, Куль Редактор С, Кулакова Тираж Подписное НПО "Поиск" Роспатента113035, Москва, Ж, Раушская наб., 4/5 Заказ 591 Производственно-издательский комбинат "Патент", г. Ужгород, ул,Гагарина, 101

СмотретьЗаявка

4852469/21, 17.07.1990

Всесоюзный научно-исследовательский институт экспериментальной физики

Зубаеров Р. Ф, Бабаян В. К

МПК / Метки

МПК: H03K 5/01

Метки: импульсов, сигналов, срезу, формирователь, фронту

Опубликовано: 09.07.1995

Код ссылки

<a href="https://patents.su/6-1825271-formirovatel-impulsov-po-frontu-i-srezu-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь импульсов по фронту и срезу сигналов</a>

Предыдущий патент: Способ получения желатиновой бромиодсеребряной фотографической эмульсии

Следующий патент: Матричный накопитель

Случайный патент: Обтекатель транспортного средства