Модулятор фазоманипулированных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1771077

Авторы: Боташев, Пархоменко, Шеляпин

Текст

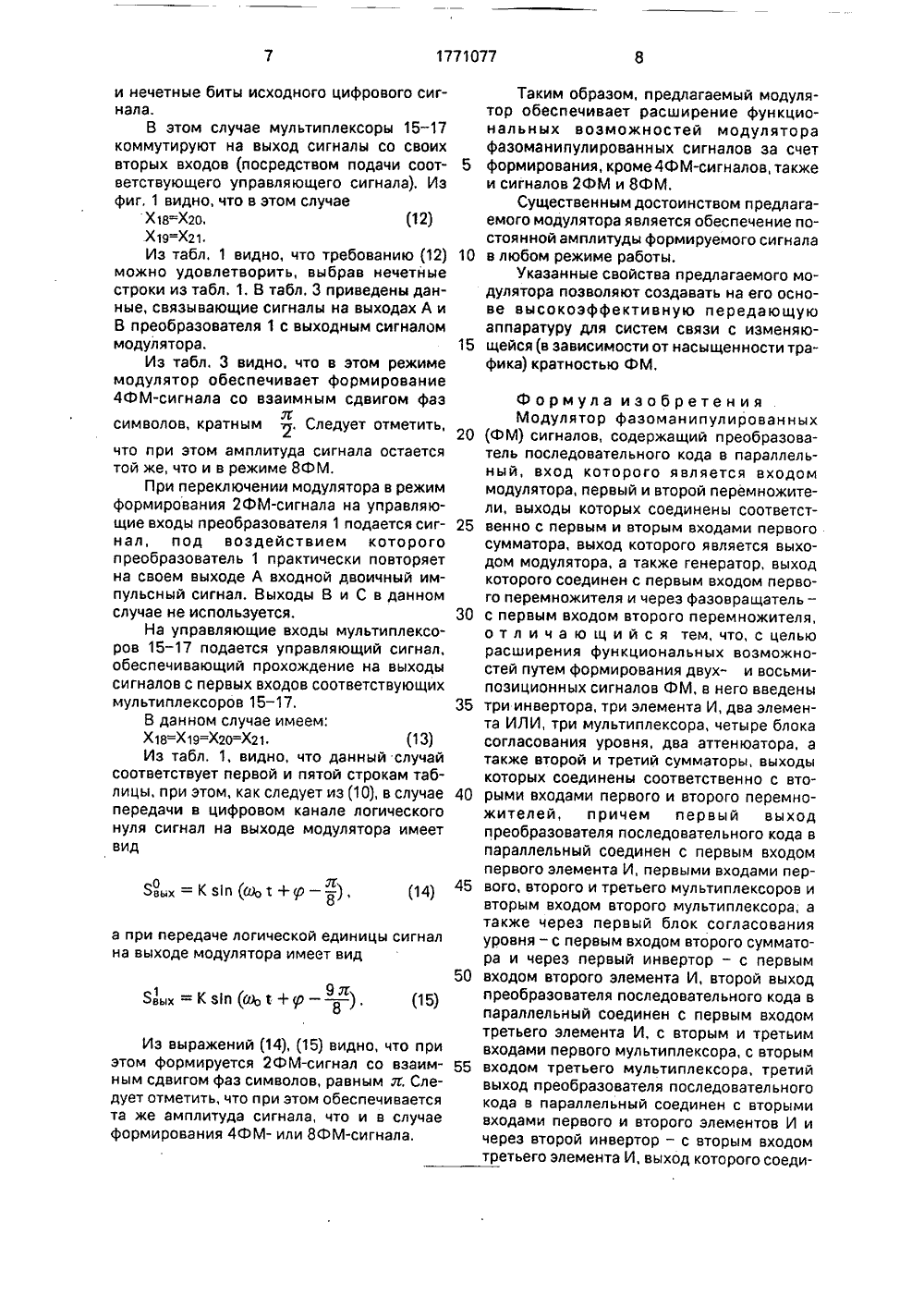

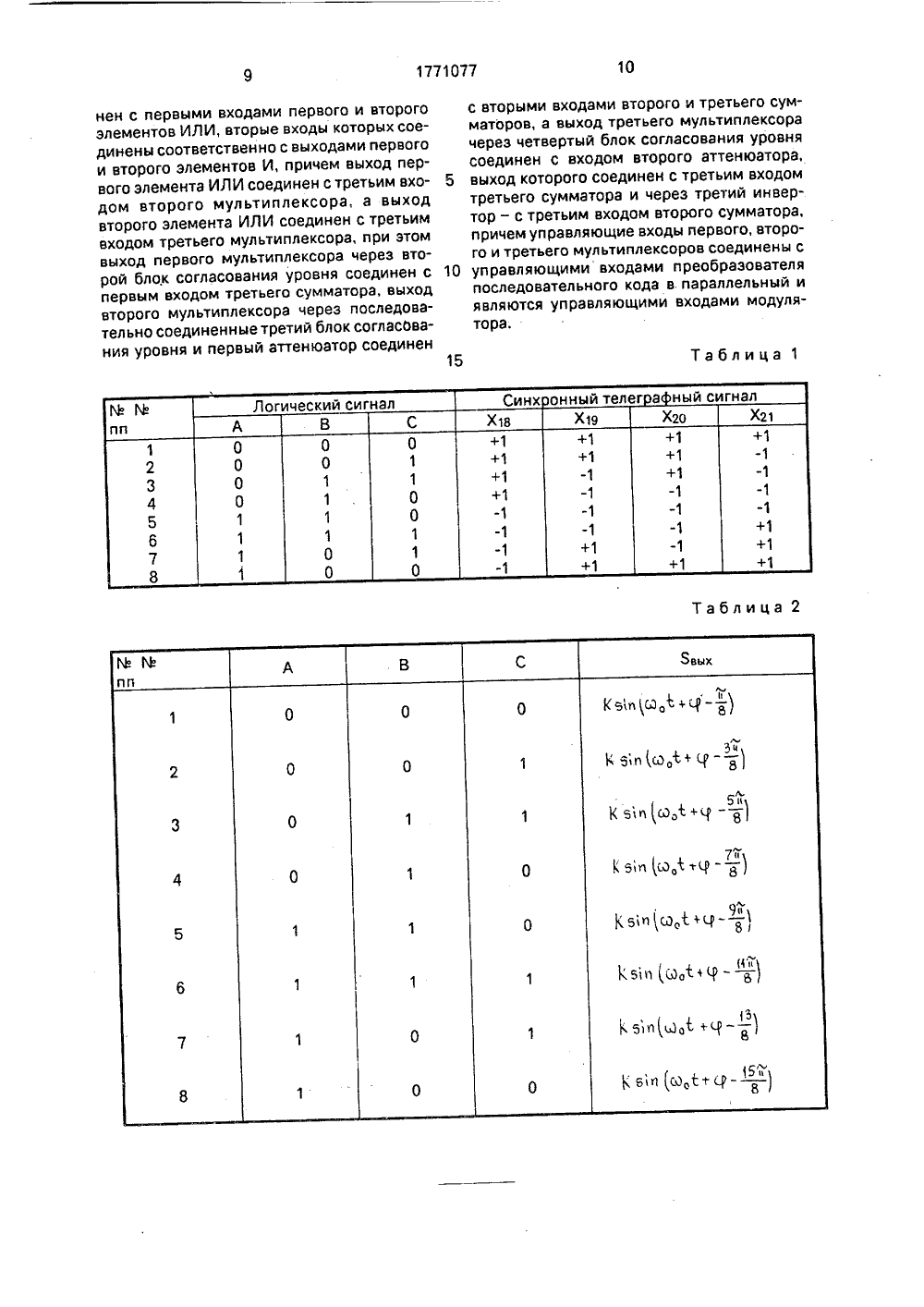

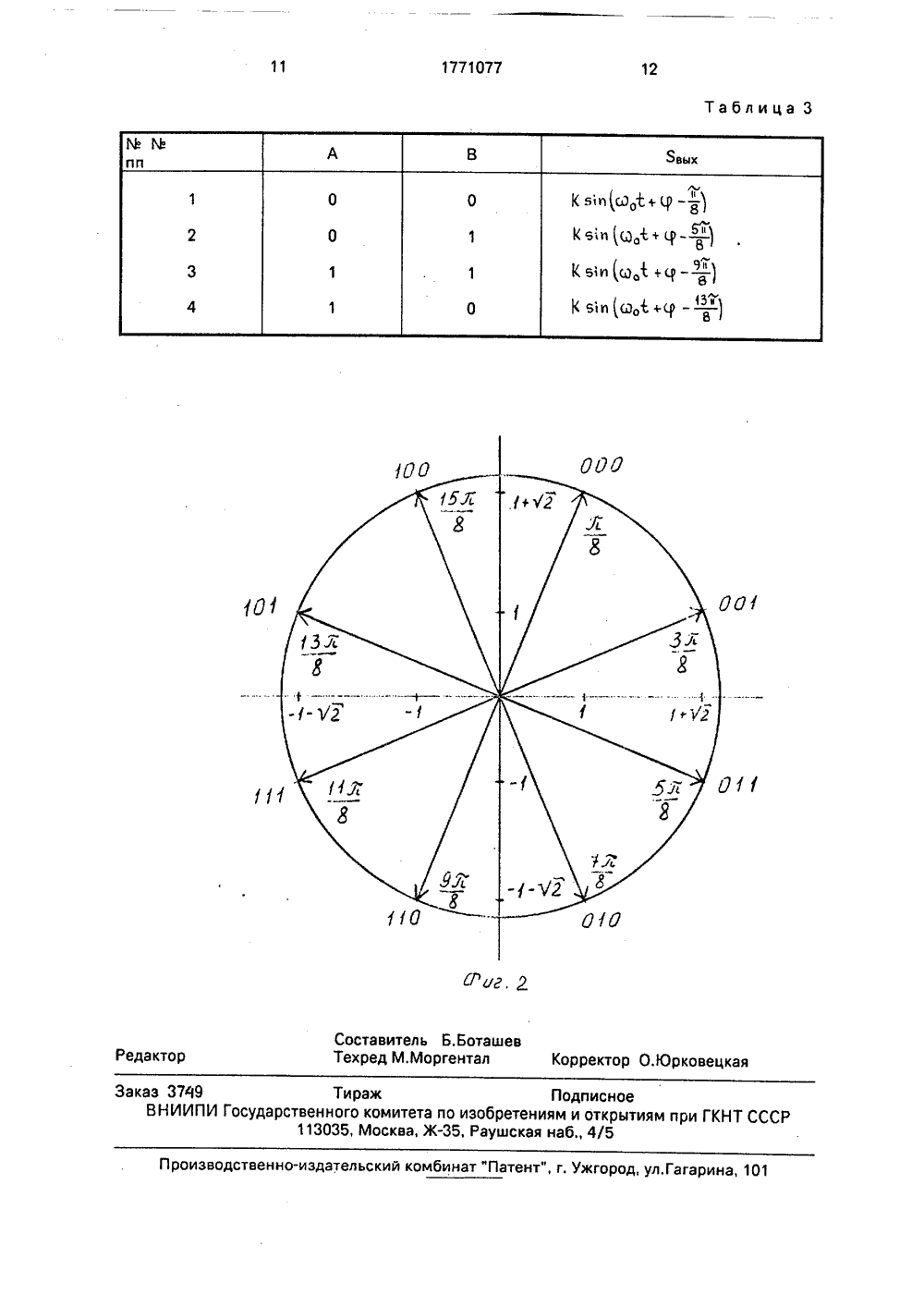

(51) ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ИСАНИЕ РЕТ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Модулятор содержит последовательного к (1) 2 перемножи атора (4, 24, 25), 1 ге щатель (6), 3 инвертоИ (1 О, 11, 12), 2 элем ьтиплексора (15, 16, ия уровня (18, 19, 20 , 23). 1 - 7 - 11 - 14 - 17 - 13 - 16 - 20 - 22-24, 1 - 8 24, 1-15-19-25-3-4 17, 1-10, 1-11, 23-25 л. л, М 39 научно вязиыев, Н вательский.Г, П хоменко Р ФАЗОМЛОВ 54) МОДУЛ ВАННЫХ СИ ИПУЛИ(21) 4901212/09 (22) 09.01,91 (46) 23.10,92, Бю (71) Ростовский институт рэдиос(72) Б. М, Бота Е,С, Шеляпин (56) Беллами Дж Радио и связь, 1 Цифровая телефония. - М,;86, с,313,(57) тель ный сумм зовра мента 3 мул сован ра (22 1 - 12 - 1-18- 15,1: 1 преобразоваода в параллельтеля (2, 3), три нератор (5), 1 фара (7, 8, 9), 3 элеента ИЛИ (13, 14), 17), 4 блока согда), 2 аттенюато 21 - 23 - 9 - 24 - 2 - 4, -12-14, 1-10-13, 1-16, 1 - 17, 1 - 22-25, 5-2, 5-6Изобретение относится к области радиотехники и может быть использовано в аппаратуре систем связи с фазовой манипуляцией (ФМ).Целью изобретения является расширение функциональных возможностей модулятора за счет обеспечения формирования, кроме четырехпозиционных ФМ-сигналов (4 ФМ), также двухпбзиционных (2 ФМ) и восьмипозиционных (8 ФМ) сигналов,На фиг. 1 приведена функциональная схема предлагаемого модулятора; на фиг. 2 - векторная диаграмма, поясняющая принцип работы модулятора.Модулятор фазоманипулированных сигналов содержит преобразователь последовательного кода в параллельный 1, вход которого является входом модулятора, первый и второй перемножители 2 и 3, выходы которых соединены соответственно с первым и вторым входами первого сумматора 4, выход которого является выходом модулятора, а также генератор 5, выход которого соединен с первым входом первого пере- множителя 2 непосредственно и через фазовращатель 6 с первым входом второго перемножителя 3. Модулятор содержит также три инвертора 7, 8 и 9, три элемента И 10, 11 и 12, два элемента ИЛИ 13 и 14, три мультиплексора 15, 16 и 17, четыре блока согласования уровня 18, 19, 20 и 21, два аттенюатора 22 и 23, а также второй и третий сумматоры 24 и 25, выходы которых соединены соответственно с вторыми входами первого и второго перемножителей 2 и 3, Первый выход преобразователя 1 соединен с первым входом первого элемента И 10, первыми входами первого и третьего мульплексоров 15 и 17, первым и вторым входами второго мультиплексора 16, а также через первый блок согласования уровня 18 соединен с первым входом второго сумматора 24 и через первый инвертор 7 с первым входом второго элемента И 11. Второй выход преобразователя 1 соединен с первым входом третьего элемента И 12, с вторым и третьим входами первого мультиплексора 15 и с вторым входом третьего мультиплексора 17, Третий выход преобразователя 1 соединен с вторыми входами первого и второго элементов И 10 и 11 и через второй инвертор 8 с вторым входом третьего элемента И 12, выход которого соединен с первыми входами первого и второго элементов ИЛИ 13 и 14, вторые входы которых соединены соответственно с выходами первого и второго элементов И 10 и 11. Выход первого элемента ИЛИ 13 соединен с третьим входом второго мультиплексора 16, а выход второго элемента ИЛИ 5 10 15 20 25 30 35 40 45 50 55 14 соединен с третьим входом третьего мультиплексора 17, при этом выход первого мультиплексора 15 через второй блок согласования уровня 19 соединен с первым входом третьего сумматора 25, выход второго мультиплексора 16 через третий блок согласования уровня 20 и первый аттенюатор 22 соединен с вторыми входами второго и третьего сумматоров 24 и 25, а выход третьего мультиплексора 17 через четвертый блок согласования уровня 21 соединен с входом второго аттенюатора 23, выход которого соединен с третьим входом третьего сумматора 25 непосредственно и через третий инвертор 9 с третьим входом второго сумматора 24. Управляющие входы первого, второго и третьего мультиплексоров 15, 16 и 17 объединены, соединены с управляющими входами преобразователя 1 и являются управляющими входами модулятора,Аттенюаторы 22, 23 имеют коэффициЛ;ент передачи ,Каждый из мультиплексоров 15 - 17 выполнен таким образом, что в режиме формирования 2 ФМ сигнала на выход коммутируется сигнал с их первых входов, в режиме 4 ФМ - с вторых и в режиме 8 ФМ - с третьих входов. Выбор режима осуществляется подачей соответствующего сигнала на объединенные управляющие входы мультиплексоров 15-17,Модулятор фазоманипулированн ых сигналов работает следующим образом.На вход преобразователя 1 поступает цифровой сигнал в виде двоичной импульсной последовательности,В режиме формирования 8 ФМ сигнала преобразователь 1 формирует на своих выходах А, В и С двоичные импульсные последовательности, скорость каждой из которых составляет 1/3 от скорости сигнала на входе преобразователя 1. При этом сигналы на выходах АВ и С соответствуют трем последовательным битам исходного (суммарного) сигнала. Режим формирования параллельного потока, состоящего из трех двоичных сигналов (трибит), задается соответствующим сигналом на управляющих входах преобразователя 1,Сигнал А с первого выхода преобразователя 1 поступает на вход элемента И 10,на другой вход которого поступает сигнал Сс третьего выхода преобразователя 1, такимобразом на выходе элемента И 10 формируется сигнал:Х 10=Ад С, (1)гдеЛ - символ логического умножения (коньюн кция), 1771077Аналогичным образом на выходах элементов И 11 и 12 формируются сигналы соответственно;Х 11=АИС, (2) Х 12=Вл С, (3) где черта над буквой обозначает операцию логической инверсии.На соответствующие входы элементов ИЛИ 13 и 14 поступают сигналы с выходов элементов И 10-12, На выходах элементов ИЛИ 13 и 14 формируются сигналы соответственно:Х 1 з=Ал СчВл С, (4) Х 14=Ал СчВл С, (5) где ч - символ логической суммы (дизъюнкция).В режиме формирования 8 ФМ сигнала мультиплексоры 15, 16 и 17 коммутируют на свои выходы (под воздействием сигнала на их управляющих входах) сигналы, соответствующие импульсным последовательностям на их третьих входах (нижних по схеме фиг. 1), Так, на выходе мультиплексора 15 формируется сигнал В, на выходе мультиплексора 16 - сигнал Х 1 з и на выходе мультиплексора 17 - сигнал Х 14,Сигналы с выходов мультиплексоров 15-17, а также сигнал А с первого выхода преобразователя 1 поступают на входы соответствующих блоков согласования уровня 18 - 21, которые преобразуют двоичные импульсные последовательности в синхронные телеграфные сигналы, При этом логической единице на входе каждого блока согласования уровня 18 - 21 соответствует напряжение на выходе, равное по величине минус 1, а логическому нулю соответствует напряжение плюс 1.Пользуясь выражениями (4) и(5), а также приведенным алгоритмом работы блоков согласования уровня 18 - 21, составлена таблица истинности (табл, 1), в которой входными сигналами являются импульсные двоичные сигналы А, В, С на соответствующих выходах преобразователя 1, а выходными - синхронные телеграфные сигналы Х 18, Х 19, Хго, Х 21 с выходов соответствующих блоков согласования уровня 18-21,Как видно из фиг, 1, на сумматор 24 поступает сигнал Х 18, а также сигнал Хго, прошедший через аттенюатор 22 с коэффи 1 Г 2циентом передачи -2-, и сигнал Х 21, прошедший через аттенюатор 23 и инвертор 9. Следовательно, сигнал Х 24 на выходе сумматора 24 можно записать в видеХг 4=Х 18+ -1 г Хго- -1 г Хг 1.Г 2 /2(6)Аналогично, сигнал Х 25 на выходе сумматора 25 имеет вид Х 25=Х 19+ -у. Х 20+ -у. Х 21.А Л(7)Генератор 5 формирует на своем выходе напряжение вида5 Яс= сов(аь т + р), (8)где ао - несущая частота ФМ-сигнала;р- начальная фаза.Фазовращатель 6 осуществляет поворот фазы сигнала Яс на 90, при этом сигнал 10 на выходе фазовращателя 6 принимает видЯ =в 1 п (в с+у). (9) После умножения сигнала Х 24 на сигналЯс в перемножителе 2 и сигнала Х 25 на сигнал Яв в перемножителе 3, а также суммиро вания в сумматоре 4 полученных сигналов,на выходе сумматора 4 сигнал имеет видЯвых=Яс Х 24+ЯсХ 25=Ч 2(10) 25 Подставляя значения Х 1 в, Х 19, Х 2 о, Х 21 изтабл, 1 и выполняя тригонометрические преобразования, получим данные, приведенные в табл. 2, связывающие трибит на выходе преобразователя 1 с сигналом на 30 выходе модулятора Явых,Величина К в табл. 2 представляет собсйамплитудный множитель, возникающий при преобразовании выражения (10);Результаты, приведенные в табл. 2,представлены на фиг. 2 в виде векторной диаграммы, где с внешней стороны окруж ности указаны передаваемые комбинациисимволов(трибиты), а с внутренней стороны окружности указаны значения фазы сигналов в соответствии с табл, 2. Из фиг. 2 видно, что реализуемый алгоритм модуляции обес печивает получение сигнального алфавита ввиде кода Грея, который гарантирует минимизацию средней вероятности битовой ошибки. Фазовый сдвиг соседних символовЛсоставляет 4.В режиме формирования 4 ФМ сигналапреобразователь 1, на управляющие входы которого подан сигнал переключения в режим 4 ФМ, формирует двоичные импульс ные последовательности только на выходахА и В, а выход С в данном случае не используется, При этом сигналы на выходах А и В представляют собой соответственно четные(14) и нечетные биты исходного цифрового сигнала.В этом случае мультиплексоры 15-17 коммутируют на выход сигналы со своих вторых входов (посредством подачи соответствующего управляющего сигнала). Из фиг. 1 видно, что в этом случаеХ 1 В=Х 2 О, (12) Х 19=Х 21Из табл, 1 видно, что требованию (12) можно удовлетворить, выбрав нечетные строки из табл. 1. В табл. 3 приведены данные, связывающие сигналы на выходах А и В преобразователя 1 с выходным сигналом модулятора.Из табл. 3 видно, что в этом режиме модулятор обеспечивает формирование 4 ФМ-сигнала со взаимным сдвигом фазЛсимволов, кратным . Следует отметить, что при этом амплитуда сигнала остается той же, что и в режиме 8 ФМ.При переключении модулятора в режим формирования 2 ФМ-сигнала на управляющие входы преобразователя 1 подается сигнал, под воздействием которого преобразователь 1 практически повторяет на своем выходе А входной двоичный импульсный сигнал. Выходы В и С в данном случае не используется.На управляющие входы мультиплексоров 15 - 17 подается управляющий сигнал, обеспечивающий прохождение на выходы сигналов с первых входов соответствующих мультиплексоров 15-17.В данном случае имеем:Х 18=Х 19=Х 20=Х 21. (13) Из табл. 1, видно, что данный случай соответствует первой и пятой строкам таблицы, при этом, как следует из (10), в случае передачи в цифровом канале логического нуля сигнал на выходе модулятора имеет вид а при передаче логической единицы сигнална выходе модулятора имеет вид Явых = К 3 и (жо т + ф -- ), (1 5)9 л8 Из выражений (14), (15) видно, что при этом формируется 2 ФМ-сигнал со взаимным сдвигом фаз символов, равным л. Следует отметить, что при этом обеспечивается та же амплитуда сигнала, что и в случае формирования 4 ФМ- или 8 ФМ-сигнала. 20 25 30 35 40 45 50 55 Таким образом, предлагаемый модулятор обеспечивает расширение функциональных возможностей модулятора фазоманипулированных сигналов за счет формирования, кроме 4 ФМ-сигналов, также и сигналов 2 ФМ и 8 ФМ.Существенным достоинством предлагаемого модулятора является обеспечение постоянной амплитуды формируемого сигнала в любом режиме работы.Указанные свойства предлагаемого модулятора позволяют создавать на его основе высокоэффективную передающую аппаратуру для систем связи с изменяющейся (в зависимости от насыщенности трафика) кратностью ФМ,Ф ар мула из о бр ете н и я Модулятор фазоманипулированных (ФМ) сигналов, содержащий преобразователь последовательного кода в параллельный, вход которого является входом модулятора, первый и второй перемножители, выходы которых соединены соответственно с первым и вторым входами первого сумматора, выход которого является выходом модулятора, а также генератор, выход которого соединен с первым входом первого перемножителя и через фазовращатель - с первым входом второго перемножителя, о т л и ч а ю гц и й с я тем, что, с целью расширения функциональных возможностей путем формирования двух- и восьми- позиционных сигналов ФМ, в него введены три инвертора, три элемента И, два элемента ИЛИ, три мультиплексора, четыре блока согласования уровня, два аттенюатора, а также второй и третий сумматоры, выходы которых соединены соответственно с вторыми входами первого и второго перемножителей, причем первый выход преобразователя последовательного кода в параллельный соединен с первым входом первого элемента И, первыми входами первого, второго и третьего мультиплексоров и вторым входом второго мультиплексора, а также через первый блок согласования уровня - с первым входом второго сумматора и через первый инвертор - с первым входом второго элемента И, второй выход преобразователя последовательного кода в параллельный соединен с первым входом третьего элемента И, с вторым и третьим входами первого мультиплексора, с вторым входом третьего мультиплексора, третий выход преобразователя последовательного кода в параллельный соединен с вторыми входами первого и второго элементов И и через второй инвертор - с вторым входом третьего элемента И, выход которого соеди1771077 10 15 Таблица 1 Таблица 2 нен с первыми входами первого и второго элементов ИЛИ, вторые входы которых соединены соответственно с выходами первого и второго элементов И, причем выход первого элемента ИЛИ соединен с третьим входом второго мультиплексора, а выход второго элемента ИЛИ соединен с третьим входом третьего мультиплексора, при этом выход первого мультиплексора через второй блок согласования уровня соединен с первым входом третьего сумматора, выход второго мультиплексора через последовательно соединенные третий блок согласования уровня и первый аттенюатор соединен с вторыми входами второго и третьего сумматоров, а выход третьего мультиплексора через четвертый блок согласования уровня соединен с входом второго аттенюатора, 5 выход которого соединен с третьим входомтретьего сумматора и через третий инвертор - с третьим входом второго сумматора, причем управляющие входы первого, второго и третьего мультиплексоров соединены с 10 управляющими входами преобразователяпоследовательного кода в. параллельный и являются управляющими входами модулятора.1771077 12 Таблица 3 едак роизводственно-издательский комбинат "Патент", г. Ужгород, ул.Гагарина, 101 акаэ 3719 ВНИИПИ Гос Составитель Б.БоташевТехред М,Моргентал Корректор О.Юрковецк Тираж Подписноевенного комитета по изобретениям и открытиям при ГКНТ СССР 113035, Москва, Ж, Раушская наб., 4/5

СмотретьЗаявка

4901212, 09.01.1991

РОСТОВСКИЙ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ РАДИОСВЯЗИ

БОТАШЕВ БОРИС МУССАЕВИЧ, ПАРХОМЕНКО НИКОЛАЙ ГРИГОРЬЕВИЧ, ШЕЛЯПИН ЕВГЕНИЙ СЕРГЕЕВИЧ

МПК / Метки

МПК: H04L 27/20

Метки: модулятор, сигналов, фазоманипулированных

Опубликовано: 23.10.1992

Код ссылки

<a href="https://patents.su/6-1771077-modulyator-fazomanipulirovannykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Модулятор фазоманипулированных сигналов</a>

Предыдущий патент: Устройство для приема биимпульсных сигналов

Следующий патент: Предварительный видеоусилитель для передающей телевизионной камеры

Случайный патент: Крепь для проходки вертикальных горных выработок