Резервированный усилитель амплитудно-модулированных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1764203

Авторы: Климентов, Коморников, Лихачев, Назаренко, Юшников

Текст

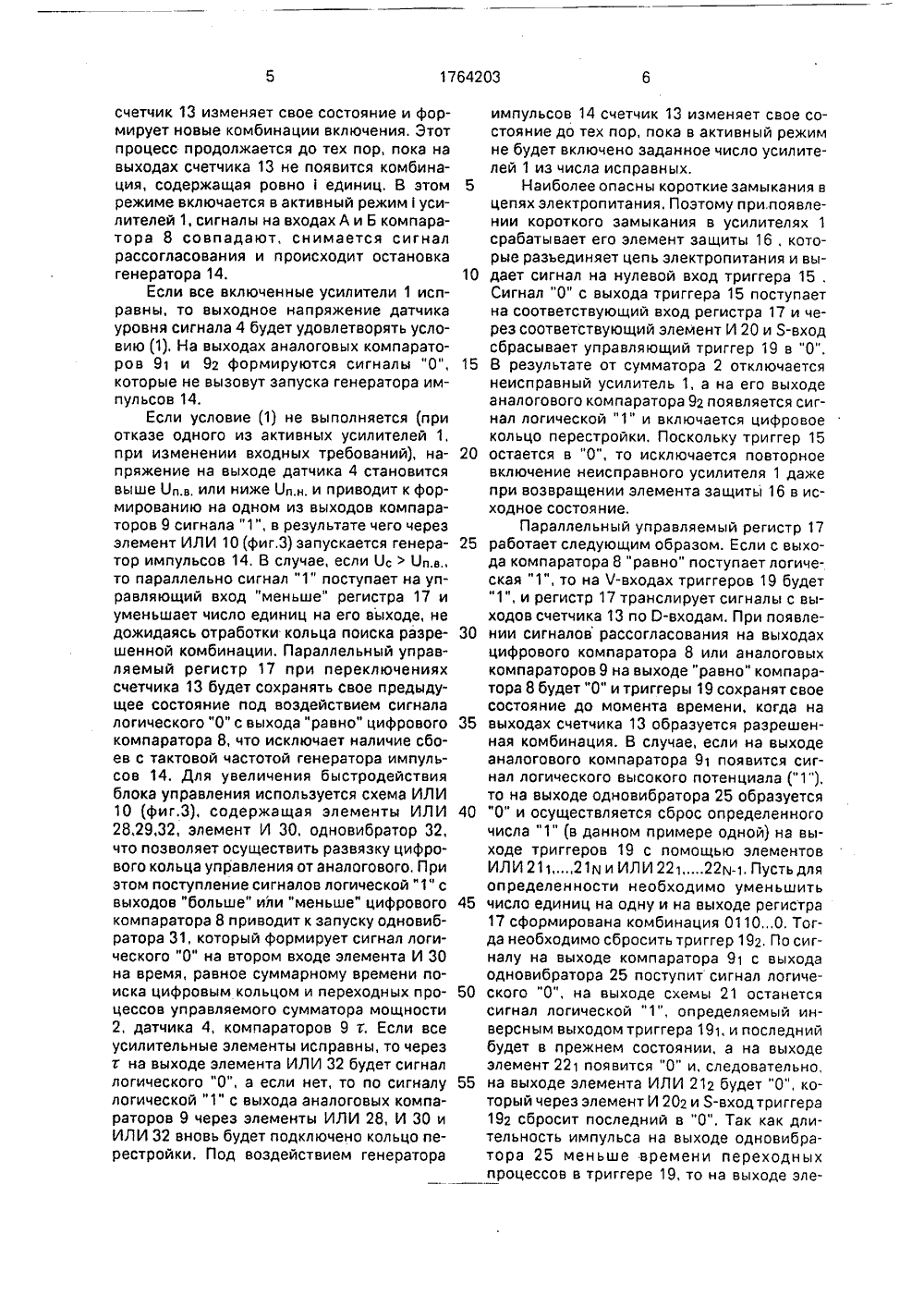

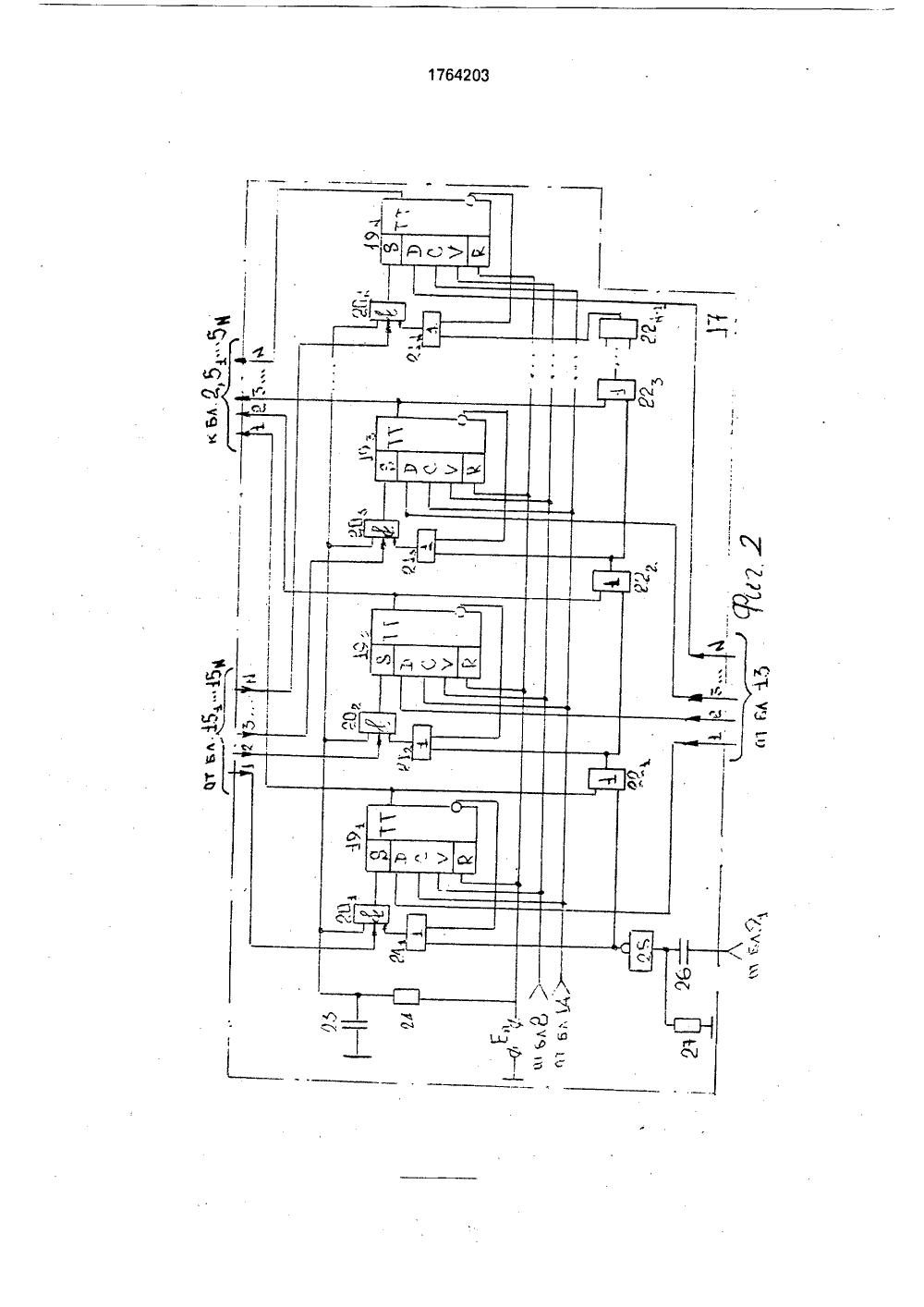

(51) 5 Н ОМУ С ЕЛЬСТВУ В Дь ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИПРИ ГКЧТ СССР ОПИСАНИЕ ИЗОБРЕ(72) А,М,Лихачев, В,И,Климентов, П,М,Коморников, В,Н,Назаренко и С,И.Юшников (56) Авторское свидетельство СССР М 1347200, кл, Н 05 К 10/00, 1983.Авторское свидетельство СССР % 1378096, кл. Н 05 К 10/00, 1986,(54) РЕЗЕРВИРОВАННЫЙ УСИЛИТЕЛЬ АМ ПЛ ИТУД Н О-МОДУЛ И РО ВАН Н ЫХ СИ ГНАЛОВ(57) Сущность изобретения: устройство содержит усилительные блоки (1), управляемый сумматор мощности (2), резистивные делители напряжения (31 и 32), датчик уровУ 8 я ня сигнала (4), ключи (5), нагрузочный элемент (6), преобразователь кодов (7), цифровой компаратор (8), аналоговые компаратора (91 и 92), элемент ИЛИ (10), дешифратор (11), цифра-аналоговый преобразователь (12), счетчик (13), генератор импульсов (14), триггеры (15), элементы защиты (16), параллельный управляемый регистр (17), масштабирующий резистор (1 81), зарядный конденсатор (182), триггеры (19), элементы И(20), элементы ИЛИ(21), элементы ИЛИ (22), конденсаторы (23,26), резисторы (24,27), одновибратор (25), элементы ИЛИ (28,29,32), элемент И (30), одновибратор (31), 1 - 2 - 4 - 9 - 10 - 14 - 13 - 17 - 1, 13 - 7-8- 10, 1-16-5, 16-15-17, 17-5, 11-12-3-9, 3 ил.Изобретение относится к автоматике иможет быть использовано в усилительныхустройствах повышенной надежности,Цель изобретения - повышение устойчивости и быстродействия процесса резервирования.На фиг,1 представлена электрическая структурная схема резервированного усилителя амплитудно-модулированных сигналов; на фиг.2,3 - электрическиепринципиальные схемы параллельного управляемого регистра и элемента ИЛИ 10.Резервированный усилитель амплитудно-модулированных сигналов содержит М усилительных блоков (УБ) 1, управляемый сумматор мощности 2, резистивный делитель напряжения 31 и 32, датчик уровня сигналов 4, М ключей 5, нагрузочный элемент 510 15 6, преобразователь кода 7, цифровой компаратор 8, два аналоговых компаратора 91 и 2092, элемент ИЛИ 10, дешифратор 11, цифроа налоговьчй преобразователь 12, счетчик 13,генератор импульсов 14, М триггеров 15, йэлементов защиты 16, параллельный управляемый регистр 17, масштабирующий резистор 181, зарядный конденсатор 182, йтриггеров 19, И элементов И 20, К элементов ИЛИ 21, Кэлементов ИЛИ 22, конденсаторы 23 и 26, сопротивления 24 и 27,одновибратор 25, элементы ИЛИ 28, 29, элемент И 30, одновибратор 31, элемент ИЛИ32,Резервированный усилитель амплитудно-модулированных сигналов работает следующим образом, 35При включении питания единичные входы триггеров 15 и Я-входы триггеров 19 через разряженные конденсатор 182 иконденсатор 23 регистра 17 соответственнооказываются кратковременно подключенными к общей шине, в результате чего всетриггеры 15 устанавливаются в "1", а триггера 19 - в "0", По мере заряда конденсаторов через зарядные сопротивления 18, и 24триггеры 15 и 19 подготавливаются к управлению по нулевым входам.На вход устройства в двоичном коде накодовую шину задания мощности поступаеткоманда на включение усилителей 1, которые обеспечивают заданную выходную 50мощность резервированного усилителя амплитудно-модулированных сигналов, Числовключенных усилителей 1 может лежать впределах 1= М - Я, т,е. в любом случаеЯ усилителей 1 находится в ненагруженном 55резерве. Сигнал 1-й команды управления поступает на е входов цифрового компаратора 8 и п входов дешифратора 11. Повыходному сигналу дешифратора 11, подаваемому через цифроаналоговый преобра зователь 12, резистивный делитель напряжения 31 и 32 на входы компараторов 91 и 92,формируется пороговое напряжения, удовлетворяющее неравенству Оп.н.ОсОп.в Оп.в, - О п.нОс)Оп,в. = КОс+ Ос/2(2) Счетчик 13 после включения напряжения питания может находиться в одном из й2 состояний, При этом на его И выходах формируется комбинация "1" и "0". Сигналы с выхода счетчика поступают на вход параллельного управляемого регистра 17, на и входов управления которого с прямых выходов триггера 15 подаются сигналы "1", Сигналы "1" с выходов счетчика поступают на входы преобразователя кода 7 и не ретранслируются регистром 17 до тех пор, пока на выходе "равно" цифрового компаратора 8 не появится сигнал логической "1", по которому будет осуществлена запись состояния счетчика 13 в триггеры 19 регистра 17. На выходе последнего образуются сигналы "1", подаваемые на входы управления сумматора мощности 2 и ключей 5. По этим сигналам выполняется необходимая коммутация в управляемом сумматоре мощности 2, подается напряжение питания на усилители 1 и подключаются выходы усилителей 1 к нагрузке. Таким образом, осуществляется защита от переключений управляемого сумматора мощности 2 в момент перестройки счетчика 13, которые могут срывать колебания на выходе сумматора мощности 2,На выходе преобразователя кода 7 формируется число, соответствующее числу активных (включенных) усилителей 1 в двоичном коде, которое поступает на входы цифрового компаратора 8, Если число их равно заданному, то сигналы рассогласования на выходах блока 8 отсутствуют. В противном случае эти сигналы через элемент ИЛИ 10 запускают генератор импульсов 14. Под воздействием импульсов последнего где Ос - напряжение, соответствующее выходному напряжению при включении УБ 1,Если учесть, что Ос щвх пропорционально включению К = Й - Я усилителей 1 и равно К Ось где Ос - стробирующее напряжение, пропорциональное включению одного усилителя 1, то сопротивления 31 и 32 выбираются так, чтобы при включении К УБ 1 выполнялось соотношения5 10 15 20 30 35 40 45 50 55 счетчик 13 изменяет свое состояние и формирует новые комбинации включения, Этот процесс продолжается до тех пор, пока на выходах счетчика 13 не появится комбинация, содержащая ровноединиц, В этом режиме включается в активный режим усилителей 1, сигналы на входах А и Б компаратора 8 совпадают, снимается сигнал рассогласования и происходит остановка генератора 14.Если все включенные усилители 1 исправны, то выходное напряжение датчика уровня сигнала 4 будет удовлетворять условию (1), На выходах аналоговых компараторов 91 и 92 формируются сигналы "0", которые не вызовут запуска генератора импульсов 14.Если условие (1) не выполняется (при отказе одного из активных усилителей 1, при изменении входных требований), напряжение на выходе датчика 4 становится выше Оп.в. или ниже Оп.н. и приводит к формированию на одном из выходов компараторов 9 сигнала "1", в результате чего через элемент ИЛИ 10 (фиг,З) запускается генератор импульсов 14, В случае, если ОсОп.в., то параллельно сигнал "1" поступает на управляющий вход "меньше" регистра 17 и уменьшает число единиц на его выходе, не дожидаясь отработки кольца поиска разрешенной комбинации. Параллельный управляемый регистр 17 при переключениях счетчика 13 будет сохранять свое предыдущее состояние под воздействием сигнала логического "0" с выхода "равно" цифрового компаратора 8, что исключает наличие сбоев с тактовой частотой генератора импульсов 14, Для увеличения быстродействия блока управления используется схема ИЛИ 10 (фиг.З), содержащая элементы ИЛИ 28,29,32, элемент И 30, одновибратор 32, что позволяет осуществить развязку цифрового кольца управления от аналогового, При этом поступление сигналов логической "1" с выходов "больше" или "меньше" цифрового компаратора 8 приводит к запуску одновибратора 31, который формирует сигнал логического "0" на втором входе элемента И 30 на время, равное суммарному времени поиска цифровым кольцом и переходных процессов управляемого сумматора мощности 2, датчика 4, компараторов 9 т, Если все усилительные элементы исправны, то через т на выходе элемента ИЛИ 32 будет сигнал логического "0", а если нет, то по сигналу логической "1" с выхода аналоговых компараторов 9 через элементы ИЛИ 28, И 30 и ИЛИ 32 вновь будет подключено кольцо перестройки. Под воздействием генератора импульсов 14 счетчик 13 изменяет свое состояние до тех пор, пока в активный режим не будет включено заданное число усилителей 1 из числа исправных,Наиболее опасны короткие замыкания в цепях электропитания, Поэтому при.появлении короткого замыкания в усилителях 1 срабатывает его элемент защиты 16, которые разъединяет цепь электропитания и выдает сигнал на нулевой вход триггера 15, Сигнал "0" с выхода триггера 15 поступает на соответствующий вход регистра 17 и через соответствующий элемент И 20 и Я-вход сбрасывает управляющий триггер 19 в "0", В результате от сумматора 2 отключается неисправный усилитель 1, а на его выходе аналогового компаратора 92 появляется сигнал логической "1" и включается цифровое кольцо перестройки. Поскольку триггер 15 остается в "0", то исключается повторное включение неисправного усилителя 1 даже при возвращении элемента защиты 16 в исходное состояние,Параллельный управляемый регистр 17 работает следующим образом, Если с выхода компаратора 8 "равно" поступает логическая "1", то на Ч-входах триггеров 19 будет "1", и регистр 17 транслирует сигналы с выходов счетчика 13 по О-входам. При появлении сигналов рассогласования на выходах цифрового компаратора 8 или аналоговых компараторов 9 на выходе "равно" компаратора 8 будет "0" и триггеры 19 сохранят свое состояние до момента времени, когда на выходах счетчика 13 образуется разрешенная комбинация. В случае, если на выходе аналогового компаратора 9 появится сигнал логического высокого потенциала ("1"), то на выходе одновибратора 25 образуется "0" и осуществляется сброс определенного числа "1" (в данном примере одной) на выходе триггеров 19 с помощью элементов ИЛИ 21121 и и ИЛ И 22122 и, Пусть для определенности необходимо уменьшить число единиц на одну и на выходе регистра 17 сформирована комбинация 0110,0, Тогда необходимо сбросить триггер 192, По сигналу на выходе компаратора 9 с выхода одновибратора 25 поступитсигнал логического "0", на выходе схемы 21 останется сигнал логической "1", определяемый инверсным выходом триггера 191, и последний будет в прежнем состоянии, а на выходе элемент 221 появится "0" и, следовательно, на выходе элемента ИЛИ 212 будет "0", который через элемент И 202 и Я-входтриггера 192 сбросит последний в "0", Так как длительность импульса на выходе одновибратора 25 меньше времени переходных процессов в триггере 19, то на выходе эле 1764203мента ИЛИ 222 "0" не появится и сброшен будет только один триггер 192, Остальные триггеры останутся в исходном состоянии. При необходимости отключения двух усилителей 1 задача решается выбором длительности импульса на выходе блока 25 больше времени переходных процессов в одном триггере 19 и меньше суммарного времени переходных процессов в двух триггерах 19.Таким образом, предлагаемое техническое решение повышает быстродействие блока управления, не приводит к появлению сбоев с тактовой частотой в формировании выходного напряжения при переключениях усилителей 1 (что не приводит к перерывам в процессе обеспечения связи) и исключает возможность появления сигнала, у которого выходное напряжение превышает допустимое. Формула изобретения Резервированный усилитель амплитудно-модулированных сигналов, содержащий и усилительных блоков, информационные выходы которых соединены с информационными входами управляемого сумматора мощности, к выходу которого подключены вход датчика уровня сигнала и нагрузочный элемент, выход питания каждого из усилительных блоков через элемент защиты и соединенный с ним последовательно ключ соединен с шиной нулевого потенциала, выходы индикации короткого замыкания элементов защиты соединены с нулевыми входами соответствующих триггеров, единичные входы которых подключены через масштабирующий резистор к шине опорного потенциала и через зарядный конденсатор к шине нулевого потенциала, первый аналоговый компаратор, неинвертирующий вход которого соединен с выходом датчика уровня сигнала, инвертирующий вход - к выходу цифроаналогового преобразователя, а выход - с первым входом элемента ИЛИ, выход которого соединен с запускающим входом генератора импульсов, выход которого соединен с входом счетчика, цифровой компаратор, первый вход которого соединен с выходом преобразователя кодов, а второй - с кодовой шиной задания 5 выходной мощности и через дешифратор свходом цифроаналогового преобразователя, выход которого соединен с инвертирующим входом первого аналогового компаратора, выходы "Больше" и "Меньше" 10 цифрового компаратора соединены соответственно с вторым и третьим входами элемента ИЛИ, о т л и ч а ю щ и й с я тем, что, с целью повышения устойчивости и быстродействия процесса резервирова ния, в него введены второй аналоговыйкомпаратор, резистивный делитель напряжения и параллельный управляемый регистр, при этом инвертированный вход второго аналогового компаратора соединен 20 с неинвертированным входом первого аналогового компаратора, между инвертированным входом первого аналогового компаратора и шиной нулевого потенциала включен резистивный делитель напряже ния, средний вывод которого соединен снеинвертированным входом второго аналогового компаратора, выход которого соединен с четвертым входом элемента ИЛИ, выход генератора импульсов соединен с 30 синхронизирующим входом параллельногоуправляемого регистра, управляющий вход уменьшения кода которого соединен с выходом первого аналогового компаратора, управляющий вход сохранения кода соединен 35 с выходом цифрового компаратора, а группауправляющих входом поразрядного сброса параллельного управляющего регистра соединена с выходами соответствующих триггеров, и разрядных выходов счетчика 40 соединены поразрядно с установочнымивходами параллельного управляющего регистра, выходы п разрядов которого соединены с управляющими входами соответствующих элементов защиты и с 45 управляющими входами коммутации управляемого сумматора мощности,1764203 УЬЛ Бл 14 едактор Г. Бельс ил юков аз 3465 Тираж Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СС 113035, Москва, Ж, Раушская наб., 4/5 оизводственно-издательский комбинат "Патент", г. Ужгород, ул, Гагарина, 101 Составитель В. Клим Техред М.Моргентал в Корректор

СмотретьЗаявка

4857882, 06.08.1990

ВОЕННАЯ КРАСНОЗНАМЕННАЯ АКАДЕМИЯ СВЯЗИ ИМ. С. М. БУДЕННОГО

ЛИХАЧЕВ АЛЕКСАНДР МИХАЙЛОВИЧ, КЛИМЕНТОВ ВАЛЕРИЙ ИВАНОВИЧ, КОМОРНИКОВ ПАВЕЛ МАРКОВИЧ, НАЗАРЕНКО ВАЛЕРИЙ НИКОЛАЕВИЧ, ЮШНИКОВ СЕРГЕЙ ИВАНОВИЧ

МПК / Метки

МПК: H05K 10/00

Метки: амплитудно-модулированных, резервированный, сигналов, усилитель

Опубликовано: 23.09.1992

Код ссылки

<a href="https://patents.su/6-1764203-rezervirovannyjj-usilitel-amplitudno-modulirovannykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Резервированный усилитель амплитудно-модулированных сигналов</a>

Предыдущий патент: Трехканальное мажоритарно-резервированное устройство

Следующий патент: Устройство для рихтовки преимущественно однонаправленных выводов радиоэлементов

Случайный патент: Устройство для вакуумного отбора масла