Устройство для вычисления логарифмической функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1596323

Авторы: Арсени, Бородянский, Браиловский, Волков, Сурженко

Текст

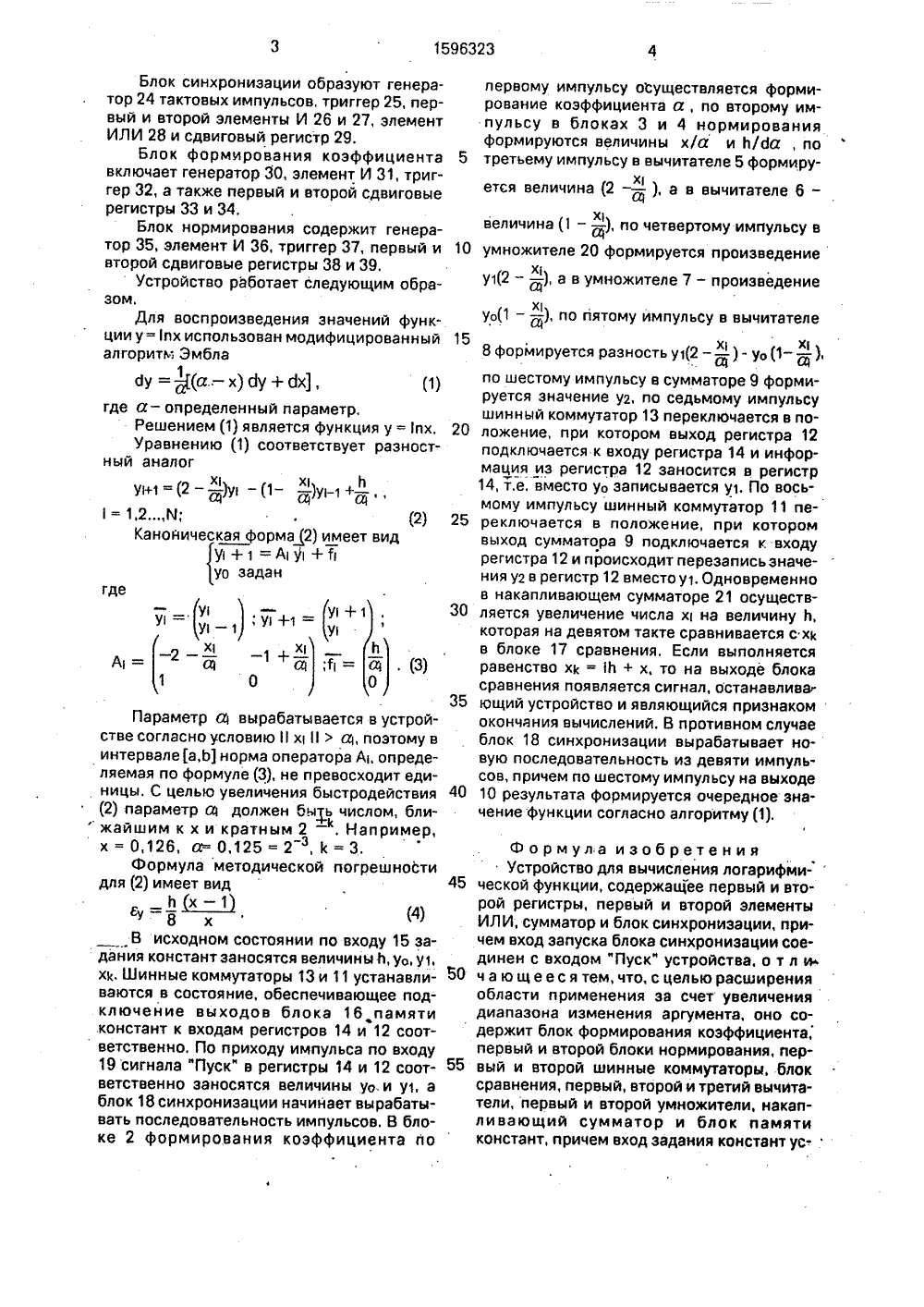

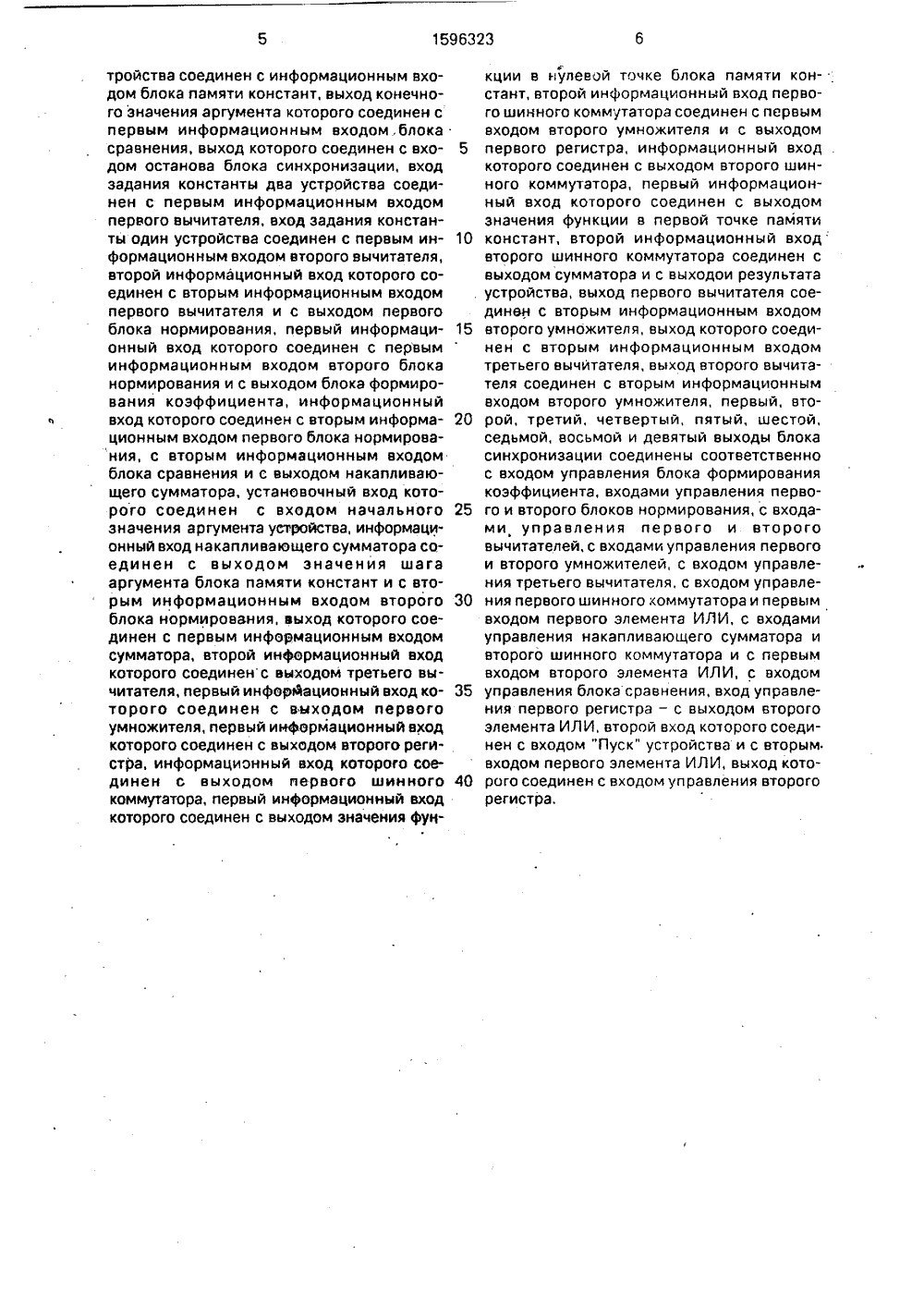

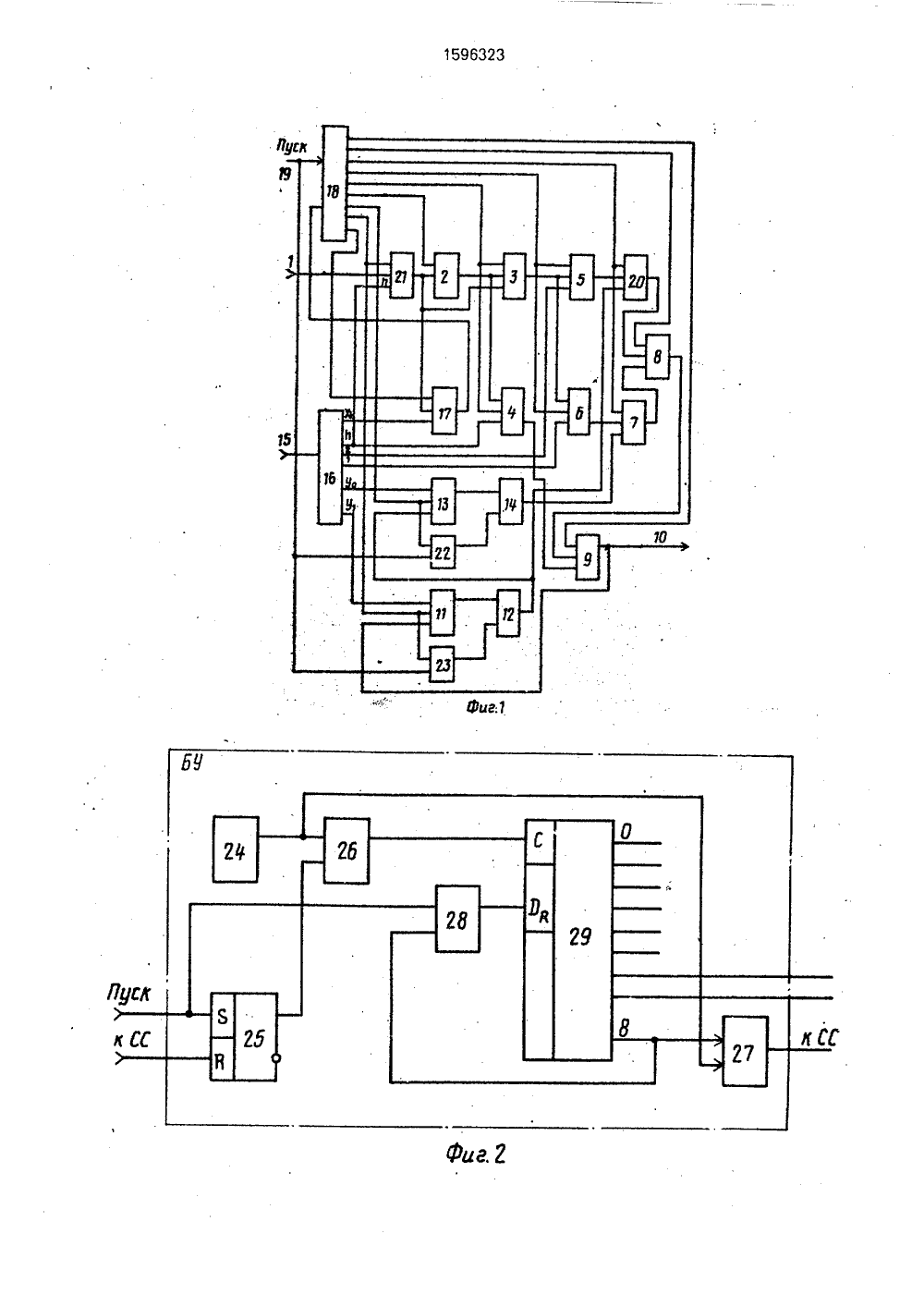

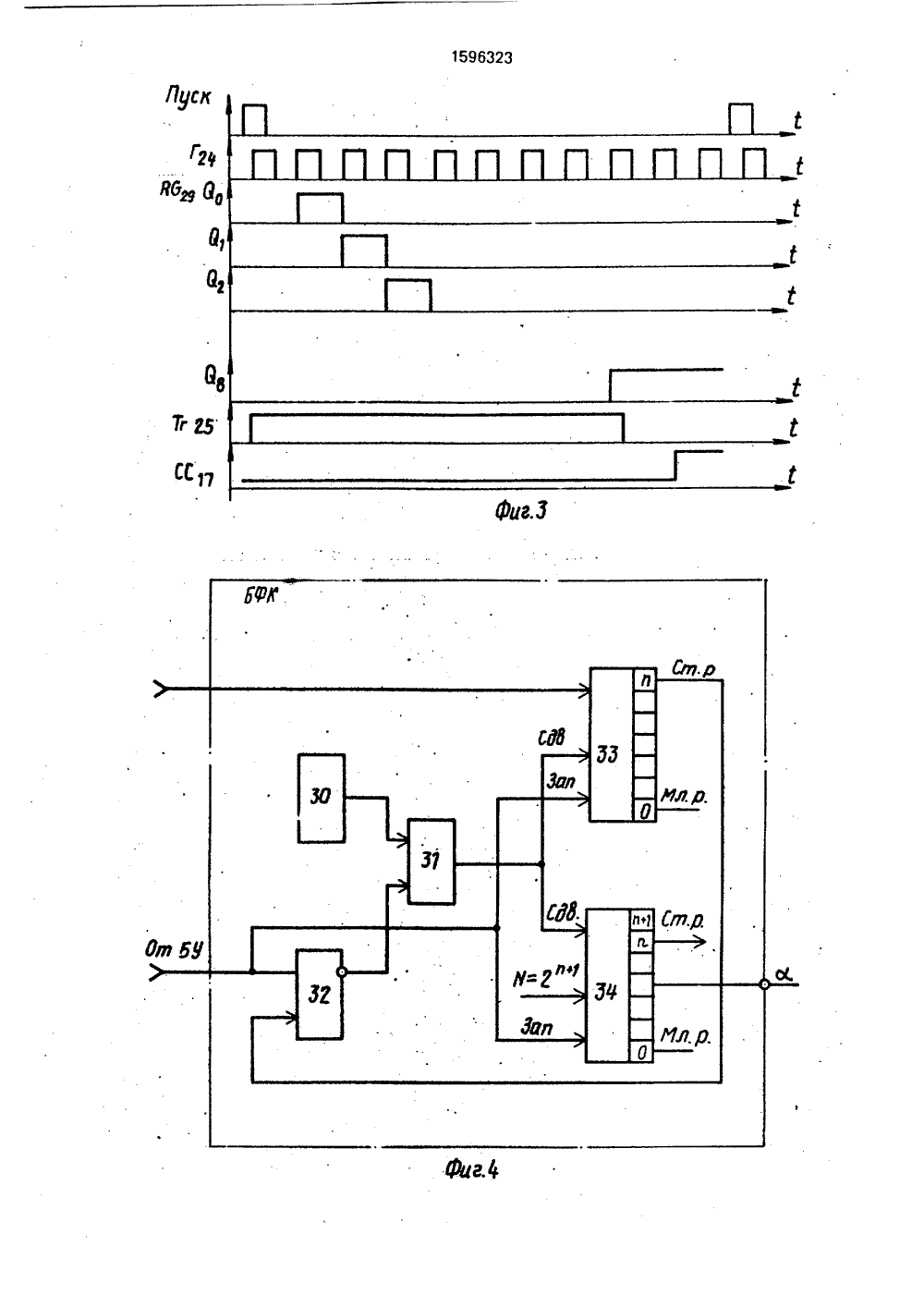

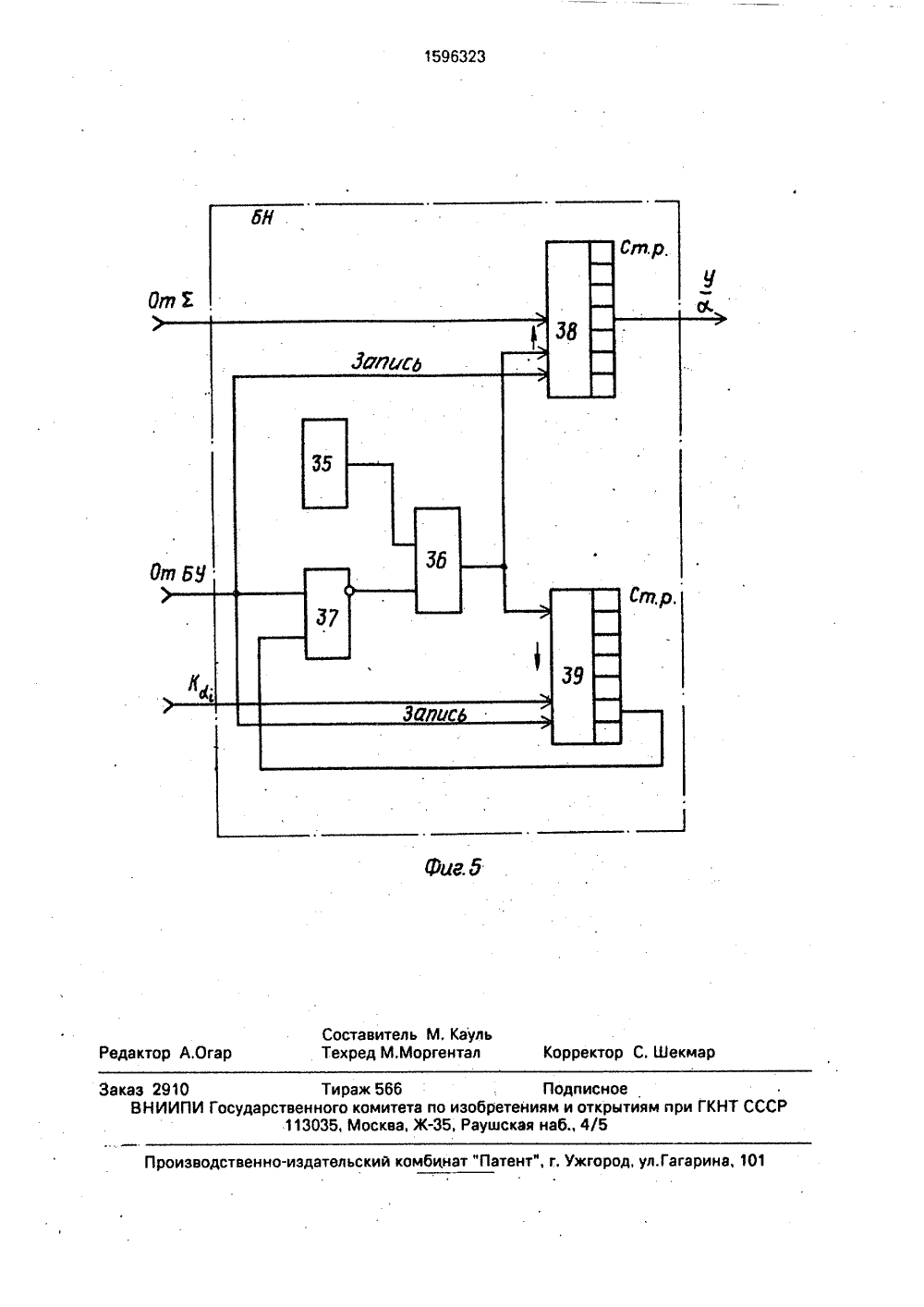

(5)5 0 06 Р 7/556 11 САНИЕ ИЗОБРЕТЕНИ содержит вход начального значения аргумента, блок формирования коэффициента, первый и второй блоки нормирования, три вычитателя, два умножителя, сумматор, выход; результата, два шинных коммутатора, два регистра, вход задания констант, блок памяти констант, блок сравнения. блок синхронизации, входсигнала "Пуск", накапливающий сумматор, первый и второй элементы ИЛИ. Блок синхронизации содержит генератор тактовых импульсов, триггер, первый и второй элементы И, элемент ИЛИ, сдвиговый регистр, Блок формирования констант содержит генератор, элемент И, триггер, первый и второй сдвиговые регистры, Блок нормирования содержит генератор, элемент И, триггер, первый и второй Б сдвиговые регистры. Работа устройства осский инстиодянский, ,И,БраиловССО,2- - )у -(1- 1, Н,ххована на соотношении у+1 Х 1 (1- )у+ - ,= 1,2,К; уо, у 1, х аданные значения. 5 ил,Устройство, соде значения аргумента. коэффициента, перв нормирования, перв 5 и 6, первый умнож тель 8, сумматор 9 второй шинный ком. гпстр 12, первый ш второй регистр 14,стант, блок 16 пам сравнения, блок вход 19 сигнала "П тель 20, накаплива также первый и в 22 и 23.ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯПРИ ГКНТ СССР К АВТОРСКОМУ СВИДЕТЕЛЬСТВ(56) Авторское свидетельство СМ 448459, кл. 6 06 Р 7/38, 1974Авторское свидетельство СВ 930314, кл, 0 06 Р 7/556, 198(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ЛОГАРИФМИЧЕСКОЙ ФУНКЦИИ(57) Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах для воспроизведения логарифмических функций, Цель изобретения - расширение области применения за счет увеличения диапазона изменения аргумента. Поставленная цель достигается тем, что устройство Изобретение относится к вычислительной технике и может быть использовано в цифровых вычислительных машинах воспроизведения логарифмических функций.Цель изобретения - расширение обла сти применения за счет увеличениядиапазона изменения аргумента.На фиг. 1 представлена структурная схема устройства; на фиг, 2 - схема блока синхронизации, пример исполнения; на фиг. 3 - временная диаграмма работы блока синхронизации; на фиг. 4 - схема блока формирования коэффициента, пример исполнения;. .на фиг. 5 - схема блока нормирования, пример исполнения,ржит вход 1 начального , блок 2 формирования ый и второй блски 3 и 4 ый и второй вычитатели итель 7, третий вычитавыход 10 результата, мутатор 11, первый реинный коммутатор 13. вход 15 задания коняти конс-ант, блок 17 18 синхронизации, уск", второй умножиющий сумматор 21, а торой элементы ИЛИБ лок синхронизации образуют генератор 24 тактовых импульсов, триггер 25, первый и второй элементы И 26 и 27, элементИЛИ 28 и сдвиговый регистр 29.Блок формирования коэффициентавключает генератор 30, элемент И 31, триггер 32, а также первый и второй сдвиговыерегистры 33 и 34.Блок нормирования содержит генератор 35, элемент И 36, триггер 37, первый ивторой сдвиговые регистры 38 и 39,Устройство работает следующим образом.Для воспроизведения значений функции у = 1 пх использован модифицированныйалгоритм Эмблабу =ф(а - х) ду+ бх, (1)где а - определенный параметр,Решением (1) является функция у = 1 пх.Уравнению (1) соответствует разностнцй аналогун.1 = (2 -- )у - (1 -- )у- + -х ха1= 1,2,И; (2)Каноническая форма 2) имеет видУ+ =АМ+буо задан где х- 2 --А = а 1(3) Параметр а вырабатывается в устройстве согласно условию 11 х 11а, поэтому винтервале а,Ь норма оператора Аь определяемая по формуле (3), не превосходит единицы, С целью увеличения быстродействия(2) параметр а должен бьгть числом, бли жайшим к х и кратным 2 , Например,х=0,126, а=0,125=2 ,1=3,Формула методической погрешностидля (2) имеет видь(х-8 хВ исходном состоянии по входу 15 задания констант заносятся величины Ь, уо, у 1,хь Шинные коммутаторы 13 и 11 устанавливаются в состояние, обеспечивающее подключение выходов блока 16 памятиконстант к входам регистров 14 и 12 соответственно. По приходу импульса по входу19 сигнала "Пуск" в регистры 14 и 12 соответственно заносятся величины уо.и у 1, аблок 18 синхронизации начинает вырабатывать последовательность импульсов. В блоке 2 формирования коэффициента по45 50 55 Ф ормула изобретения Устройство для вычисления логарифми-ческой функции, содержащее первый и второй регистры, первый и второй элементы ИЛИ; сумматор и блок синхронизации, причем вход запуска блока синхронизации соединен с входом "Пуск" устройства, о т л и ча ющееся тем,что, сцельюрасширения области применения за счет увеличениядиапазона изменения аргумента, оно содержит блок формирования коэффициента, первый и второй блоки нормирования, первый и второй шинные коммутаторы. блок сравнения, первый, второй и третий вычитатели, первый и второй умножители, накапливающий сумматор и блок памяти констант, причем вход задания констант успервому импульсу осуществляется формирование коэффициента а, по второму импульсу в блоках 3 и 4 нормирования формируются величины х/а и Ь/ба, по 5 третьему импульсу в вычитателе 5 формирухется величина (2 =), а в вычитателе 6 -63хвеличина (1 -- ), по четвертому импульсу вЦ10 умножителе 20 формируется произведениеху 1(2 -- ), а в умножителе 7 - произведениеахуо(1 -- ), по пятому импульсу в вычитателеЯ15 х х8 формируется разность у 1(2 -- ) - уо(1 р )апо шестому импульсу в сумматоре 9 формируется значение у 2, по седьмому импульсу шинный коммутатор 13 переключается в по ложение, при котором выход регистра 12подключается к входу регистра 14 и информация из регистра 12 заносится в регистр 14, т,е. вместо уо записывается у 1. По восьмому импульсу шинный коммутатор 11 пе реключается в положение, при которомвыход сумматора 9 подключается к входу регистра 12 и происходит перезапись значения у 2 в регистр 12 вместо у 1, Одновременно в накапливающем сумматоре 21 осуществ ляется увеличение числа х на величину 1,которая на девятом такте сравнивается с хк в блоке 17 сравнения. Если выполняется равенство х = 11 + х, то на выходе блока сравнения появляется сигнал, останавлива 35 ющий устройство и являющийся признакомокончания вычислений. В противном случае блок 18 синхронизации вырабатывает новую последовательность из девяти импульсов, причем по шестому импульсу на выходе 40 10 результата формируется очередное значение функции согласно алгоритму (1).тройства соединен с информационным входом блока памяти констант, выход конечного значения аргумента которого соединен с первым информационным входом, блока сравнения, выход которого соединен с вхо дом останова блока синхронизации, вход задания константы два устройства соединен с первым информационным входом первого вычитателя, вход задания константы один устройства соединен с первым ин формационным входом второго вычитателя, второй информационный вход которого соединен с вторым информационным входом первого вычитателя и с выходом первого блока нормирования, первый информаци онный вход которого соединен с первым информационным входом второго блока нормирования и с выходом блока формирования коэффициента, информационный вход которого соединен с вторым информа ционным входом первого блока нормирования, с вторым информационным входом блока сравнения и с выходом накапливающего сумматора, установочный вход которого соединен с входом начального 25 значения аргумента устройства, информационный вход накапливающего сумматора соединен с выходом значения шага аргумента блока памяти констант и с вторым информационным входом второго 30 блока нормирования, выход которого соединен с первым информационным входом сумматора, второй информационный вход которого соединенс выходом третьего вычитателя, первый информационный вход ко торого соединен с выходом первого умножителя, первый информационный вход которого соединен с выходом второго регистра, информационный вход которого соединен с выходом первого шинного 40 коммутатора, первый информационный вход которого соединен с выходом значения функции в нулевой точке блока памяти констант, второй информационный вход первого шинного коммутатора соединен с первым входом второго умножителя и с выходом первого регистра, информационный вход . которого соединен с выходом второго шинного коммутатора, первый информационный вход которого соединен с выходом значения функции в первой точке памяти констант, второй информационный вход второго шинного коммутатора соединен с выходом сумматора и с выходои результата устройства, выход первого вычитателя соединен с вторым информационным входом второго умножителя, выход которого соединен с вторым информационным входом третьего вычитателя, выход второго вычитателя соединен с вторым информационным входом второго умножителя, первый, второй, третий, четвертый, пятый, шестой, седьмой, восьмой и девятый выходы блока синхронизации соединены соответственно с входом управления блока формирования коэффициента, входами управления первого и второго блоков нормирования, с входами управления первого и второго вычитателей, с входами управления первого и второго умножителей, с входом управления третьего вычитателя, с входом управления первого шинного коммутатора и первым входом первого элемента ИЛИ, с входами управления накапливающего сумматора и второго шинного коммутатора и с первым входом второго элемента ИЛИ, с входом управления блока сравнения, вход управления первого регистра - с выходом второго элемента ИЛИ, второй вход которого соединен с входом "Пуск" устройства и с вторым входом первого элемента ИЛИ, выход которого соединен с входом управления второго регистра.1596323 Составитель М. КаульТехред М.Моргентал А.Огар Корректор С. Шекмар ед Производственнонат "Патент", г. Ужгород, ул. Гагарина, 10 ательский к Заказ 2910 Тираж 566 Подписное ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ ССС 113035, Москва, Ж, Раушская наб., 4/5

СмотретьЗаявка

4379448, 15.02.1988

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

АРСЕНИ ВЛАДИМИР ФЕДОРОВИЧ, БОРОДЯНСКИЙ МИХАИЛ ЕФИМОВИЧ, СУРЖЕНКО ИГОРЬ ФЕОДОСЬЕВИЧ, ВОЛКОВ ИМЕРТ НИКОЛАЕВИЧ, БРАИЛОВСКИЙ ГЕННАДИЙ ИСААКОВИЧ

МПК / Метки

МПК: G06F 7/556

Метки: вычисления, логарифмической, функции

Опубликовано: 30.09.1990

Код ссылки

<a href="https://patents.su/6-1596323-ustrojjstvo-dlya-vychisleniya-logarifmicheskojj-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления логарифмической функции</a>

Предыдущий патент: Устройство для возведения в квадрат двоичных чисел

Следующий патент: Устройство для формирования односвязной n-позиционной марковской последовательности

Случайный патент: Средства для удаления накипи с эмалированной и металлической поверхности