Управляемый формирователь пачек импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1559396

Автор: Горбунов

Текст

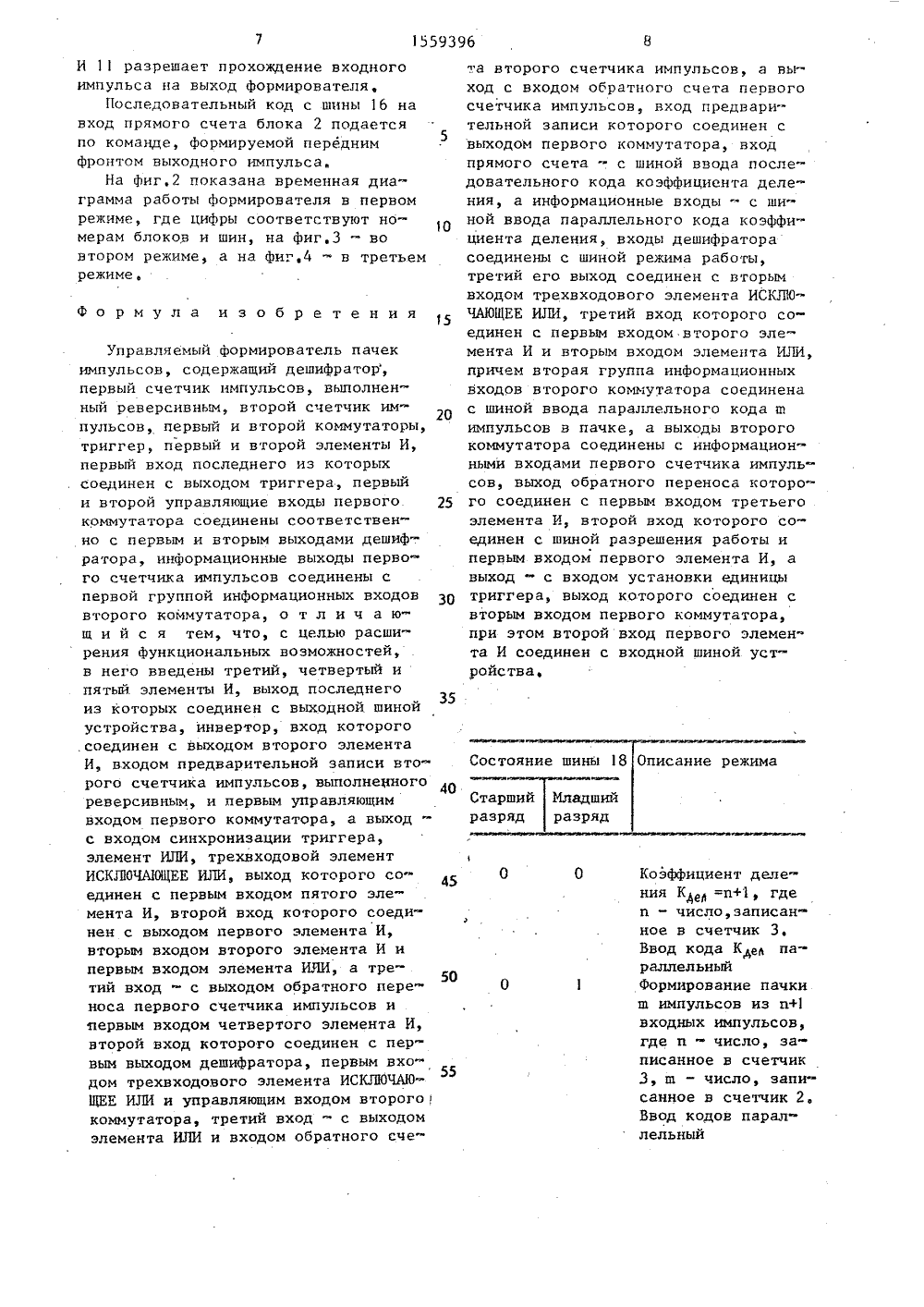

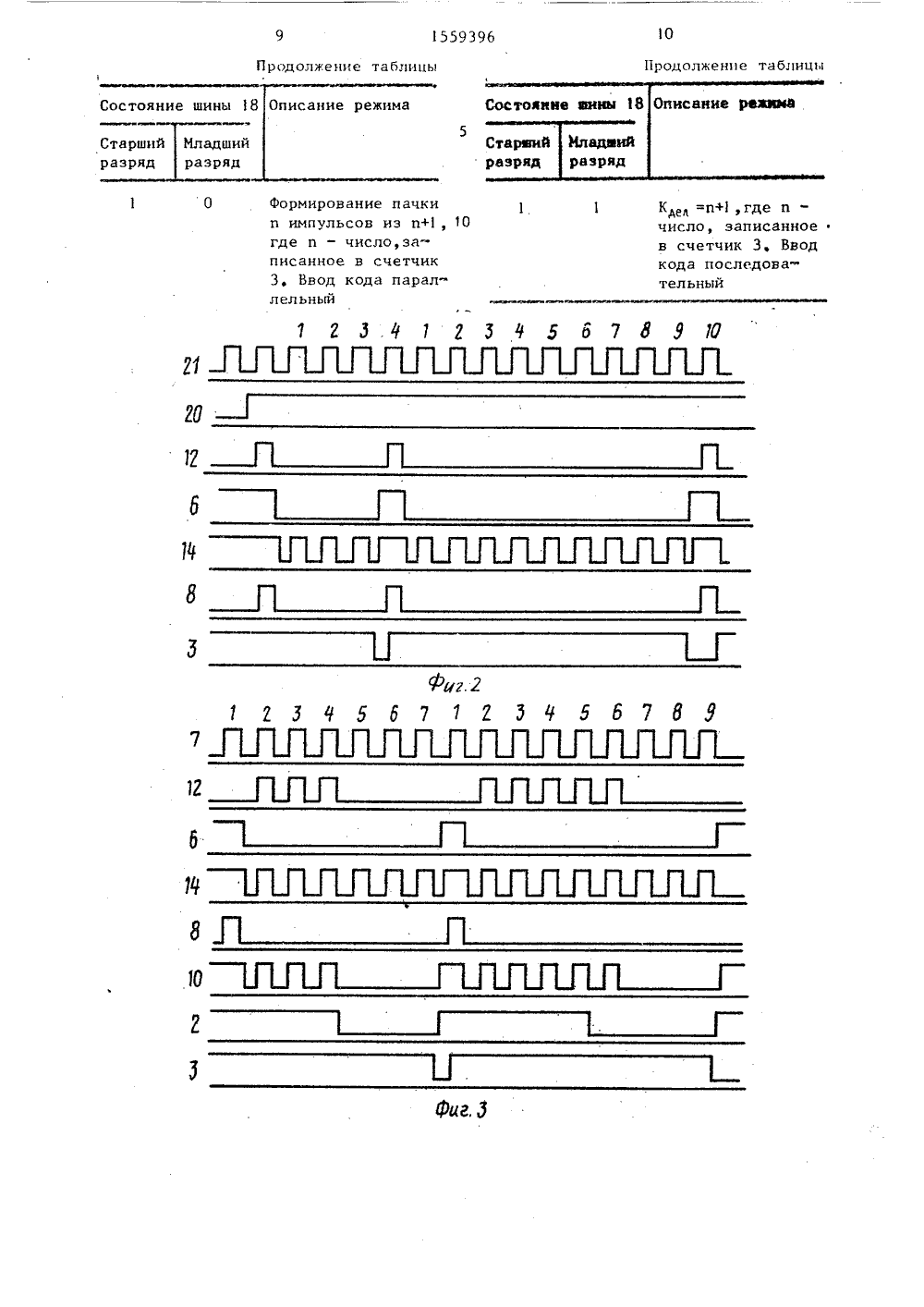

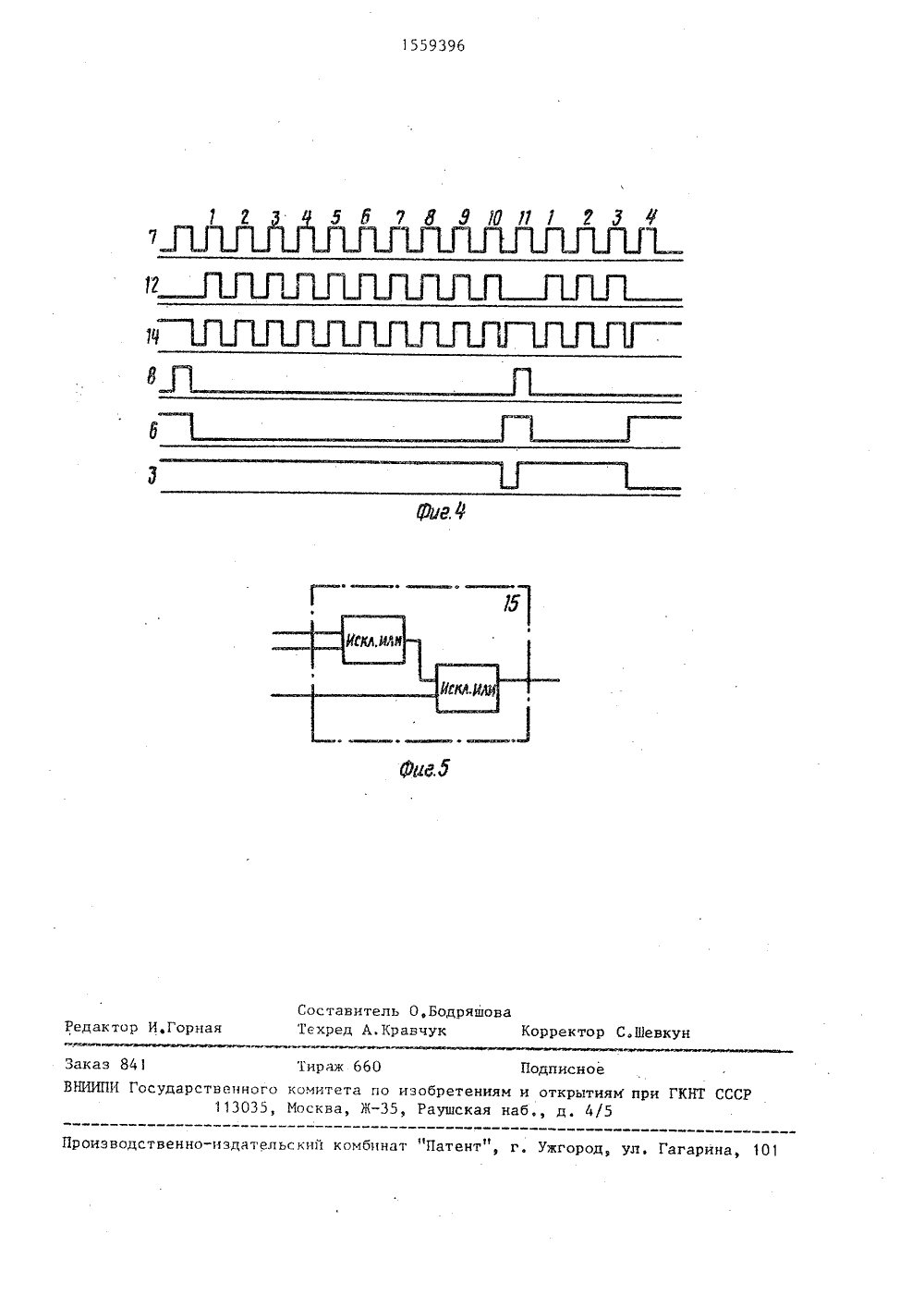

) Н Пи ЗОБРЕТДЕТЕЛЬСТВ У1 у.3 41 ОсудАРстненный иомитетпо изоБ етениям и отнрцтилмпри гкнт сса(56) Авторское свидетельство СССРУ 1210208, кл. Н 03 К 3/64,20,04,86Авторское свидетельство СССРР 834847, ,кл, Н 03 К 3/64,09,07,79.(57) Изобретение относится к импульсной технике и может быть использовано в измерительной и вычислительнойтехнике, Цель изобретения" расширение функциональных возможностей-досЯ ФОРМИРОВАТЕЛЬ ПАЧЕК 2тигается путем обеспечения режимовделения частоты входных импульсов наК = и+1 при параллельной и последо,лел,вательной записи кода и. Формирователь содержит дешифратор 1, первыйи второй реверсивные счетчики 2 и 3,первый и второй коммутаторы 4 и 5,триггер 6, первый, второй, .третий,четвертый и пятый элементы И 7-11,выходную шину 12 устройства, инвертор 13, элемент ИЛИ 14, трехвходовойэлемент ИСКЛЮЧАЮЩЕЕ ИЛИ 15, шины ввода последовательного кода К , ввода параллельного кода К , режимаработы, ввода параллельного кода шимпульсов в пачке, разрешения работы16-20 и входную шину 21 устройства,5 ил 1 табл,Изобретение относится к импульсной технике и может быть использовано в измерительной и вычислительнойтехнике.Цель изобретения - расширениефункциональных возможностей за счетобеспечения режимов деления частотыВходных импульсов на Кдеб - и+ припараллельной и последовательной записях кода и.На фиг.1 показана структурнаяэлектрическая схема предлагаемогоформирователя; на фиг,2-4 - времен-.ные диаграммы, поясняющие три режимаработы устройства: деление на К,формирование ш импульсов из (и+1 )входных импульсов, формирование иимпульсов из (и+1) входных импульсовсоответственно; на фиг.5 - стрУктУР 20ная электрическая схема трехвходового элемента ИСКЛЮЧАЮЩЕЕ ИЛИ,Формирователь содержит дешифратор1, первый реверсивный счетчик 2 исчетчик 3 импульсов, выполненный реверсивным ,первый 4 и второй 5 коммутаторы, триггер 6, первый 7, второй 8, третий 9, четвертый 10 и пятый 11 элементы И, выходную шину 12формирователя, инвертор 13, элемент 30ИЛИ 4, трехвходовой элемент ИСКЛЮЧАЮЩЕЕ ИЛИ 15, шины 16-20 ввода последовательного кода К , параллельного ввода кода КА , режима работы,ввода параллельного кода ш импульсов в пачке, разрешения работы ивходную шину 21 формирователя,Первый вход второго элемента И 8соединен с выходом триггера 6, первый и второй управляющие входы перво Ого коммутатора 4 соединены соответственно с первым и вторым выходами дешифратора 1, Информационные выходыпервого реверсивного счетчика 2 соединены с первой группой информационных входов второго коммутатора 5.Вход инвертора 13 соединен с выходом второго элемента И 8, входомпредварительной записи второго реверсивного счетчика 3 и первым управляющим входом первого коммутатора 4,а выход - с входом синхронизациитриггера, Выход трехвходового элемента ИСКЛЮЧАЮЩЕЕ ИЛИ 15 соединен с первым входом пятого элемента И 11, выход которого соединен с выходной шиной 12 формирователя, второй вход -с выходом первого элемента И 7, вторым входом второго элемента И 8, и первым входом элемента ИЛИ 14, а третий вход .- с выходом обратного переноса первого реверсивного счетчика2 и первым входом четвертого элемен."та И 1 О, второй вход которого соединен с первым выходом дешифратора 1,первым входом трехвходового элементаИСКЛЮЧАЮЩЕЕ ИЛИ 5 и управляющим входом второго коммутатора 5, третийвход - с выходом элемента ИЛИ 4 ивходом обратного счета второго реверсивного счетчика 3, а выход - с входом обратного счета первого реверсивного счетчика 2, вход предварительной записи которого соединен с выходом первого коммутатора 4, вход прямого счета - с шиной 6 ввода последовательного кода КА а информационные входы - с шиной 17 ввода параллельного кода КАе,Входы дешифратора соединены с шиной 18 режима работы, третий его выход соединен с вторым входом трехвходового элемента ИСКЛЮЧАЮЩЕЕ И 5 М15, третий вход которого соединен спервым входом второго элемента И 8 ивторым входом элемента ИЛИ 4,Вторая группа информационных входов второго коммутатора 5 соединенас шиной 19 ввода параллельного кодачисла ш импульсов в пачке, а выходывторого коммутатора - с информационными входами первого реверсивногосчетчика 2, выход обратного переносакоторого соединен с первым входомтретьего элемента И 9, второй входкоторого соединен с шиной 20 разрешения работы и первым входом первогоэлемента И 7, а выход - с входом установки триггера, выход которого соединен с вторым входом первого коммутатора 4, Второй вход первого элемента И 7 соединен с входной шиной21 формирователя,Формирователь работает следующимобразом,Сигналами на шине 18 режима можнозадать четыре различных режима работы формирователя, описание которыхприведено в таблице,В исходном состоянии на шине 20 разрешения работы низкий уровень, который запрещает прохождение импульсов на вход счетчика 3 и устанавливает триггер 6 в состояние "1", подготавливая запись кода в счетчики 2 и 35 15Б первом режиме все выходы дешиф раторанаходятся в состоянии 0,при этом к выходу коммутатора 4 подключается выход триггера 6, которыйнаходится в состоянии "1 , Эта "1"поступает на вход записи счетчика 2,записывая в него код с шины 17, Этоткод через коммутатор 5, на управляющем входе которого "0", поступает на.информационные входы счетчика 3.Высоким уровнем на шине 20 открывается доступ .импульсов на входсчетчика 3. Первый импульс черезэлемент И 8 поступает на вход записисчетчика 3 и записывает код с инфор- .мационных входов, При этом на выходах счетчиков 2 и 3 присутствует "1",Задним фронтом импульса, прошедшего через элемент И 8 и инвертор 13,триггер 6 устанавливается в "0", чемподготавливается прохождение импульсов на вход обратного счета счетчика 3,По заднему фронту импульса, порядковый номер которого равен числу,записанному в счетчик 3, на выходепоследнего формируется сигнал низкого уровня, который через элемент И9 устанавливает триггер 6 в "1",тем самым записывая новый код в счетчик 2, подготавливая перезапись кодав блок 3 и открывая доступ входнымимпульсам на выход формирователя через элемент И 11, Следующий за этим(и+1)-й импульс (где и - число, записанное в счетчик 3) проходит навыход формирователя, а также записывает, в блок 3 новое значение кодаи устанавливает триггер 6 в состояние "О", тем самым вновь закрываядоступ импульсам на выход Формирователя,Во втором режиме на первом выходедешифратора высокий уровень, на остальных - низкий, При этом к выходукоммутатора 4 подключается выходэлемента И 8, а к выходам коммутатора 5 - шина 1.9 ввода кода К.Алгоритм работы формирователя вовтором режиме (Ке =(и+1)/ш) следующий,Первый импульс с выхода элементаИ 7 записывает соответствующие кодыв счетчики 2 и 3 и задним фронтомустанавливает триггер 6 в состояние"0", подготавливая прохождение последующих входных импульсов на выходформирователя через элемент И 11593966По заднему фронту импульса, порядковый номер которого равен ш+1(ш - число, записанное в пересчетныйблок 2), на выходе блока 2 появляется сигнал, закрывающий доступ вход-ным импульсам на выход Формирователяи вход обратного счета пересчетногоблока 2. Входные импульсы продолжаютпоступать только на вход обратногосчета блока 3, на выходе которого поприходу заднего фронта (и+1)-го импульса (и - число, записанное в блок3) формируется сигнал, устанавливающий триггер 6 в состояние "1" и темсамым подготавливающий запись новыхчисел в счетчики 2 и 3, Таким образом, на выход Формирователя из(и+1)-го входного импульса проходят20 ш импульсов, где ш и и - числа, записанные в блоки 2 и 3 соответственно,В третьем режиме алгоритм работы25 заключается в следующем,Входные импульсы проходят навыход формирователя до тех пор, показадний фронт импульса с порядковымномером п (п - число, записанное в30 блок 3) не сформирует на выходе блока 3 сигнал, устанавливающий триггер6 в состояние "1" и тем самым перекрывающий доступ входным импульсамна выход Формирователя, Следующий(и+1)-й импульс на выход формирова 35теля не проходит, но осуществляетзапись в блок 3 нового числа и.В четвертом режиме на втором выходе дешифратора 1 высокий уровень,40 на остальных - низкий, При этом выход коммутатора 4 оказывается подключенным к шине "0",Последовательный код с шины 16подается на вход прямого счета счетчи"5 ка 2 и с выходов этого блока черезкоммутатор 5 поступает в параллельном уже коде на информационные входыблока 3,Первый импульс, пришедший после50 разрешения деления (высокий уровеньна шине 20),осуществляет запись кодав блок 3 и своим задним Фронтом устанавливает триггер 6 в "0"Задний Фронт импульса, порядковыйномер которого равен числу, записанному в блоке 3, формирует низкийуровень на выходе этого блока, устанавливающий триггер 6 в "1", котораячерез элементы ИСКЛЮЧАЮЩЕЕ ИЛИ 15 иИ 1 разрешает прохождение входного импульса на выход формирователя,Последовательный код с шины 16 на вход прямого счета блока 2 подается по команде, формируемой передним фронтом выходного импульсаНа фиг,2 показана временная диаграмма работы формирователя в первом режиме, где цифры соответствуют номерам блоков и шин, на фиг.3 - во втором режиме, а на фиг,4 - в третьем режиме. 1 О Формула изобретения Управляемый формирователь пачек импульсов, содержащий дешифратор, первый счетчик импульсов, выполненный реверсивным, второй счетчик импульсов, первый и второй коммутаторы, триггер, первый и второй элементы И, первый вход последнего из которых соединен с выходом триггера, первый и второй управляющие входы первого 25 коммутатора соединены соответственно с первым и вторым выходами дешифратора, информационные выходы первого счетчика импульсов соединены с первой группой информационных входов второго коммутатора, о т л и ч а ющ и й с я тем, что, с целью расширения функциональных возможностей, в него введены третий, четвертый и пятый. элементы И, выход последнего35 иэ которых соединен с выходной шинои устройства, инвертор, вход которого .соединен с выходом второго элемента И, входом предварительной записи второго счетчика импульсов, выполнеиного 40 реверсивным, и первым управляющим входом первого коммутатора, а выходс входом синхронизации триггера, элемент ИЛИ, трехвходовой элемент ИСКЛ 10 ЧАЮЩЕЕ ИЛИ, выход которого соединен с первым входом пятого элемента И, второй вход которого соединен с выходом первого элемента И, вторым входом второго элемента И и первым входом элемента ИЛИ, а третий вход - с выходом обратного переноса первого счетчика импульсов и первым входом четвертого элемента И, второй вход которого соединен с первым выходом дешифратора, первым вхо 55 дом трехвходового элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и управляющим входом второгокоммутатора, третий вход - с выходом элемента ИЛИ и входом обратного счета второго счетчика импульсов, а выход с входом обратного счета первого счетчика импульсов, вход предварительной записи которого соединен с выходом первого коммутатора, вход прямого счета - с шиной ввода последовательного кода коэффициента деления, а информационные входы - с шиной ввода параллельного кода коэффициента деления, входы дешифратора соединены с шиной режима работы, третий его выход соединен с вторым входом трехвходового элемента ИСКЛЮЧАЮЩЕЕ ИЛИ, третий вход которого соединен с первым входом второго элемента И и вторым входом элемента ИЛ 1, причем вторая группа информационных входов второго коммутатора соединена с шиной ввода параллельного кода ш импульсов в пачке, а выходы второго коммутатора соединены с информационными входами первого счетчика импульсов, выход обратного переноса которого соединен с первым входом третьего элемента И, второй вход которого соединен с шиной разрешения работы и первым входом первого элемента И, а выход - с входом установки единицы триггера, выход которого соединен с вторым входом первого коммутатора, при этом второй вход первого элемента И соединен с входной шиной устройства,сание режима Сост Стар разр Коэффициент деления Ке =и+1, где и - число, записанное в счетчик 3. Ввод кода КАев параллельный Формирование пачки ш импульсов из п+1входных импульсов, где и - число, записанное в счетчик 3 ш число запи санное в счетчик 2. Ввод кодов парал- лельный10 1559396 форми п имп ов ь ое ис ельн Продолжение таблицы е пачки из и+1, 1 ло,за- счетчик вод кода пара Продолжение таблицы Ке =и+1,где и "число, записанноев счетчик 3Вводкода последовательный1559396 ор И,Горная Корректор С.Шевкун Подпис Ти коми Коскв Производственно-издательский комбинат "Патент, г. Ужгород, ул, Гагарина, 101 Заказ 841ВБ 1 ИПИ Государственн1130 Составитель О,БодряшовТехред А.Кравчук а ло изобретениям и открытияМ при ГКНТ СССР Ж, Раушская наб д. 4/5

СмотретьЗаявка

4326417, 12.11.1987

ПРЕДПРИЯТИЕ ПЯ Г-4152

ГОРБУНОВ АНДРЕЙ ВЛАДИМИРОВИЧ

МПК / Метки

МПК: H03K 3/64

Метки: импульсов, пачек, управляемый, формирователь

Опубликовано: 23.04.1990

Код ссылки

<a href="https://patents.su/6-1559396-upravlyaemyjj-formirovatel-pachek-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Управляемый формирователь пачек импульсов</a>

Предыдущий патент: Управляемый генератор импульсов

Следующий патент: Управляемый формирователь импульсов

Случайный патент: Устройство для автоматического вождения мобильного агрегата