Устройство для вычисления систем булевых функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1532912

Автор: Беляков

Текст

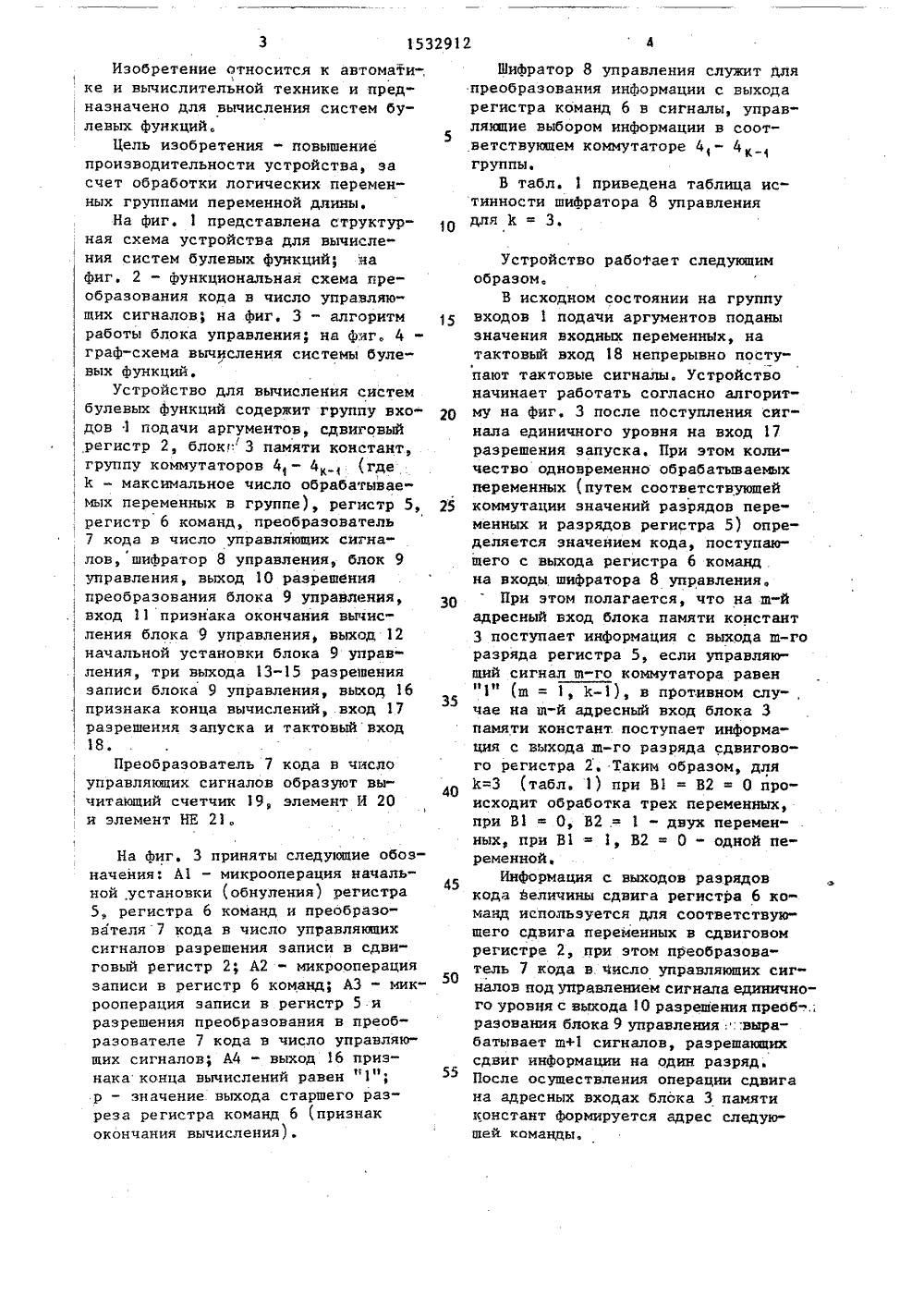

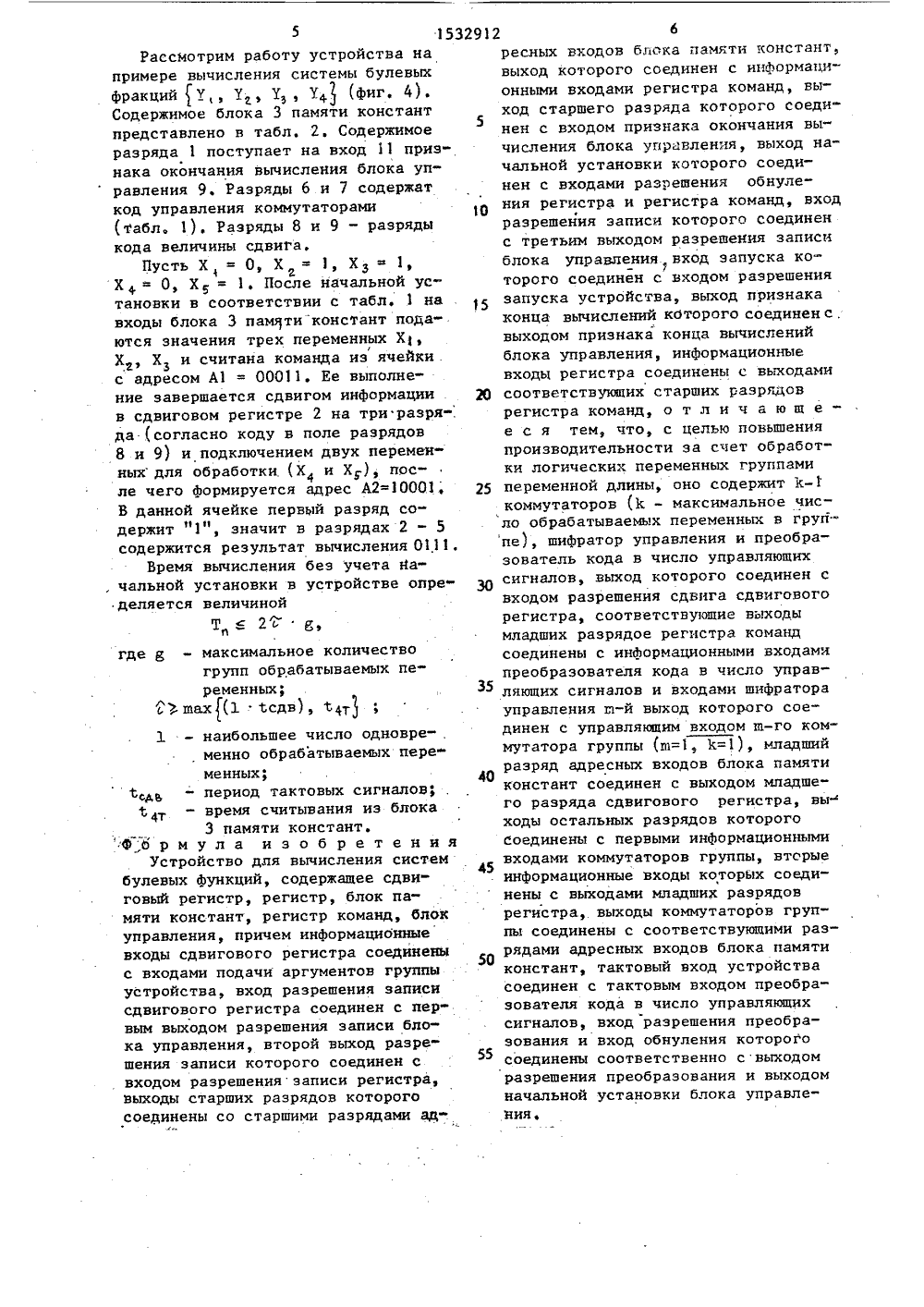

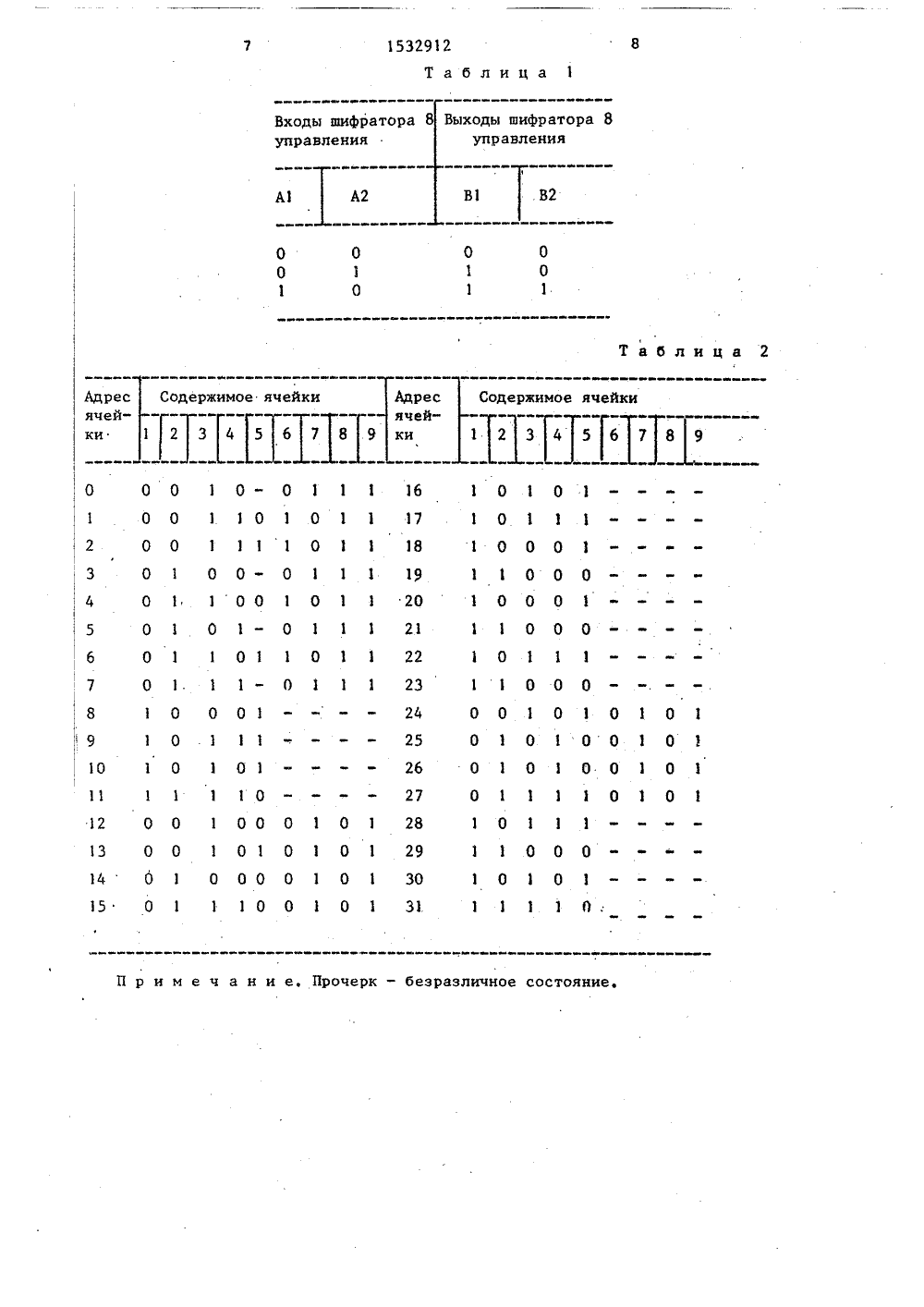

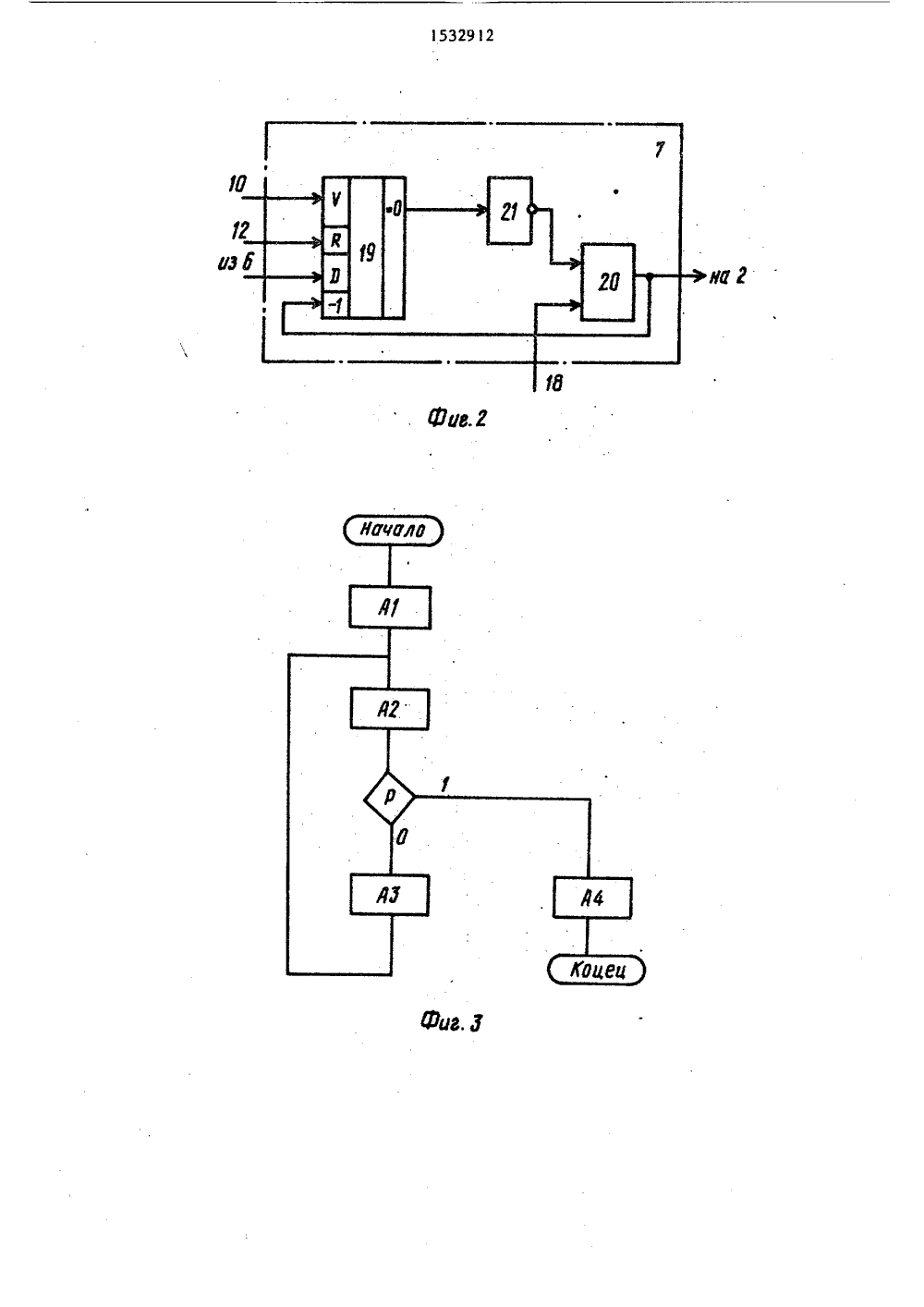

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИРЕСПУБЛИК б Р 7/00 АНИЕ ИЗОБРЕТ ОП ые системы. информации/ и В.Б,Смол ат, 1985, с ова.-,74, ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ВТОРИЧНОМУ СВИ ТЕЛЬСТВ(56) йнформационн Табличная обработка Подред. Е.П.БалашоваЛ.: Энергоатомиздрис. 3-12 а.(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯСИСТЕМ БУЛЕВЫХ ФУНКЦИЙ.предназначено для вычисления систем булевых функций. Цель изобре 2тения - повышение производительности устройства за счет. обработки логических переменных группами переменной длины, Устройство содержит группу входов 1 подачи аргументов, сдвиговый регистр 2, блок памяти 3 . констант, группу коммутаторов 4 - 4(Е - максимальное число обрабатываемых переменных в группе), регистр 5, регистр команд б,преобразователь кода 7 в число управляющих сигналов, шифратор управления 8, блок управления 9. Устройство работает следующим образом. На группу входов подачи аргументов подаются значения входных неремнных, и устройство вычисляет значения булевых функций от и переменных группами переменной длины. 4 ил., 2 табл.Изобретение относится к автомати-, ке и вычислительной технике и предназначено для вычисления систем булевых функций.Цель изобретения - повышение производительности устройства, за счет обработки логических переменных группами переменной длины.На фиг. 1 представлена структурная схема устройства для вычисления систем булевых функций; на Фиг. 2 - функциональная схема пре 10 образования кода в число управляю" щих сигналов, на Фиг. 3 - алгоритм 40 На фиг, 3 приняты следующие обозначения: А 1 - микрооперация начальной установки (обнуления) регистра45 5, регистра 6 команд и преобразователя 7 кода в число управляющих сигналов разрешения записи в сдвиговый регистр 2; А 2 - микрооперация записи в регистр 6 команд; АЭ - мик" рооперация записи в регистр 5 и разрешения преобразования в преобразователе 7 кода в число управляющих сигналов; А 4 - выход 16 признака конца вычислений равен "1"; р - значение выхода старшего разреза регистра команд 6 (признак окончания вычисления),работы блока управления; на Фиг. 4 граф-схема вычисления системы булевых Функций.Устройство для вычисления систембулевых функций содержит группу входов 1 подачи аргументов, сдвиговыйрегистр 2, блок 3 памяти констант,группу коммутаторов 4 - 4(гдеК - максимальное число обрабатывае мых переменных в группе)регистр 5, 25, регистр 6 команд, преобразователь7 кода в число управляющих сигна лов,шифратор 8 управления, блок 9управления, выход 10 разрешенияпреобразования блока 9 управления,вход 11 признака окончания вычисления блока 9 управления, выход 12начальной установки блока 9 управления, три выхода 13-15 разрешениязаписи блока 9 управления, выход 16признака конца вычислений, вход 1735разрешения запуска и тактовый вход18,Преобразователь 7 кода в числоуправляющих сигналов образуют вычитающий счетчик 19, элемент И 20и элемент НЕ 21. Шифратор 8 управления служит для преобразования информации с выхода регистра команд 6 в сигналы, управляющие выбором информации в соответствующем коммутаторе 41- 4 к 1 группы.В табл. 1 приведена таблица истинности шифратора 8 управления для К = 3. Устройство работает следующимобразом.В исходном состоянии на группувходов 1 подачи аргументов поданызначения входных переменных, натактовый вход 18 непрерывно поступают тактовые сигналы. Устройствоначинает работать согласно алгоритму на фиг. 3 после поступления сигнала единичного уровня на вход 17разрешения запуска. При этом количество одновременно обрабатываемыхпеременных (путем соответствующейкоммутации значений разрядов переменных и разрядов регистра 5) определяется значением кода, поступающего с выхода регистра 6 команд .на входы шифратора 8 управления.При этом полагается, что на ш-йадресный вход блока памяти констант3 поступает информация с выхода ш-горазряда регистра 5, если управляю"щнй сигнал ш-го коммутатора равен"1" (ш = 1, К), в противном слу-,чае на ш-й адресный вход блока 3памяти констант. поступает информация с выхода а-го разряда сдвигового регистра 2. Таким образом, дляК=З (табл, 1) при В 1 = В 2 = О происходит обработка трех переменных,при В 1О, В 2 .= 1 - двух переменных, при В 11, В 2 = О - одной переменной.Информация с выходов разрядовкода Величины сдвига регистра 6 команд используется для соответствующего сдвига переменных в сдвиговомрегистре 2, при этом преобразователь 7 кода в число управляющих сигналов нод управлением сигнала единичного уровня с выхода О разрешения преоб-;разования блока 9 управления .: вырабатывает ш+1 сигналов, разрешающихсдвиг информации на один разряд.После осуществления операции сдвигана адресных входах блока 3 памятиконстант формируется адрес следующей.команды,Рассмотрим работу устройства напримере вычисления системы булевыхфракций 1 т, , а 1 (фиг. ф).Содержимое блока 3 памяти константпредставлено в табл. 2Содержимоеразряда 1 поступает на вход 11 признака окончания вычисления блока управления 9. Разряды 6 и 7 содержаткод управления коммутаторами(Табл, 1), Разряды 8 и 9 - разрядыкода величины сдвига.Пусть Х = О, Х = 1, Хэ =к 1,Х 4, = О, Х = 1, После начальной ус"тановки в соответствии с табл. 1 навходы блока 3 памятиконстант подаются значения трех переменных Х 1,Хэ, Х и считана команда из ячейки .с адресом А 1 = 00011. Ее выполнение завершается сдвигом информациив сдвиговом регистре 2 на три разря-да (согласно коду в поле разрядов8 и 9) и подключением двух переменных для обработки (Х 4 и Х), после чего формируется адрес А 2=10001;В данной ячейке первый разряд содержит "1", значит в разрядах 2 - 5содержится результат вычисления 0111,Время вычисления беэ учета на, чальной установки в устройстве определяется величинойТ я 2 ц,где- максимальное количествогрупп обрабатываемых переменных;-как 1 каца ка 11 - наибольшее число одновре- .менно обрабатываемых переменных;Седа - период тактовых сигналов;14 т - время считывания из блока3 памяти констант. Формула изобретенияУстройство для вычисления систем булевых Функций, содержащее сдвиговый регистр, регистр, блок памяти констант, регистр команд, блок управления, причем информационные входы сдвигового регистра соединены с входами подачи аргументов группы устройства, вход разрешения записи сдвигового регистра соединен с первым выходом разрешения записи блока управления, второй выход разрешения записи которого соединен с входом разрешения записи регистра, выходы старших разрядов которого соединены со старшими разрядами ад управления ш-й выход которого соединен с управлякщим входом ш-го коммутатора группы (ш=1, =1), младшийразряд адресных входов блока памятиконстант соединен с выходом младшего разряда сдвигового регистра, выаходы остальных разрядов которогосоединены с первыми информационными а 5входами коммутаторов группы, вторые . информационные входы которых соединены с выходами младших разрядоврегистра, выходы коммутаторов группы соединены с соответствующими разрядами адресных входов блока памятиконстант, тактовый вход устройствасоединен с тактовым входом преобразователя кода в число управляющихсигналов, вход разрешения преобразования и вход обнуления которогосоединены соответственно с выходомразрешения преобразования и выходомначальной установки блока управления,5 10 5 20 25 ресных входов блока памяти констант выход которого соединен с информационными входами регистра команд, выход старшего разряда которого соединен с входом признака окончания вычисления блока управления, выход начальной установки которого соединен с входами разрешения обнуления регистра и регистра команд, вход разрешения записи которого соединен с третьим выходом разрешения записи блока управления вход запуска которого соединен с входом разрешения запуска устройства, выход признака конца вычислений которого соединен с, выходом признака конца вычислений блока управления, информационные входы регистра соединены с выходами соответствующих старших разрядов регистра команд, о т л и ч а ю ш е е с я тем, что, с целью повышения производительности за счет обработки логических переменных группами переменной длины, оно содержит Хкоммутаторов (К - максимальное число обрабатываемых переменных в группе), шифратор управления и преобразователь кода в число управляющихсигналов, выход которого соединен свходом разрешения сдвига сдвиговогорегистра, соответствующие выходымладших разрядое регистра командсоединены с информационными входамипреобразователя кода в число управляюших сигналов и входами шифратора,В А Таблица Адрес Содержимое ячейки Адрес Содержимое ячейки -ГФ111 Ф1111 Н О О О 1 О - О 1 1 1 1 6 1 0 1 0 1 О 1 17 1 0 1 1О О О 1 1 0 0 О 0 1 1 19 а О О 1 0 О 0 115329 12 Составитель В, СорокТехредЛ.Олийнык орректор В;Кабации чолинс дакто Заказ 8100/53 Тираж 668 ПодписноеВНИИПИ Гасударственного комитета по изобретениям и открытиям при ГКНТ СС 113035, Москва, Ж, Раушская наб., д. 4/5 атент", г, Уж ул. Гагарина, 101 Производственно-издательский комбин

СмотретьЗаявка

4431889, 30.05.1988

ФИЛИАЛ "ВОСХОД" МОСКОВСКОГО АВИАЦИОННОГО ИНСТИТУТА ИМ. СЕРГО ОРДЖОНИКИДЗЕ

БЕЛЯКОВ СТАНИСЛАВ ЛЕОНИДОВИЧ

МПК / Метки

МПК: G06F 7/00

Метки: булевых, вычисления, систем, функций

Опубликовано: 30.12.1989

Код ссылки

<a href="https://patents.su/6-1532912-ustrojjstvo-dlya-vychisleniya-sistem-bulevykh-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления систем булевых функций</a>

Предыдущий патент: Устройство для реализации бесповторных функций

Следующий патент: Устройство для сортировки чисел

Случайный патент: Станок для выделки кирпича