Формирователь импульсов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1522388

Авторы: Брайловский, Летюхин

Текст

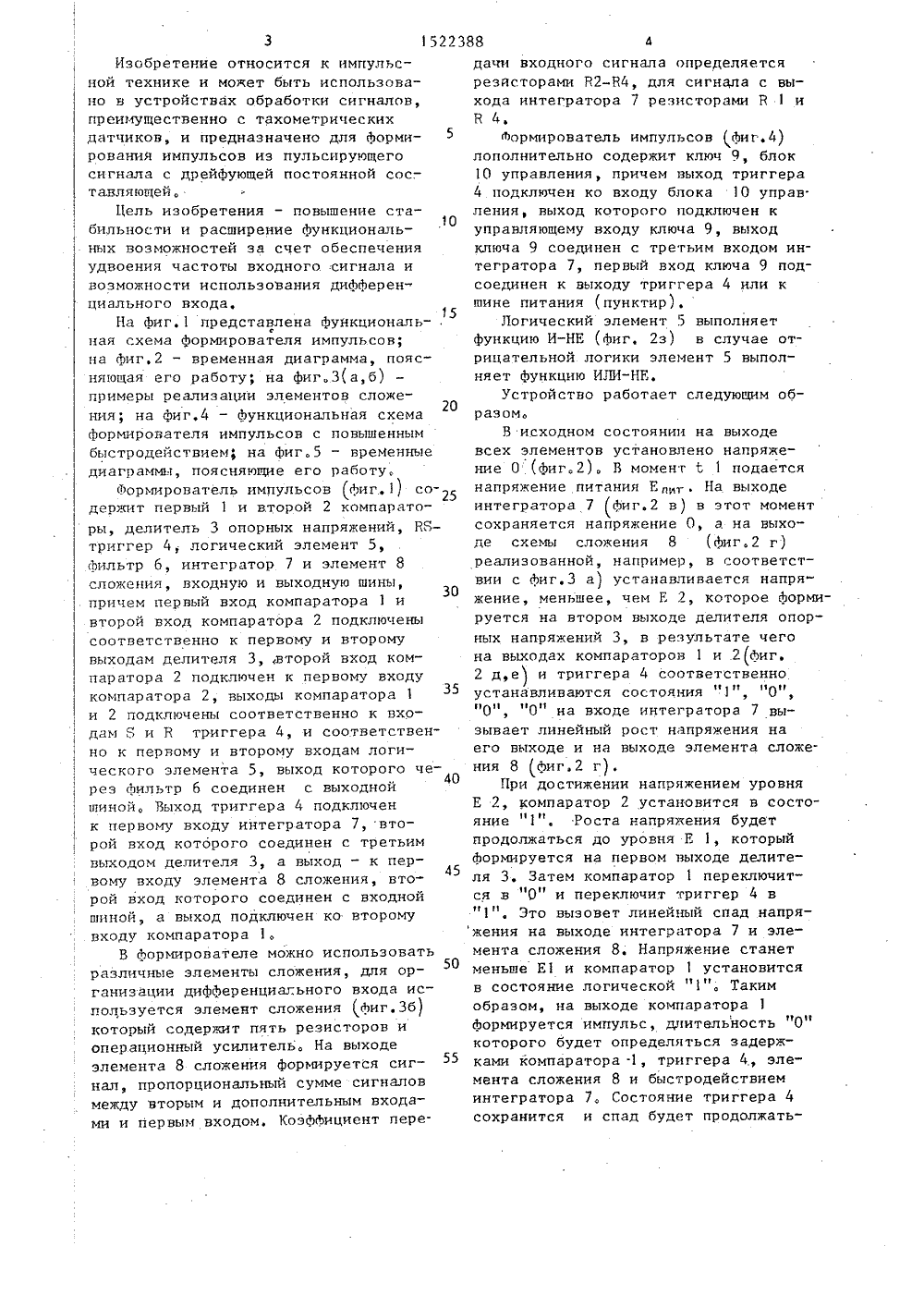

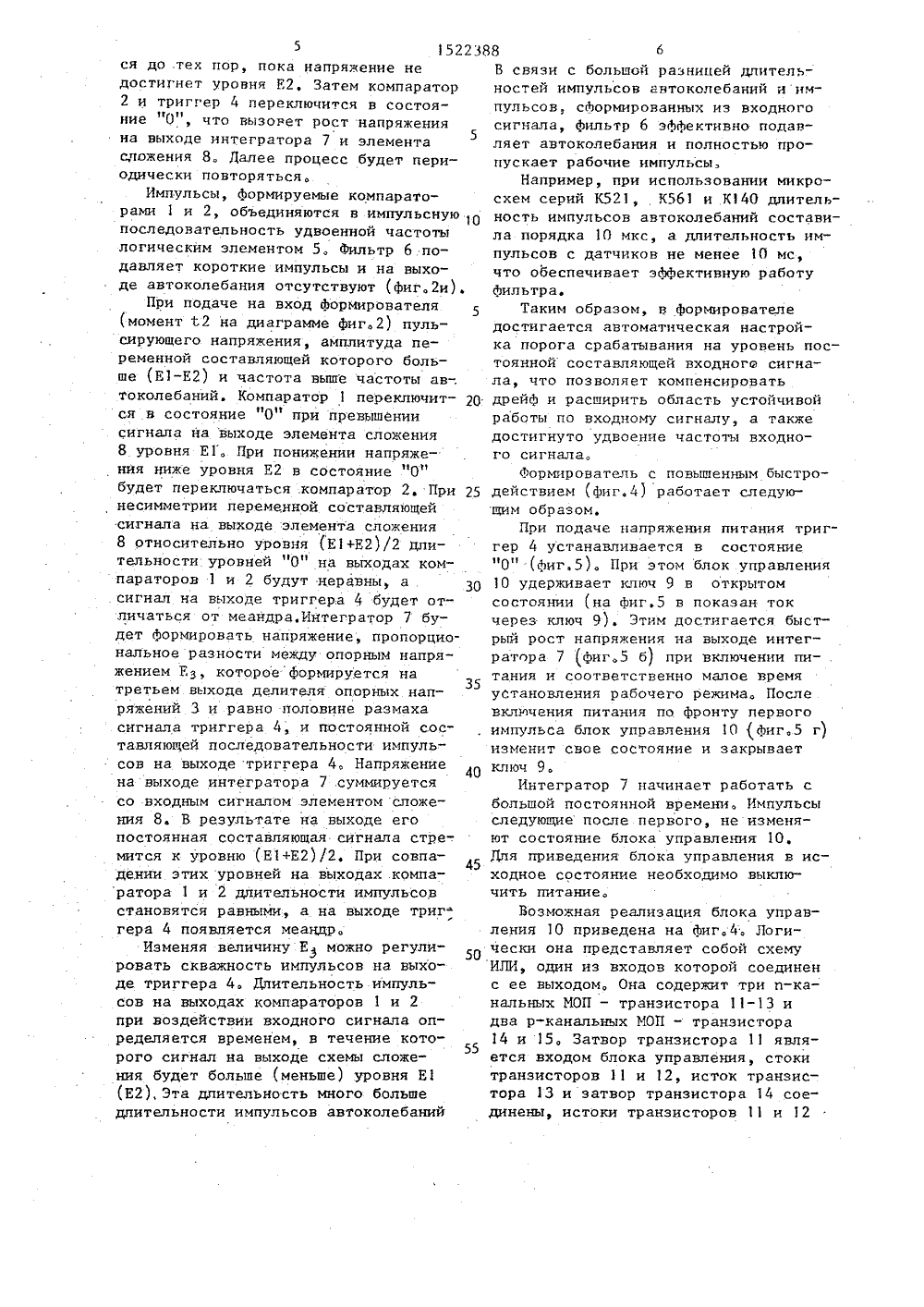

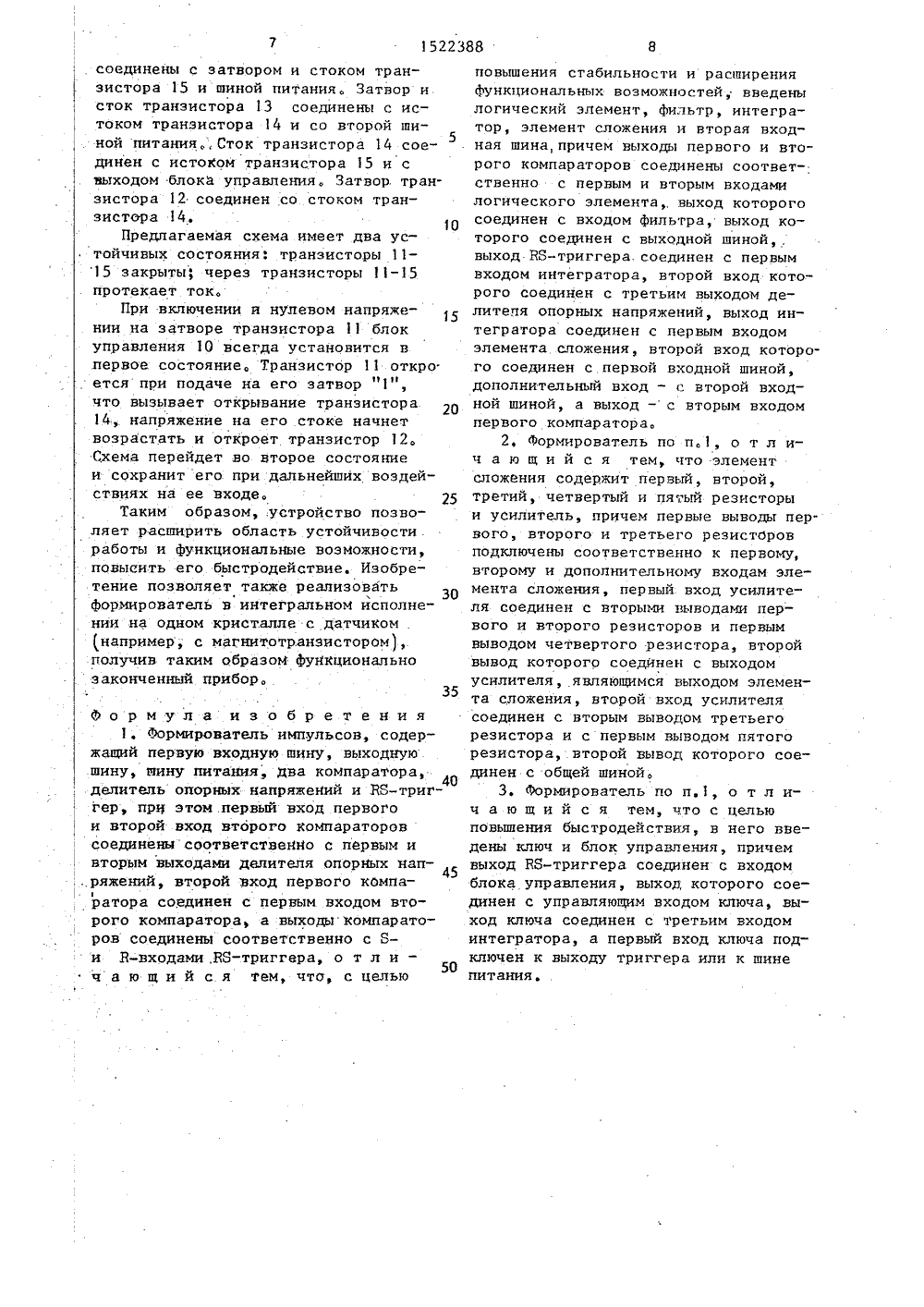

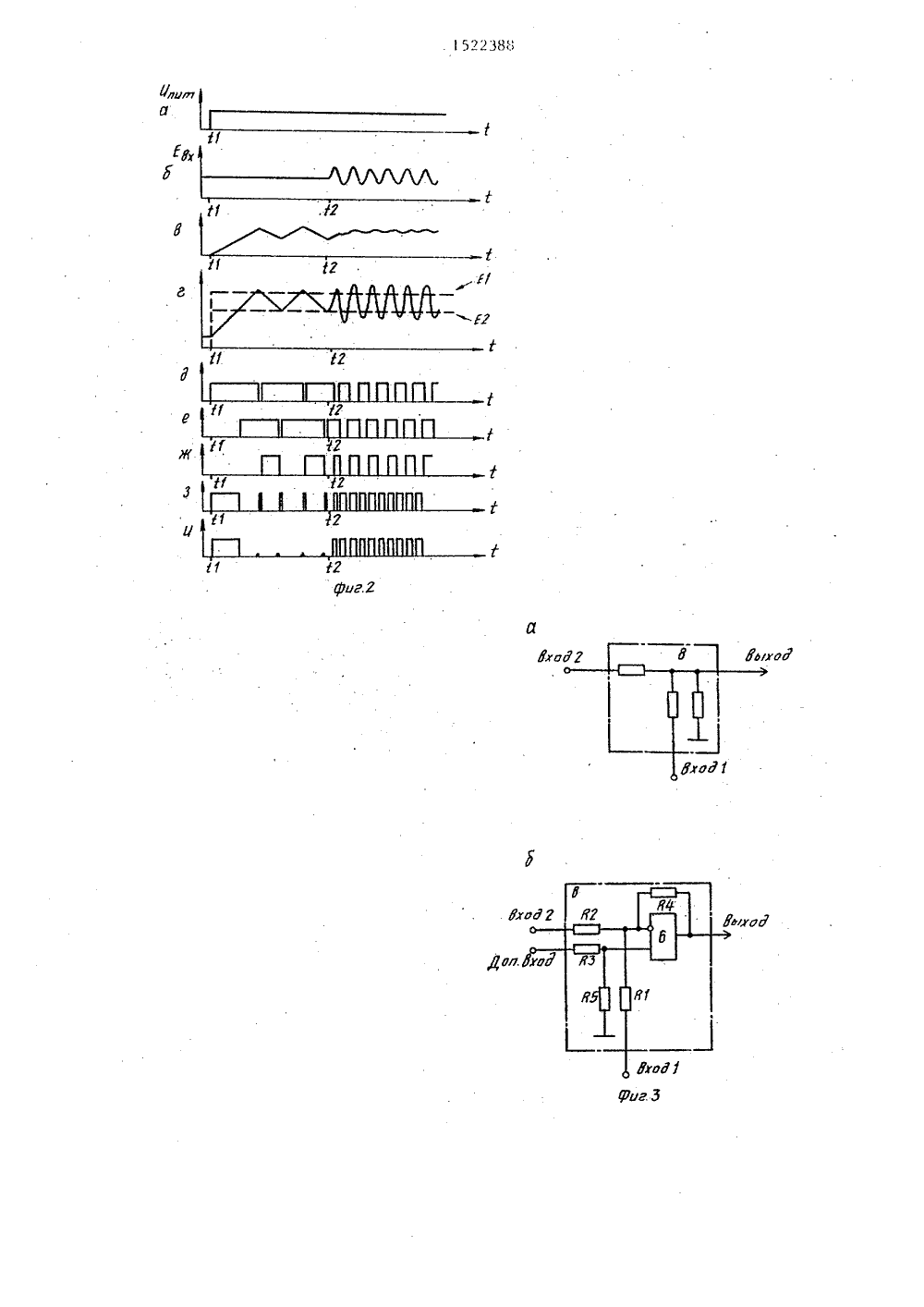

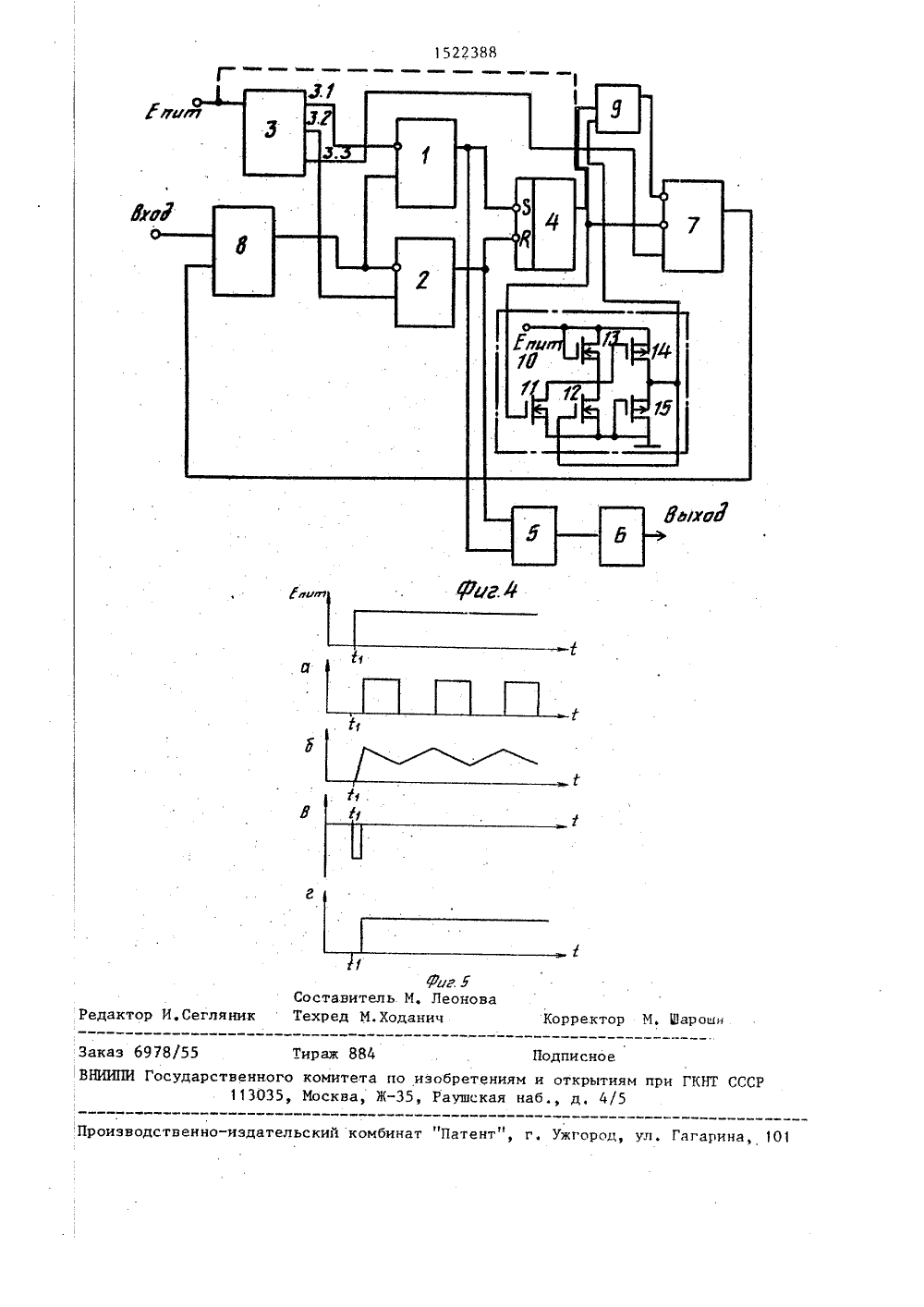

)4 НОЗК 5 ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЦТИЯМПРИ ГКНТ СССР НИЕ ИЗОБРЕ П СНОМУ СВИДЕТЕЛЬСТВУ 43224 23.09 15.11 Ленин ное о учно-производЭлектронмаш".С. Брайловский Д,А.621.3Хоров У, Искусст р, 1984, т емот с. 4.23. е 54) ФОРМИРОВ 57) Изобрете ой технике,устройства реимуществен атчиков и пр вания им Еп,89. Бюл. Рградское набъединениеЛетюхин и Г74 (088. 81иц П. и Хилхники, М.:с. 7. 1.т.1 с. 272 ТЕЛЬ ИМПУЛЬСОВие относится к импульсожет быть использованообработки сигналово с тахометрическихдназначено для формиров из пульсирующего сиг нала с дрейфующей постоянной состав-,ляющей. Цель изобретения - повышениестабильности и расширение Функциональных возможностей - достигается путемобеспечения удвоения частоты входного сигнала и возможности использования диеренциального входа. Формирователь импульсов содержит компараторы 1 и 2, делитель 3 опорных напряжений, ББ-триггер 4, логический элемент 5, фильтр 6, интегратор 7,и элемент 8 сложения, Изобретение позволяет расширить область устойчивостиработы и повысить быстродействие Формирователя, Формирователь может бытьреализован в интегральном исполнениина одном кристалле с датчиком, например, с магнитотранзистором. 2 з.п.ф-лы, 5 ил.Изобретение относится к импульсной технике и может быть использовано в устройствах обработки сигналов,преимущественно с тахометрическихдатчиков, и предназначено для формирования импульсов из пульсирующегосигнала с дрейфующей постоянной сос. -тавляющей,Цель изобретения - повышение ста, Обильности и расширение функциональных возможностей за счет обеспеченияудвоения частоты входного:сигнала ивозможности использования дифференциального входа,15На фиг.1 представлена функциональная схема формирователя импульсов;на фиг,2 - временная диаграмма поясняющая его работу; на фиг,З(а,б)примеры реализации элементов сложе 20ния; на фиг,4 - функциональная схемаформирователя импульсов с повышеннымбыстродействием; на фиг.5 - временныедиаграммы, поясняющие его работу,Формирователь импульсов (фиг,1) со держит первый 1 и второй 2 компараторы, делитель 3 опорных напряжений, НЯтриггер 4, логический элемент 5,фильтр б, интегратор 7 и элемент 8сложения, входную и выходную шины,причем первый вход компаратора 1 ивторой вход компаратора 2 подключенысоответственно к первому и второмувыходам делителя Звторой вход компаратора 2 подключен к первому входукомпаратора 2, выходы компаратора 1и 2 подключены соответственно к входам Б и Н триггера 4, и соответственно к первому и второму входам логического элемента 5, выход которого че 40рез фильтр б соединен с выходнойшиной, Выход триггера 4 подключенк первому входу интегратора 7, второй вход котброго соединен с третьимвыходом делителя 3 а выход - к пер 145вому входу элемента 8 сложения, второй вход которого соединен с входнойшиной, а выход подключен ко второмувходу компаратора 1,В формирователе можно испольэовать50различные элементы сложения, для организации дифференциального входа используется элемент сложения 1,фиг.Зб)который содержит пять резисторов иоперационный усилитель. На выходеэлемента 8 сложения формируется сиг 55нал, пропорциональный сумме сигналовмежду вторым и дополнительным входами и первым входом, Коэффициент передачи входного сигнала определяется резисторами Н 2-В 4, для сигнала с выхода интегратора 7 резисторами В 1 и Я 4 аФормирователь импульсов (фиг.4) лополнительно содержит ключ 9, блок 10 управления, причем выход триггера 4 подключен ко входу блока 10 управ. ления, выход которого подключен к управляющему входу ключа 9, выход ключа 9 соединен с третьим входом интегратора 7, первый вход ключа 9 подсоединен к выходу триггера 4 или к шине питания (пунктир).Логический элемент 5 выполняет функцию И-НЕ (фиг, 2 з) в случае отрицательной логики элемент 5 выполняет функцию ИЛИ-НЕ.Устройство работает следующим образом.В исходном состоянии на выходевсех элементов установлено напряжение О (фиг.2), В момент С 1 подаетсянапряжение питания Елг. На выходеинтегратора 7 (фиг,2 в) в этот моментсохраняется напряжение О, а. на выходе схемы сложения 8 (фиг,2 г)реализованной, например, в соответствии с фиг.З а) устанавливается напряжение, меньшее, чем Е 2, которое формируется на втором выходе делителя опорных напряжений 3, в результате чегона выходах компараторов 1 и 2(фиг.2 д,е) и триггера 4 соответственноустанавливаются состояния "1", "0","0", "О" на входе интегратора 7 вызывает линейный рост напряжения наего выходе и на выходе элемента сложе.ния 8 (фиг.2 г),При достижении напряжением уровняЕ 2, компаратор 2 установится в состояние "1", Роста напряжения будетпродолжаться до уровня Е 1, которыйформируется на первом выходе делителя 3, Затем компаратор 1 переключится в "О" и переключит триггер 4 в. Это вызовет линейный спад напряжения на выходе интегратора 7 и элемента сложения 8. Напряжение станетменьше Е и компаратор 1 установитсяв состояние логической "1", Такимобразом, на выходе компаратораформируется импульс, длительность 0которого будет определяться задержками компаратора -1, триггера 4, элемента сложения 8 и быстродействиеминтегратора 7, Состояние триггера 4сохранится и спад будет продолжать55 5 152 ся до тех пор, пока напряжение не достигнет уровня Е 2. Затем компаратор 2 и триггер 4 переключится в состояиние О , что вызовет рост напряжения на выходе интегратора 7 и элемента счожения 8. Далее процесс будет периодически повторяться.Импульсы, Аормируемые компараторами 1 и 2, объединяются в импульсную последовательность удвоенной частоты логическим элементом 5. Фильтр 6.подавляет короткие импульсы и на выходе автоколебания отсутствуют (фиг,2 и)При подаче на вход Аормирователя (момент 12 на диаграмме фиг,2) пульсирующего напряжения, амплитуда переменной составляющей которого больше (Е 1-Е 2) и частота вьппе частоты ав-, токолебаний. Компаратор 1 переключится в состояние "0" при превьппении сигнапа на выходе элемента сложения 8 уровня Е 1. При понижении напряжения ниже уровня Е 2 в состояние "0" будет переключаться .компаратор 2. При несимметрии переменной составляющей сигнала на выходе элемента сложения 8 относительно уровня (Е 1+Е 2)/2 длительности уровней "0" на выходах компараторов 1 и 2 будут неравны, а сигнал на выходе триггера 4 будет отличаться от меандра.Иитегратор 7 будет формировать напряжение, пропорциональное разности между опорным напряжением Ез, которое формируется на третьем выходе делителя опорных напряжений 3 и равно половине размаха сигнала триггера 4, и постоянной составляющей последовательности импульсов на выходе триггера 4. Напряжение на выходе интегратора 7 .суммируется со входным сигналом элементом сложения 8. В результате на выходе его постоянная составляющая сигнала стре-. мится к уровню (Е 1+Е 2)/2, При совпадении этих уровней на выходах компаратора 1 и 2 длительности импульсов становятся равными, а на выходе триг" гера 4 появляется меандр.Изменяя величину Е можно регулировать скважность импульсов на выходе триггера 4. Длительность импульсов на выходах компараторов 1 и 2 при воздействии входного сигнала определяется временем, в течение которого сигнал на выходе схемы сложения будет больше (меньше) уровня Е 1 (Е 2), Эта длительность много больше длительности импульсов автоколебаний 2388 6 В связи с большой разницей длительностей импульсов антоколебаний иимпульсов, сАормированных из входногосигнала, фильтр 6 эффективно подавляет автоколебания и полностью пропускает рабочие импульсы,Например, при использовании микросхем серий К 521, К 561 и К 40 длительность импульсов автоколебаний составила порядка 10 мкс, а длительность импульсов с датчиков не менее 10 мс,что обеспечивает эффективную работуАильтра.Таким образом, В формирователедостигается автоматическая настройка порога срабатывания на уровень постоянной составляющей входного сигнала, что позволяет компенсировать 20 дрейф и расширить область устойчивойработы по входному сигналу, а такжедостигнуто удвоение частоты входного сигнала.Формирователь с повышенным быстро 25 действием (фиг.4) работает следующим образом,При подаче напряжения питания триггер 4 устанавливается в состояние"О" (фиг,5). При этом блок управления10 удерживает ключ 9 в открытомсостоянии (на фиг.5 в показан токчерез ключ 9). Этим достигается быстрый рост напряжения на выходе интегратора 7 фиг.5 б) при включении пи в .тания и соответственно малое время35установления рабочего режима, Послевключения питания по фронту первого, импульса блок управления 10 (Аиг.5 г)изменит свое состояние и закрывает40 ключ 9.Интегратор 7 начинает работать сбольшой постоянной времени. Импульсыследующие после первого, не изменяют состояние блока управления 10,Для приведения блока управления в исходное состояние необходимо выключить питание.Возможная реализация блока управления 10 приведена на Аиг,4, Логи 50 чески она представляет собой схему ИЛИ, один из входов которой соединен с ее выходом, Она содержит три п-канальных МОП - транзистора 11-13 и два р-канальных МОП - транзистора 14 и 15. Затвор транзистора 11 является входом блока управления, стоки транзисторов 11 и 12, исток транзис - тора 13 и затвор транзистора 14 соединены, истоки транзисторов 11 и 121522388 7соединены с затвором и стоком транзистора 15 и шиной питания. Затвор и сток транзистора 13 соединены с истоком транзистора 14 и со второй шиной питания. Сток транзистора 14 сое 5 динен с истоком транзистора 15 и с выходом блока управления, Затвор, транзистора 12 соединен со стоком транзистора 14.Предлагаемая схема имеет два устойчивых состояния: транзисторы 11- 15 закрыты, через транзисторы 11 - 15 протекает ток.При включении и нулевом напряжении на затворе транзистора 11 блок управления 10 всегда установится в первое состояние, Транзистор 11 откро. ется при подаче на его затвор "1", что вызывает открывание транзистора 14, напряжение на его стоке начнет возрастать и откроет транзистор 12. Схема перейдет во второе состояние и сохранит его при дальнейших воздействиях на ее Входе. 25Таким образом, .устройство позволяет расширить область устойчивости . работы и функциональные возможности, повысить его быстродействие. Изобретение позволяет также реализовать формирователь в интегральном исполнении на одном кристалле с датчиком . например, с магнитотранзистором, получив таким образом функционально законченный прибор.35 Формула изобретения1, Формирователь импульсов, содержащий первую входную шину, выходную шину, шину питания, два компаратора,делитель опорных напряжений и Ж-триггер, прн этом .первый вход первогои второй вход второго компараторовсоединены соответственно с первым ивтор входами дели т еля оп орйых нап 45 ряжений, второй Вход первого компаратора соединен с первым входом второго компаратора, а выходы компараторов соединены соответственно с Б- и Н-входами,ВБ-.триггера, о т л и - ч а ю щ и й с. я тем, что, с целью повьппения стабильности и распирения функциональных возможностей; введены логический элемент, фильтр, интегратор, элемент сложения и вторая входная шина, причем выходы первого и второго компараторов соединены соответственно с первым и вторым входами логического элемента, выход которого соединен с входом фильтра, выход которого соединен с выходной шиной выход ББ-триггера. соединен с первым входом интегратора, второй вход которого соединен с третьим выходом делителя опорных напряжений, выход интегратора соединен с первым входом элемента сложения, второй вход которого соединен с первой входной шиной, дополнительный вход - с второй входной шиной, а выход - с вторым входом первого компаратора.2. Формирователь по п.1, о т л ич а ю щ и й с я тем, что элемент сложения содержит первый, второй, третий, четвертый и пятый резисторы и усилитель, причем первые выводы первого, второго и третьего резисторов подключены соответственно к первому, второму и дополнительному входам элемента сложения, первый вход усилителя соединен с вторыми выводами первого и второго резисторов и первым выводом четвертого резистора, второй вывод которого соединен с выходом усилителя, являющимся выходом элемента сложения, второй вход усилителя соединен с вторым выводом третьего резистора и с первым выводом пятого резистора, второй вывод которого соединен с общей шиной.3. Формирователь по п,1, о т л ич а ю щ и й с я тем, что с целью повышения быстродействия, в него вве - дены ключ и блок управления, причем выход ВБ-триггера соединен с входом блока управления, выход которого соединен с управляющим входом ключа, выход ключа соединен с третьим входом интегратора, а первый вход ключа подключен к выходу триггера или к шине питания.

СмотретьЗаявка

4322437, 23.09.1987

ЛЕНИНГРАДСКОЕ НАУЧНО-ПРОИЗВОДСТВЕННОЕ ОБЪЕДИНЕНИЕ "ЭЛЕКТРОНМАШ"

ЛЕТЮХИН ДМИТРИЙ АНДРЕЕВИЧ, БРАЙЛОВСКИЙ ГЕННАДИЙ СЕНДЕРОВИЧ

МПК / Метки

МПК: H03K 5/01

Метки: импульсов, формирователь

Опубликовано: 15.11.1989

Код ссылки

<a href="https://patents.su/6-1522388-formirovatel-impulsov.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь импульсов</a>

Предыдущий патент: Формирователь импульсов управления

Следующий патент: Устройство для контроля последовательности импульсов

Случайный патент: Способ нейтрализации конечного шлака