Модуль для формирования признака переполнения и кода нормализации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1501041

Авторы: Заблоцкий, Самусев, Шостак, Яскульдович

Текст

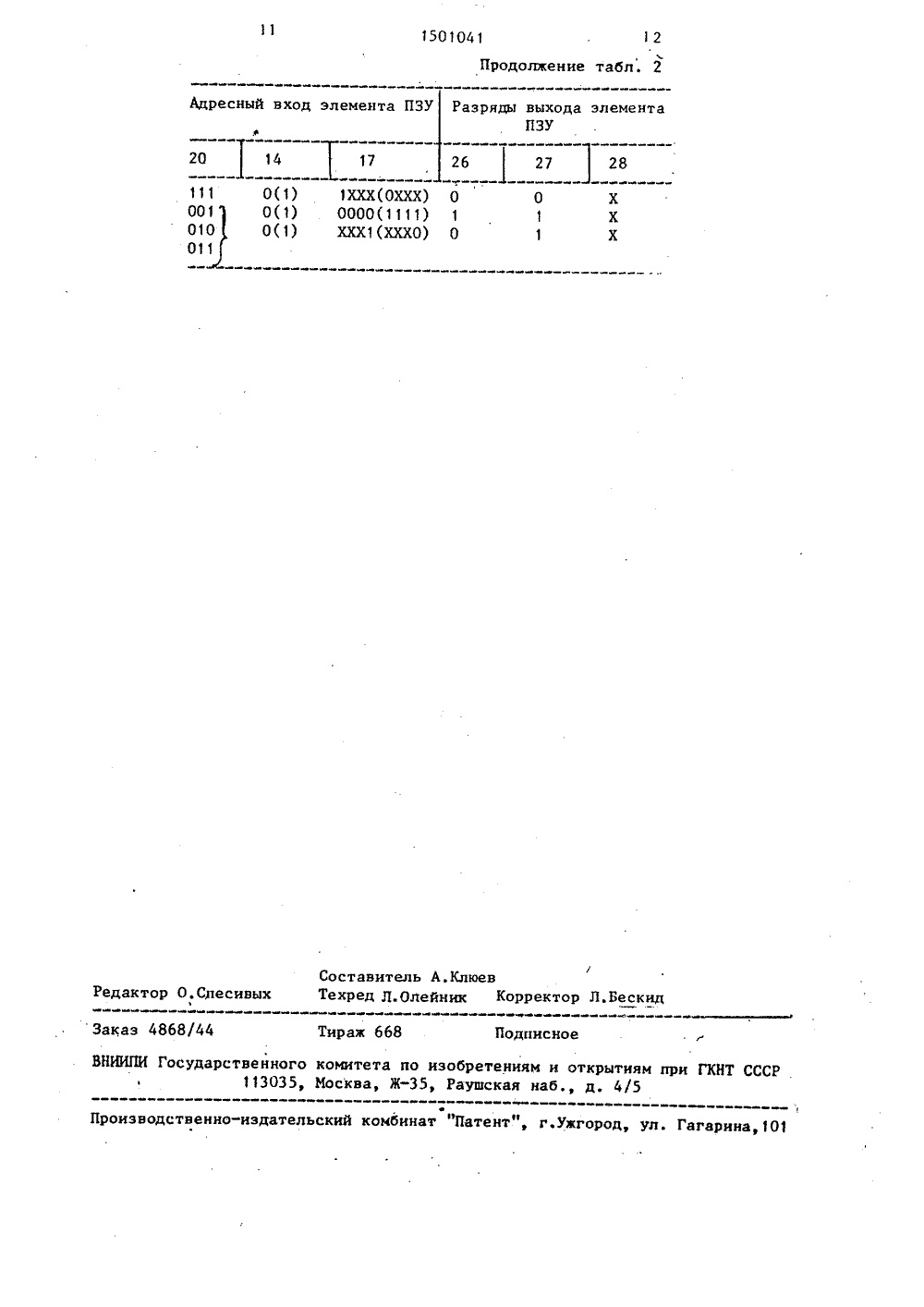

(51) ГОСУДАРСТВЕННЫЙ КОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯПРИ ГКНТ СССР ОПИСАНИЕ ИЗОБРЕТЕНИЯ Р 30 А.А.Самусев,скульдович детельство ССС 6 Р 7/38, 1985 тельство СССРГ 7/38, 1985 ФОРМИРОВАНИЯ ПРИЗНА- И КОДА НОРМАЛИЗАЦИИ относится к вычисли- и может быть испольоения устройств фор(54) МОДУЛ КА ПЕРЕПОЛ (57) Изобр тельной те зовано для ДЛЯЕНИЯ тен ике Ж ост ЮФ ТОРСКОМУ СВИДЕТЕЛЬСТ(21) 4379763/24-2 (22) 18.02.88 (46) 15.08.89, Бю (72) В,Н.Заблоцки А.А.Шостак и А.В. (53) 681. 325(088. (56) Авторское св Иф 1345351, кл. САвторское свид Р 1331315, кл. С мирования кода нормализации и признака переполнения при арифметическихсдвигах влево в цифровых вычислительных машинах и системах. Целью изобретения является сокращение аппаратурных затрат, Поставленная цель достигается тем, что модуль для Формирования признака переполнения и кода нормализации, содержащий узлы 1 и 2шифрации, элемент И-НЕ 4 и узел 5коммутации, содержит группу элементовИ 3, при этом узел 5 коммутации содержит элемент И 6, элемент НЕ 7 иэлементы И-НЕ 8-13 с соответствующимися связями. 1 з.п. ф-лы, 1 ил.,2 табл.31501041Изобретение относится к области вычислительной техники и может быть использовано для построения устройств формирования кода нормализации и при 5 знака переполнения при арифметических сдвигах влево в цифровых вычислительных машинах и системах.Целью изобретения является сокращение аппаратурных затрат. 10На чертеже представлена схема модуля для формирования признака переполнения и кода нормализации.Модуль содержит первый и второй узлы 1 и 2 шифрации соответственно, 15 группу элементов И 3, элемент И-НЕ 4, узел 5 коммутации, содержащий элемент И 6, элемент НЕ 7, с первого по шестой элементы И-НЕ 8-13 соответственно, знаковый вход 14 модуля, ин формационный вход 15 модуля, первые входы 16 и 17 соответственно узлов 1 и 2 шифрации, вход 18 задания величи-ны сдвига модуля, вход 19 задания режима модуля, прямые выходы 20 элементов И 3 группы, первый управляющий вход 21 узла 5 коммутации, вход 22 блокировки модуля, первую группу информационных входов 23-25 узла 5 коммутации, вторую группу информацион ных входов 26-28 узла 5,коммутации, выход 29 признака нуля модуля, выход 30 признака переполнения модуля, выход 31 кода нормализации модуляЦифры около линий разрядов на чертеже обозначают количество или номера разрядов.Узлы 1 и 2 предназначены для анализа значений кода на входах соответственно 16,17 с учетом значений кодов 40 на входе 14 и выходе 20, могут быть построены на элементах постоянных запоминающих устройств (ПЗУ), Каждый узел. 1 или 2 содержит один элемент ПЗУ, разряды адресного входа которо го соединены с входами разрядов входов 16 или 17, 14 и выхода 20. Соответствующие ра ряды выхода элемента ПЗУ в узле 1 или 2 соединены с входами 23 - 25 или 26 - 28.Элементы ПЗУ в узле 1 и 2 кодируются в соответствии с табл. 1 и 2. Вместо элементов ПЗУ могут быть использованы программируемые логические матрицы.55Модуль функционирует следующим образом.Б исходном состоянии на входе 15 устанавливается анализируемый информационный двоичный код. На входе 14 устанавливается код знака, На входе 18 устанавливается код величины сдвига. На входе 19 устанавливается код признака, например арифметического сдвига влево, или код признака нулевого сдвига, равныесоответственно "1" и "0". На входе 22 устанавливается сигнал блокировки, равный "0", при котором модуль блокируется, т.е, на выходах 30, 31 устанавливаются единичные коды. При этом на выходе 29 формируется код признака 0", равный "1", если значения всех бит входа 15 равны значению знака на входе 14, или пОп в противном случае.Код признака нуля на выходе 29 формируется независимо от значения управляющих кодов на входах 18,19,22. Код признака нуля независимо формируется для групп бит на входах 16 и 17 в узлах соответственно 1 и 2, на входах соответственно 23 и 26 (см. табл1 и 2). С помощью элемента И 6 в узле 5 сигналы с входов 23,26 объединяются. Т.е. если коды на входах 16 и 17 равны нулю, то на выходе 29 появляется логический сигнал, равный "1". При " 1" на входе 22 модуль функционирует и по выходам 30, 31.При установке на входе 19 "1".код с входа 18 передается на выход 20 и модуль функционирует в режиме формирования признака переполнения, код которого формируется на выходе 30. Если значение кода на выходе 20 меньше или равно к, где к - количество разрядов входа 16, то сигнал признака переполнения Формируется только на входе 24 с учетом результата анализа только кода на входе 16При этом на входе 27 устанавливается "1", независимо от значения кода на входе 17, Если же код на выходе 20 больше к, то код признака переполнения формируется и на входе 27 с учетом значений кода на входе 17 и значения кода на выходе 20, равного (М-к), где М - код на выходе 20.Сигналы с входов 24,27 объединяются элементом И-НЕ 10, если код ве-, личины сдвига не равен нулевому и на входе 21 сформирована "1". Т.е, при отсутствии переполнения на входах 24, 27 формируются "1" (см, табл. 1 и 2), благодаря чему (так как на всех входах элемента И-НЕ 10 сформированы "1") на выходе 30 установится "0".5 1501041Если имеет место переполнение (т.е.количество бит слева на входе 15,равных коду знака на входе 14, меньше значения величины сдвига, заданной кодом на входе 18), то хотя бына одном входе 24 или 27 установится0, благодаря которому на выходе 30устанавливается "1",При нулевом коде величины сдвигана входе 18 на входе 21 устанавливается "О", благодаря которому на выходе 30 устанавливается "1", означающая,что переполнение отсутствует, так каконо невозможно,При этом модуль переходит в режимформирования кода нормализации, Длязадания режима Формирования кода нормализации используется также вход 19,на котором для этого устанавливается0, что эквивалентно установке навходе 18 нулевого кода.При этом на входах 24,25 при ненулевом коде на входе 16 формируетсякод нормализации с инверсными значениями бит дпя кода на входе 16 (см,табл.1). Благодаря нулевому коду навходе 23 блокируются элементы НЕ 7,И-НЕ 8,9, на выходах которых устанавливается "1". На выходе элемента 11устанавливается 0.В результате на выходах элементовИ-НЕ 11 - 13 и, следовательно, на выходе 31 Формируется прямой код нормализации. При нулевом коде на .входе 1635на входах 23 - 25 устанавливается единичный код, Параллельно Формируемыйкод нормализации на входах 27,28 (см.табл.2) для группы разрядов кода навходе 17 транзитом передается на выходы элементов И-НЕ 12, 13. На выходеэлемента И-НЕ 11 устанавливается единичный,код, так как на входе 23 устанавливается "1", которая транзитомпередается на выход элемента И-НЕ 11.В результате на выходе 31 формируется прямой код нормализации.Если на входе 17 установлен нулевой код, то на входах 27,28 формируется единичный код, который транзи"том передается на выходы элементовИ-НЕ 12, 13. Параллельно на выходе 29формируется единичный код. 40 45 50 55 Модуль может быть использован вкачестве ячейки шифрации в устройстведля.формирования кода нормализации ипризнака переполнения. При этом нетребуется блок дешифраторов, так какС в качестве выхопов пеши,ряторов можно использовать выходы 29 мопупя,Устройство строится с помощью модуля следующим образом,Строится блок ячеек шиФрации, вкотором вместо ячеек ыифрации используется модуль. Т.е. блок ячеек шифрации содержит ; модулей, гле Ь - ко 10 .Иличество разрядов информационноговхода устройства. Выходы модулей соединены с соответствующими выходамиблока, а информационные входы модулей соединены с соответствующимигруппами из И соседних разрядов информационного входа блока и устройства.Одноименные управляющие входы иРазряды управляющих входов 19, 18 изнаковый вход всех моцулей соединяются между собой и соединяются с соответствующими входами блока и устройства. При этом входы 18 соединяются25 с первым входом задания величинысдвига устройства (младшими разрядами кода величины сдвига). Группа элементов И 3 и элемент И-НЕ 4 могутбыть общими для всех модулей блока. Входы 22 для всех модулей в блоке, кроме крайнего левого модуля, соединяются с соответствующими разрядами входа блокировки (ипи управляющего) блока, Вход 22 крайнего левого модуля в блоке соединен с входом "1". Преобразователь кода содержит модуль и дешифратор границ, вход деыиФратора границ и информационный вход модуля связаны соответствующими разрядами между собой и с выходом блока ячеек ыифрации, разряды которого соединены с выходами 29 модулей в блоке ячеек ыифрации. Выход дешифратора границ соответствующими разрядами соединен.с входом блокировки (управляющим входом) блока ячеек шифрации.Входы 14 и 22 модуля в преобразователе кода соединены с входом "1", Вход 18 модуля в преобразователе кода соединен с вторым входом задания величины. сдвига (старшими разрядами кода величины сдвига). Вход 19 модуля в преобразователе кодов соединен с входом признака сдвига блока шифраторов и устройстваВыход 29 модуля в преобразователе кода соединен с выходом признака нуля устройства.Соединение разрядов выходов 31 модулей в блоке ячеек шифрации и впреобразователе осуществляется также, как и выходов ячеек шифрации визвестном устройстве. Выходы 30 модулей блока ячеек шифрации и модуляв преобразователе соединены с соответствующими входами дополнительногоэлемента И, выход которого соединенс выходом признака переполнения устройства. Информационный вход блокаячеек шифрации, кроме крайнего правого разряда, соединен с информационным входом устройства, Крайний правый разряд ииформационного входаблока ячеек шифрации соединен с входом "0",Таким образом, с помощью модуляможно строить многоразрядные устройства для формирования кода нормализации и признака переполнения,Формула изо бре тения251. Модуль для Формирования признака переполнения и кода нормализации,содержащий первый и второй узлы шифрации,. элемент И-НЕ и узел коммутации, причем выход элемента И-НЕ .соединен с первым управляюцим входом узла коммутации, о т л и ч а ю щ и й -с я тем, что, с целью сокращения аппаратурных затрат,. он содержитгруппу элементов И, причем входы старших и младших разрядов информационно 35го входа модуля соединены с входамиразрядов первых входов первого и второго узлов ыифрации соответственно,вторые входы которых объединены и соединены со знаковым входом модуля,входы разрядов входа задания величины сдвига которого соединены с первыми входами соответствуюцих элементов И группы, вторые входы которыхсоединены с входом задания режима модуля, прямые выходы элементов И группы соединены с входами соответствуютщих разрядов третьих входов первогои второго узлов шифрации, выходы разрядов которых соединены соответствен 50но с ийформационнйми входами первой и второй групп узла коммутации, второй управляющий вход которого соединен с входом блокировки модуля, инверсные выходы элементов И группы соединены с соответствующими входами элемента И-НЕ, выходы группы узла коммутации являются соответственно выходами признака нуля, признака переполнения и кода нормализации модуля12. Модуль по и. 1, о т л и ч а ющ и й с я тем, что узел коммутациисодержит элемент НЕ, элемент И, первый, второй, третий, четвертый, пятый ишестой элементы И-НЕ, причемпервый информационный вход первойгруппы узла коммутации соединен спервыми входами элемента И, первогои второго элементов И-НЕ, с входомэлемента НЕ, второй управляющий входузла коммутации соединен с первымивходами элементов И-НЕ с третьегопо шестой, выход элемента НЕ соединен с вторым входом четвертого элемента И-НЕ, первый уцравляющий входузла коммутации соединен с вторымвходом .третьего элемента И-НЕ, третий вход которого соединен с вторымвходом пятого элемейта И-НЕ и с вторым информационным входом первойгруппы узла коммутации, третий информационный вход первой группы которого соединен с вторым входом шестого элемента И-НЕ, третий вход которого и третий вход пятого элементаИ-НЕ соединены с выходами соответственно второго и первого элементовИ-НЕ, первый информационный вход второй группы узла коммутации соединенс вторым входом элемента И, второйинформационный вход второй группы,узла коммутации соединен с вторымвходом первого элемента И-НЕ и с четвертым входом третьего элемента И-НЕ,третий информационный вход второйгруппы узла коммутации соединен свторым входом второго элемента И-НЕ,выходы элемента И и третьего элемента И-НЕ являются первым и вторымвыходами группы узла коммутации, выходы разрядов третьего выхода группы которого соединены соответственнос выходами четвертого, пятого и шестого элементов И-НЕ,1501041 Адресный Раэряды выхода элемента ПЗУ.. элемента ПЗУ вход 23 24 25 20 16 14 0000(1111) О 0 О 1 (1110) оо 1 х(11 ох) о 1 хх(10 хх) 1 ххх(оххх) оооо(11) оао 1(111 о)1 ххх(оххх) оооо(1111) ооо 1(111 о) о о х х И И И х х х И И Но 1 хх(1 охх) 1 ххх(оххх)оооо(1111)ооо 1(11.1 о)001 Х(110 Х) х х х х о о о И И Н1 ххх(оххх)оооо(1111)0001(1110) х х х И Н1 ххх(оххх) о х Адресный вход элемента ПЗУ го оооо(1111) о(1) о о х х ее х х х о ооо ооо 1(111 о) оо 1 х(11 ох) о 1 хх(1 охх) О(1) о(1) о(1) ооо ооо ооо ооо оооо(1111) О(1) 1 О 1101И1 О 111 О110И11 О110111 ооо 1(111 о)о(1) ИТаблица 2 Разряды выхода элементаПЗУ 26 21 2815010412 Продолжение табл. 2 Адресный вход элемента ПЗУ Разряды выхода элементаПЗУ/Составитель А.КлюевТехред Л.Олейник Корректор Л.Бескид Редактор О,СлесивыхИ4ЮМю ю юЗаказ 4868/44 Тираж 668 Подписноег ВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР 1 113035, Иосква, Ж, Раушская наб., д. 4/5 Производственно-издательский комбинат "Патент", г.Ужгород, ул. Гагарина, 101

СмотретьЗаявка

4379763, 18.02.1988

ПРЕДПРИЯТИЕ ПЯ М-5339

ЗАБЛОЦКИЙ ВЛАДИМИР НИКОЛАЕВИЧ, САМУСЕВ АНАТОЛИЙ АЛЕКСЕЕВИЧ, ШОСТАК АЛЕКСАНДР АНТОНОВИЧ, ЯСКУЛЬДОВИЧ АЛЕКСАНДР ВАДИМОВИЧ

МПК / Метки

МПК: G06F 7/38

Метки: кода, модуль, нормализации, переполнения, признака, формирования

Опубликовано: 15.08.1989

Код ссылки

<a href="https://patents.su/6-1501041-modul-dlya-formirovaniya-priznaka-perepolneniya-i-koda-normalizacii.html" target="_blank" rel="follow" title="База патентов СССР">Модуль для формирования признака переполнения и кода нормализации</a>

Предыдущий патент: Вычислительное устройство

Следующий патент: Четырехуровневый одноразрядный сумматор

Случайный патент: Устройство для передачи телеметрической информации