Дельта-модулятор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1425838

Автор: Тимченко

Текст

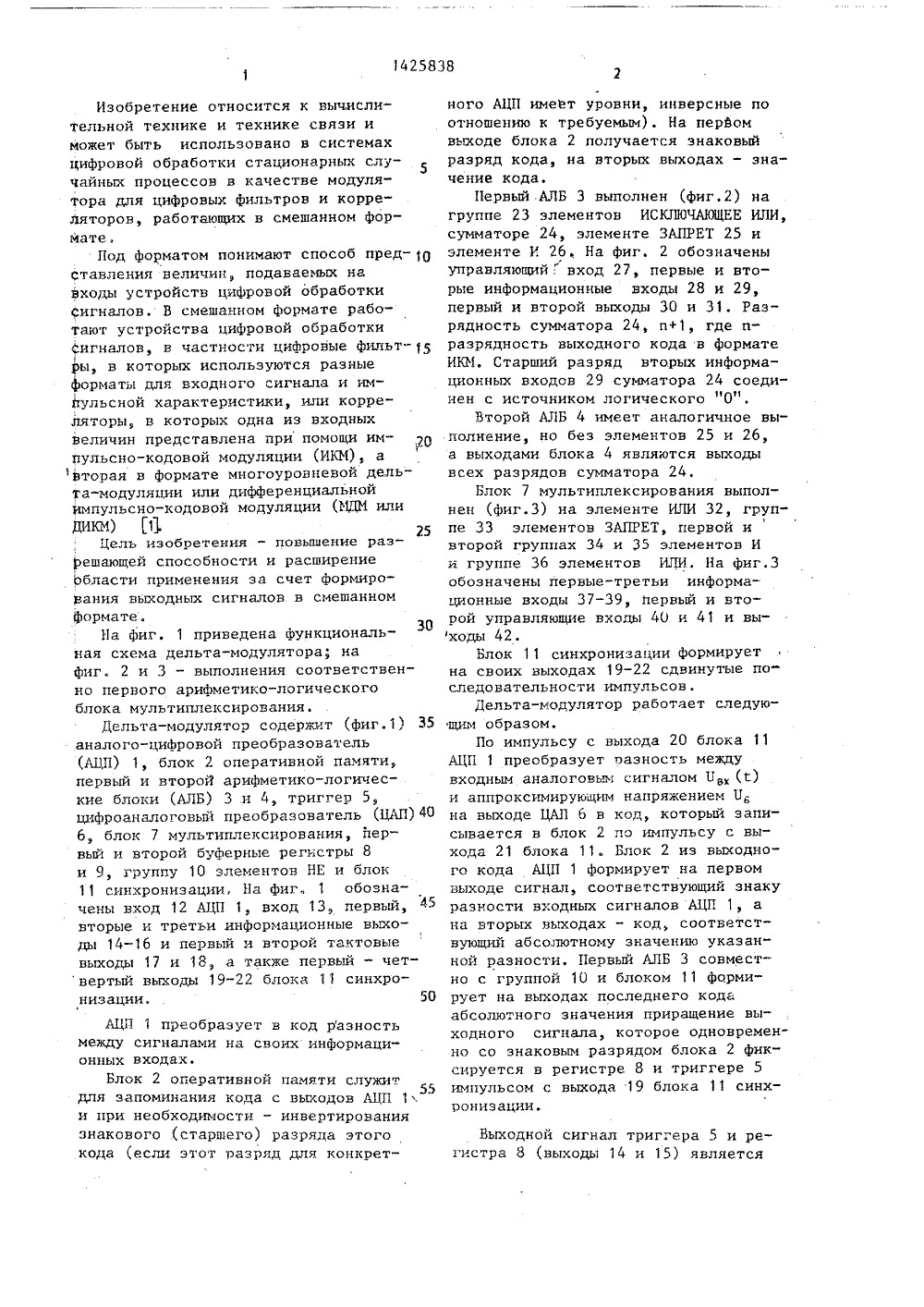

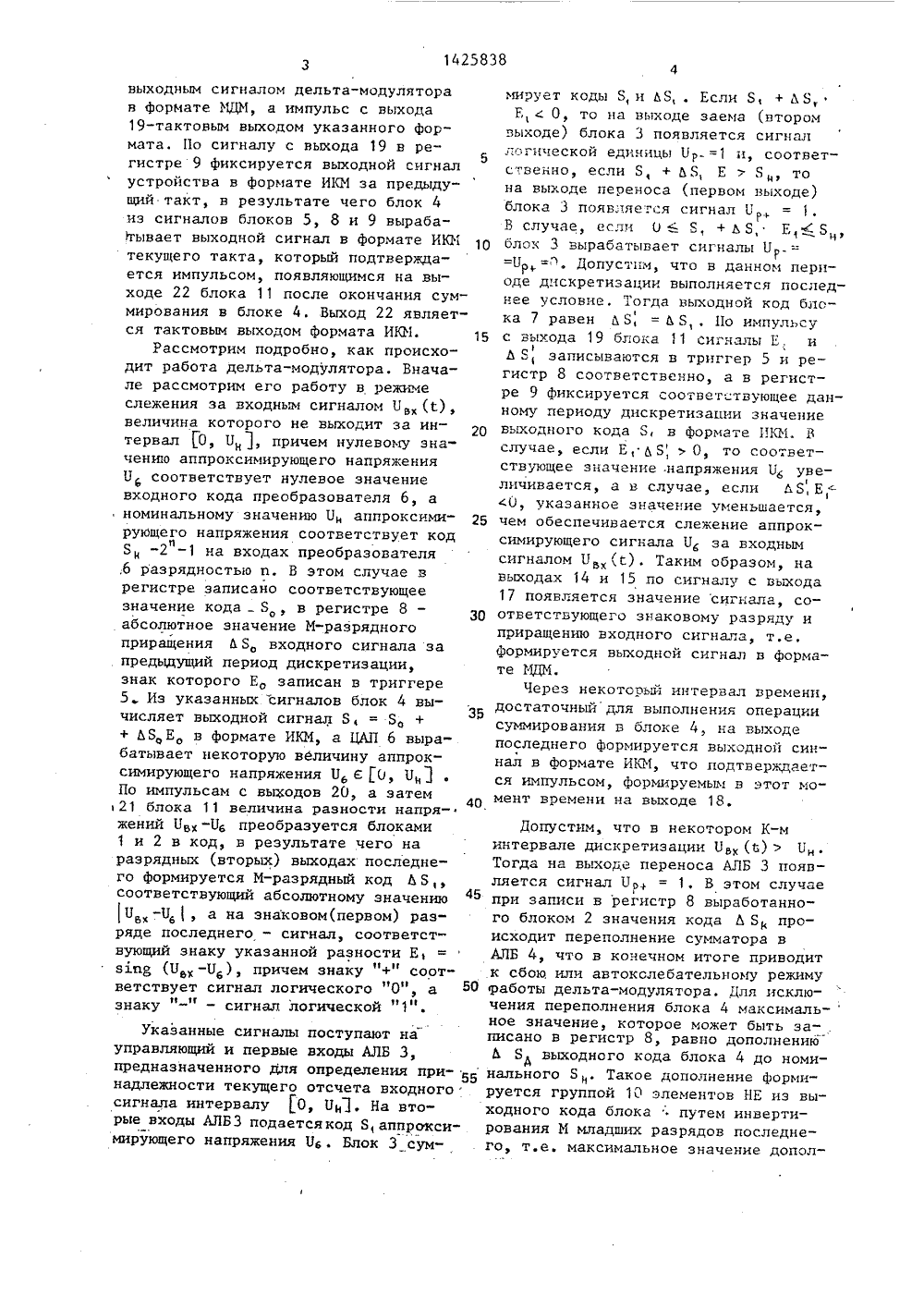

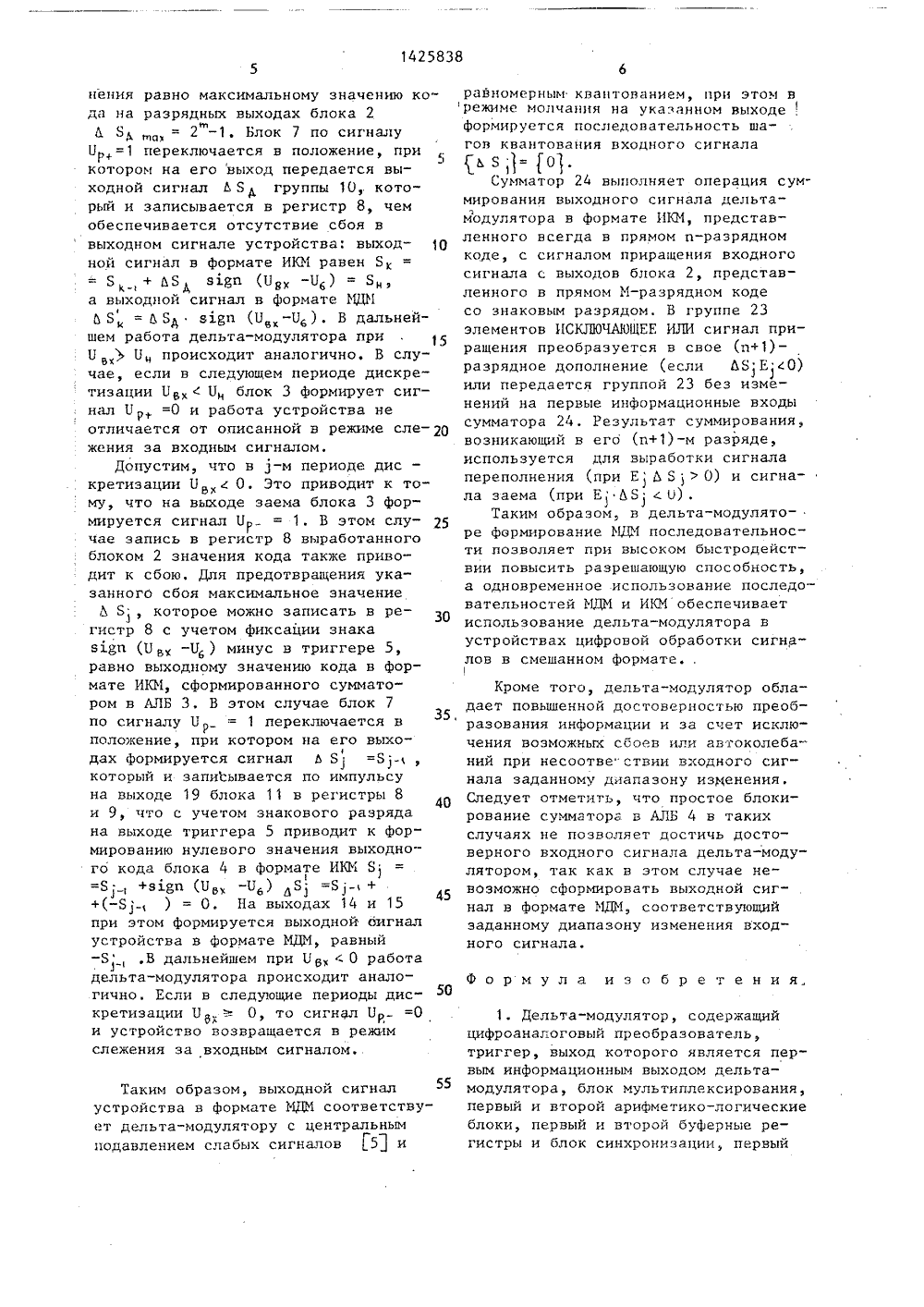

,.ЯО СЮ 1 Н ОЗ Г 1 3 ИСАНИЕ ИЗОБРЕТЕНИЯ ССР3. 82.СССРМЗ/ ьнциал я, М .2.1 СССР МЗ/2,ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ЛЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ Я А ВТОРСКОМУ СВИДЕТЕЛЬСТВУ(56) 1. Доклады АН УССР, сер.А,1983, У 4, с. 73-77.2. Авторское свидетельство СУ 1112552, кл. Н 03 М 3/02, 1983. Авторское свидетельство ССУ 1149411, кл. Н 03 М 3/02, 194. Авторское свидетельствопо заявке У 4047426/24,кл.Н 031986.,5. Харатишвили Н,Г. Дифференая импульсно-кодовая модуляциРадио и связь, 1982, .с.24, рисб, Авторское свидетельствопо заявке Р 4101636/24,кл.Н 031986.(54) ДЕЛЬТА-МОДУЛЯТОР (57) Изобретение относится к вычислительной технике и технике связи. Использование иэобретечия в системах цифровой обработки случайных процессов позволяет повысить разрешающую способность и расширить область применения за счет формирования выходных сигналов в смешанном формате. Дельта- модулятор содержит арифметико-логические блоки 3,4, триггер 5, цифроана 3 логовый преобразователь 6, блок 7 мультиплексирования, буферные регистры 8,9 и блок 11 синхронизации. Благодаря введению аналого-цифрового преобразователя 1, блока 2 оператив- о ной памяти и группы 10 элементов ИСКЛ 10 ЧАЮЩЕЕ ИЛИ в дельта-модуляторе обеспечивается формирование выходных Сф сигналов как в формате импульсно- кодовой модуляции, так и в формате многоуровневой дельта-модуляции. 2 з.п, ф-лы, 3 ил.Изобретение относится к вычислительной технике и технике связи иможет быть использовано в системахцифровой обработки стационарных случайных процессов в качестве модулятора для цифровых фильтров и корреляторов, работающих в смешанном формате.Под форматом понимают способ предСтавления величин, подаваемых навходы устройств цифровой обработкиСигналов. В смешанном Формате рабоТают устройства цифровой обработкиСигналов, в частности цифровые фильтры, в которых используются разныеформаты для входного сигнала и имПульсной характеристики, или корреляторы, в которых одна из входныхВеличин представлена при помощи импульсно-кодовой модуляции (ИКИ), аВторая в формате многоуровневой дельта-модуляции или дифференциальнойимпульсно-кодовой модуляции (МДМ илиДИКМ) 1,25Цель изобретения - повышение разрешающей способности и расширениеобласти применения за счет формирования выходных сигналов в смешанномФормате.На Фиг. 1 приведена функциональная схема дельта-модулятора; нафиг. 2 и 3 - выполнения соответственно первого арифметико-логическогоблока мультиплексированияДельта-модулятор содержит (фиг.1) 35аналого-цифровой преобразователь(АЦП) 1, блок 2 оперативной памяти,первый и второй арифметико-логические блоки (АЛБ) 3 и 4, триггер 5,цифроаналоговый преобразователь (ЦАП) 406, блок 7 мультиплексирования, первый и второй буферные регистры 8и 9 группу 10 элементов НЕ и блок11 синхронизации, На фиг. 1 обозначены вход 12 АЦП 1, вход 13, первый, 45вторые и третьи информационные выходы 14-16 и первый и второй тактовыевыходы 17 и 18, а также первый - четвертыи выходы 19-22 блока 11 синхронизации. 50АЦП 1 преобразует в код разностьмежду сигналами на своих информационных входах.Блок 2 оперативной памяти служит55 для запоминания кода с вьподов АЦП 1,и при необходимости - инвертирования знакового (старшего) разряда этого кода (если этот разряд для конкретного АЦП имеет уровни, инверсные поотношению к требуемым). На первомвыходе блока 2 получается знаковыйразряд кода, на вторых выходах - значение кода.Первый АЛБ 3 выполнен (фиг,2) нагруппе 23 элементов ИСКЛЮЧАЮЩЕЕ ИЛИ,сумматоре 24, элементе ЗАПРЕТ 25 иэлементе И 26, На Фиг, 2 обозначеныуправляющий:" вход 27, первые и вторые информационные входы 28 и 29,первый и второй выходы 30 и 31. Разрядность сумматора 24, и+1, где празрядность выходного кода в форматеИКИ, Старший разряд вторых информационных входов 29 сумматора 24 соединен с источником логического "0,Второй АЛБ 4 имеет аналогичное выполнение, но без элементов 25 и 26,а выходами блока 4 являются выходывсех разрядов сумматора 24,Блок 7 мультиплексирования выполнен (фиг.З) на элементе ИЛИ 32, группе 33 элементов ЗАПРЕТ, первой ивторой группах 34 и 35 элементов Ии группе 36 элементов ИЛИ На фиг.Зобозначены первые-третьи информационные входы 37-39, первый и второй управляющие входы 40 и 41 и выходы 42.Блок 11 синхронизации формируетна своих выходах 19-22 сдвинутые последовательности импульсов.Дельта-модулятор работает следующим образом.По импульсу с выхода 20 блока 11АЦП 1 преобразует разность междувходным аналоговым сигналом П(1)и аппроксимирующим напряжением П;на выходе ЦАП 6 в код, который записывается в блок 2 по импульсу с выхоца 21 блока 11. Блок 2 из выходного кода АЦП 1 Формирует на первомвыходе сигнал, соответствующий знакуразности входных сигналов АЦП 1, ана вторых выходах - код, соответствующий абсолютному значению указанной разности. Первый АЛБ 3 совместно с группой 10 и блоком 11 формирует на выходах последнего кодаабсолютного значения приращение выходного сигнала, которое одновременно со знаковым разрядом блока 2 фиксируется в регистре 8 и триггере 5импульсом с выхода 19 блока 11 синхронизации.Выходной сигнал триггера 5 и регистра 8 (выходы 14 и 15) являетсявыходным сигналом дельта-модуляторав формате МДМ, а импульс с выхода19-тактовым выходом указанного формата, По сигналу с выхода 19 в ре 5гистре 9 фиксируется выходной сигналустройства в формате ИКМ за предыдущий такт, в результате чего блок 4иэ сигналов блоков 5, 8 и 9 вырабатывает выходной сигнал в формате ИКМтекущего такта, который подтверждается импульсом, появляющимся на выходе 22 блока 11 после окончания суммирования в блоке 4. Выход 22 является тактовым выходом формата ИКМ. 15Рассмотрим подробно, как происходит работа дельта-модулятора. Вначале рассмотрим его работу в режимеслежения за входным сигналом 11 (С),величина которого не выходит за интервал 0, 11 , причем нулевому значению аппроксимирующего напряжения11 соответствует нулевое значениевходного кода преобразователя 6, аноминальному значению 11 аппроксимирующего напряжения соответствует кодБ -2 -1 на входах преобразователяи,6 разрядностью и. В этом случае врегистре записано соответствующеезначение кода Б , в регистре 8 -абсолютное значение М-разрядногоприращения Ь Б, входного сигнала запредыдущий период дискретизации,знак которого Е записан в триггере5 Из указанных сигналов блок 4 вычисляет выходной сигнал Б, = Б +Эб+ ЬБ Е, в формате ИКМ, а ЦАП 6 вырабатывает некоторую величину аппроксимирующего напряжения Ц Е 0, 11По импульсам с выходов 20, а затем21 блока 11 величина разности напряжений 11 в -О 6 преобразуется блоками1 и 2 в код, в результате чего наразрядных (вторых) выходах последнего формируется М-разрядный код Ь Бсоответствующий абсолютному значению 45О-О (, а на знаковом(первом) разряде последнего - сигнал, соответствующий знаку указанной разности Е,81 п 8 (11-0), причем знаку + соответствует сигнал логического "О", а 50знаку "-" - сигнал логической "1".Указанные сигналы поступают на управляющий и первые входы АЛБ 3, предназначенного для определения при- б 5 надлежности текущего отсчета входного сигнала интервалу О, 11 Д, На вторые входы АЛБЗ подаетсякод Б, аппроксимирующего напряжения 0. Блок 3 суммирует коды Я, и ЬЯ, . Если Б, + ЬБ,Е, - О, то на выходе заема (второмвыходе) блока 3 появляется сигналлогической единицы 11 р =1 и, соответственно, если Б, + ЬЯ, ЕБ , тона выходе переноса (первом выходе)блока 3 появляется сигнал О.,В случае, если О = Я, + Ь Я, ЕБн,блок 3 вырабатывает сигналы 11=11=д. Допустим, что в данном периоде дискретизации выполняется последнее условие, Тогда выходной код блока 7 равен Ь Б, = Ь Б По импульсус выхода 19 блока 11 сигналы Е. исЬ Я, записываются в триггер 5 и регистр 8 соответственно, а в регистре 9 фиксируется соответствующее данному периоду дискретизации значениевыходного кода Я, в формате ИКМ, Вслучае, если Е, Ь Б,О, то соответ -ствующее значение .напряжения Ц увеличивается, а в случае, если Ь Б,Е,(О, указанное значение уменьшается,чем обеспечивается слежение аппроксимирующего сигнала 11 эа входнымсигналом 11 (С). Таким образом, навыходах 14 и 15 по сигналу с выхода17 появляется значение сигнала, соответствующего знаковому разряду иприращению входного сигнала, т.е.формируется выходной сигнал в формате МДМ.Через некоторый интервал времени,достаточный для выполнения операциисуммирования в блоке 4, на выходепоследнего формируется выходной синнал в формате ИКМ, что подтверждается импульсом, формируемым в этот момент времени на выходе 18. Допустим, что в некотором К-м интервале дискретизации 0 в(б)Ь, Тогда на выходе переноса АЛБ 3 появляется сигнал 11 = 1. В этом случае при записи в регистр 8 выработанного блоком 2 значения кода Ь Б происходит переполнение сумматора в АЛБ 4, что в конечном итоге приводит к сбою, или автокслебательному режиму работы дельта-модулятора. Для исключения переполнения блока 4 максималь-ное значение, которое может быть за- . писано в регистр 8, равпо дополнению Ь Б выходного кода блока 4 до номиДнального Б . Такое дополнение формируется группой 1 О элементов НЕ из выходного кода блока путем инвертирования М младших разрядов последнего, т.е. максимальное значение допол 1425838нения равно максимальному значению кода на разрядных выходах блока 2Б= 2 - 1, Блок 7 по сигналуБ 1, =1 переключается в положение, при5котором на его выход передается выходной сигнал Ь Бд группы 1 О который и записывается в регистр 8, чемобеспечивается отсутствие сбоя ввыходном сигнале устройства: выход Оной сигнал в формате ИКМ равен БЬБД В (11 ВХ 116) БН 9а выходной сигнал в формате МДМЬ Б = Ь Бд зхцп (Ц-11 ) . В дальнейшем работа дельта-модулятора приНУ происходит аналогично, В случае, если в следующем периоде дискретизации Н( 0 н блок 3 формирует сигнал Н=О и работа устройства неотличается от описанной в режиме сле Ожения за входным сигналом,Допустим, что в 3-м периоде дис -кретизации НвО. Это приводит к тому, что на выходе заема блока 3 формируется сигнал 11 = 1, В этом слуРчае запись в регистр 8 выработанногоблоком 2 значения кода также приводит к сбою, Для предотвращения указанного сбоя максимальное значениеЛ Б, которое можно записать в регистр 8 с учетом фиксации знаказКп (У-Н ) минус в триггере 5,равно выходному значению кода в формате ИКМ, сформированного сумматором в АЛБ 3, В этом случае блок 7по сигналу У = 1 переключается вРположение, при котором на его выходах формируется сигнал Ь Б =Б-который и записывается по импульсуна выходе 19 блока 11 в регистры 8и 9, что с учетом знакового разрядана выходе триггера 5 приводит к формированию нулевого значения выходного кода блока 4 в формате ИКМ Б 11- Б+з 18 п (Нрх 06) ЬБ -Б 1 -++(-Б-, ) = О, На выходах 14 и 15при этом формируется выходной сигналустройства в формате МДМ, равный-Б, .В дальнейшем при 06О работадельта-модулятора происходит аналогично. Если в следующие периоды дискретизации НО, то сигнал Нр =Ои устройство возвращается в режимслежения за входным сигналом. Таким образом, выходной сигнал устройства в формате МДМ соответствует дельта-модулятору с центральным подавлением слабых сигналов 5 и равномерным квантованием, при этом врежиме молчания на указанном выходеформируется последовательность шагов квантования входного сигналаСУБД= Я.Сумматор 24 выполняет операция суммирования выходного сигнала дельтамодулятора в формате ИКМ, представленного всегда в прямом п-разрядномкоде, с сигналом приращения входногосигнала с выходов блока 2, представленного в прямом М-разрядном кодесо знаковым разрядом. В группе 23элементов ИСКЛЮЧАЮЩЕЕ ИЛИ сигнал приращения преобразуется в свое (и+1) -разрядное дополнение (если ЬБЕ О)или передается группой 23 без изменекий на первые информационные входысумматора 24, Результат суммирования,возникающий в его (и+1)-м разряде,используется для выработки сигналапереполнения (при Е Д Б0) и сигнала заема (при Е ЬБ(0),Таким образом, в дельта-модуляторе формирование МЯ 4 последовательности позволяет при высоком быстродействии повысить разрешающую способность,а одновременное использование последовательностей МДМ и ИКМ обеспечиваетиспользование дельта-модулятора вустройствах цифровой обработки сигналов в смешанном форматеКроме того, дельта-модулятор обладает повышенной достоверностью преобразования информации и за счет исключения возможных сбоев или автоколебаний при несоотвествии входного сигнала заданному диапазону изменения,Следует отметить, что простое блокирование сумматора в АЛВ 4 в такихслучаях не позволяет достичь достоверного входного сигнала дельта-модулятором, так как в этом случае невозможно сформировать выходной сигнал в формате МДМ, соответствующий заданному диапазону изменения входного сигнала.формула изобретения1. Дельта-модулятор, содержащий цифроаналоговый преобразователь, триггер, выход которого является первым информационным выходом дельта- модулятора, блок мультиплексирования, первый и второй арифметико-логические блоки, первый и второй буферные регистры и блок синхронизации, первыйвыход которого подключен к Входам синхронизации буферных регистров, выходы второго арифметико-логического блока соединены с информационны 5 ми входами второго буферного регистра, о т л и ч а ю щ и й с я тем, что, с целью повышения точности и расширения области применения за счет формирования выходных сигналов О в смешанном формате, в дельта-модулятор введены блок оперативной памяти, группа элементов НЕ и аналого-цифровой преобразователь, первый информационный вход. которого является входом 15 дельта-модулятора, выходы аналого-цифрового преобразователя соединены с информационными входами блока оперативной памяти, первый выход которого подключен .к информационному входу триггера и управляющему входу первого арифметико-логического блока, первый и второй выходы которого соединены с одноименными управляющимивходами блока мультиплексирования, вторые выходы блока оперативной памяти подключены к соответствующим первым информационным входам первого арифметико-логического блока и блока мультиплексирования, выходы ко-, торого соединены с информационными 1 ЗО входами первого буферного регистра, выходы которого подключены к первым информационным входам второго арифметико-логического блока и являются вторыми информационными выходами 35 дельта-модулятора, выходы второго арифметико-логического блока являются третьими информационными выходами дельта-модулятора и подключены к вторым информационным входам первого 40 арифметико-логического блока и блока мультиплексирования, входом цифроаналогового преобразователя и группы элементов НЕ, выходы которых соединены с третьими информационными входами 45 блока мультиплексирования, выходы второго буферного регистра соединены с вторыми информационными входами второго арифметико-логического блока, управляющий вход которого подключен к выходу триггера, первый выход блока синхронизации является первым тактовым выходом дельта-модулятора и подключен к входу синхронизации триггера, выход цифроаналогового преобразователя и второй и третий выходы блока синхронизации соединены со - ответственно с вторым информационньмуправляющим входами аналого-цифрового преобразователя и управляющим входом блока оперативной памяти, четвертый выход блока синхронизации является вторым тактовым выходом дельта-модулятора.2. Дельта-модулятор по п.1 т о тл и ч а ю щ и й с я тем, что первый арифметико-логический блок выполнен на сумматоре, элементе ЗАПРЕТ, элементе И и группе элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, информационные входь. которых являются первыми информационными входами блока, выходы группы элементов ИСКЛЮЧАЮЦЕЕ ИЛИ соединены с первыми информационными входами сумматора, вторые информационные входы которых являются одноименными входами блока, вход перекоса сумматора объединен с управляющим входом группы элементов ИСКЛЮЧАЮЩЕЕ ИЛИ, запрещающим входом элемента ЗАПРЕТ и первым входом элемента И и является управляющим входом блока, выход старшего разряда сумматора подключен к разрешающему входу элемента ЗАПРЕТ и второму входу элемента И, выходы которого являются соответственно первым и вторым выходами блока,3. Дельта-модулятор по п.1, о тл и ч а ю щ и й с я тем, что блок мультиплексирования выполнен на группах элементов И, группе элементов ИЛИ, группе элементов ЗАПРЕТ и элементе ИЛИ, выход которого соединен с запрещающими входами элементов ЗАПРЕТ группы, разрешающие входы ксторых и первые входы элементов И первой и второй групп являются соответственно первыми-третьими информационными входами блока, первый и второй .входы элементов ИЛИ объединены с вторыми входами элементов И соответственно второй и первой групп и являются соответственно первым и вторым управляющими входами блока выходы элементов ЗАПРЕТ группы и элементов И первой и второй групп подключены соответственно к первым- третьим входам одноименных элел 1 ентов ИЛИ группы, выходы которых являются выходами блока.1425838 Составитель О.РевинскийТрхред Л.Сердюкова Корректор С.Чер едактор А.Воров одписное Заказ 4783/5 Тираж 928 ВНИИПИ Государственного ком по делам изобретений и о 13035, Москва, Ж, Раушская

СмотретьЗаявка

4211884, 12.01.1987

ПРЕДПРИЯТИЕ ПЯ В-8751

ТИМЧЕНКО АЛЕКСАНДР ВЛАДИМИРОВИЧ, ТИМЧЕНКО СВЕТЛАНА ВИКТОРОВНА

МПК / Метки

МПК: H03M 3/02

Метки: дельта-модулятор

Опубликовано: 23.09.1988

Код ссылки

<a href="https://patents.su/6-1425838-delta-modulyator.html" target="_blank" rel="follow" title="База патентов СССР">Дельта-модулятор</a>

Предыдущий патент: Способ передачи видеоимпульсов цифровой информации

Следующий патент: Адаптивный дельта-кодер

Случайный патент: Газовая горелка со струйной стабилизацией факела