Устройство для выполнения матричных операций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

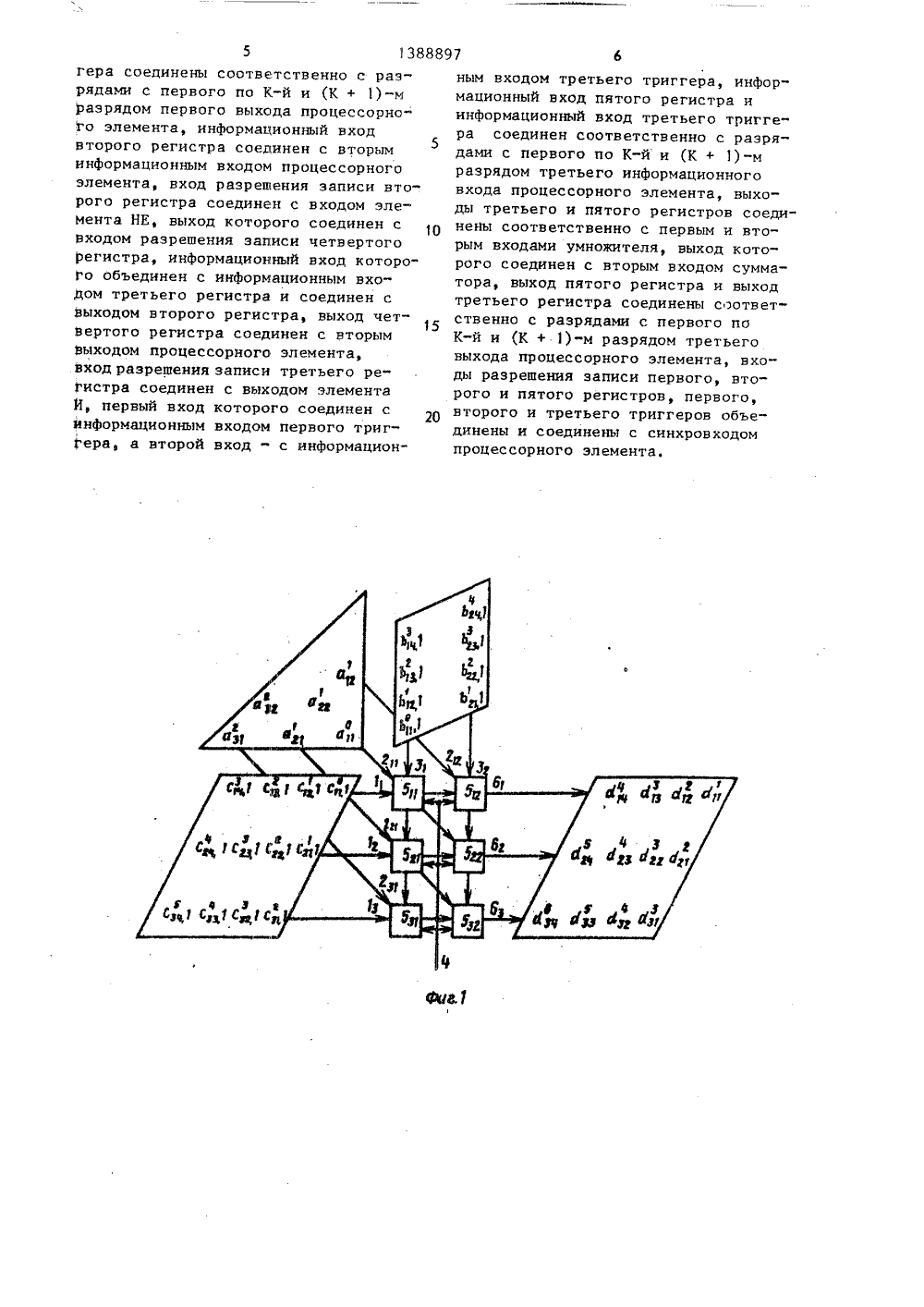

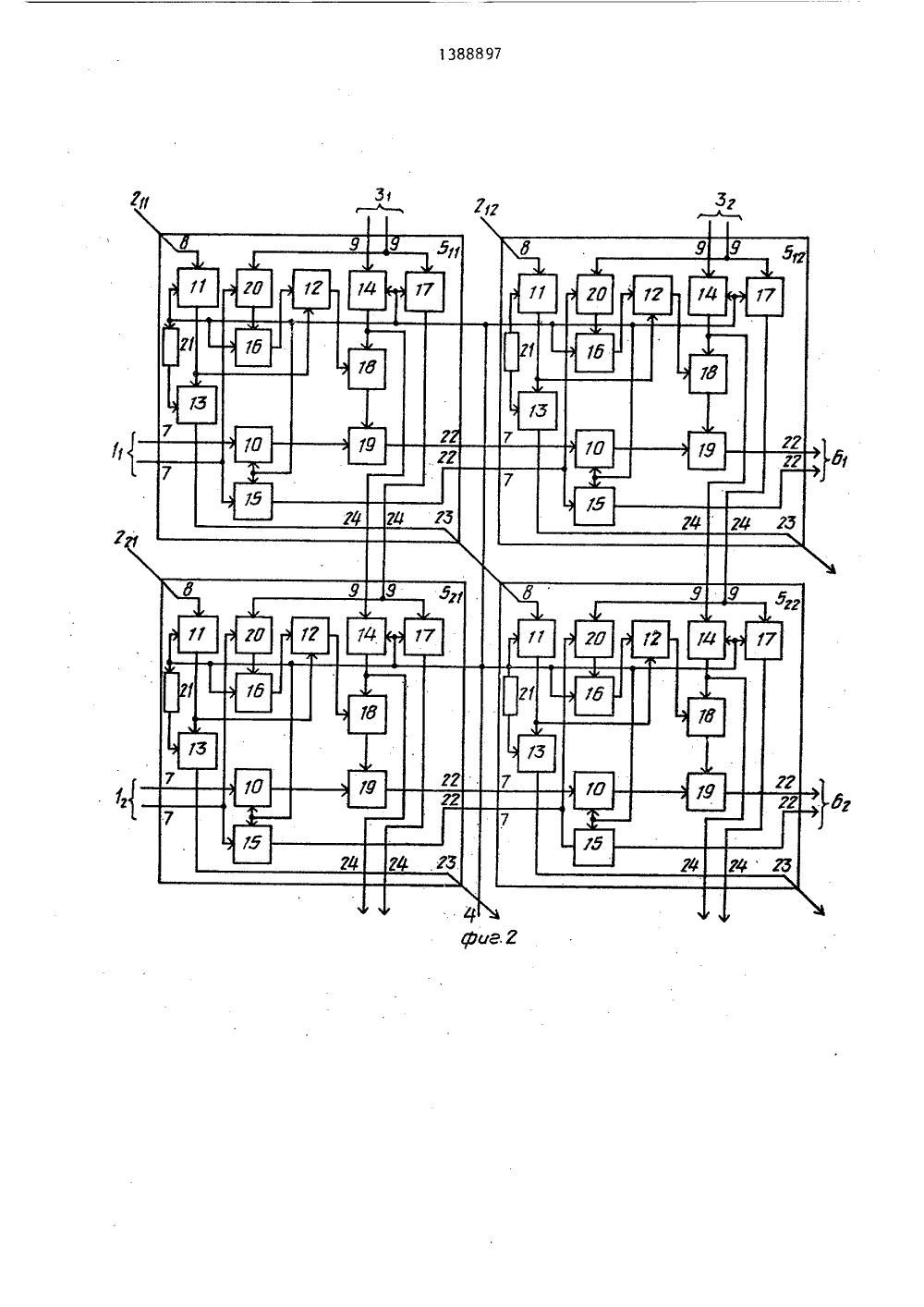

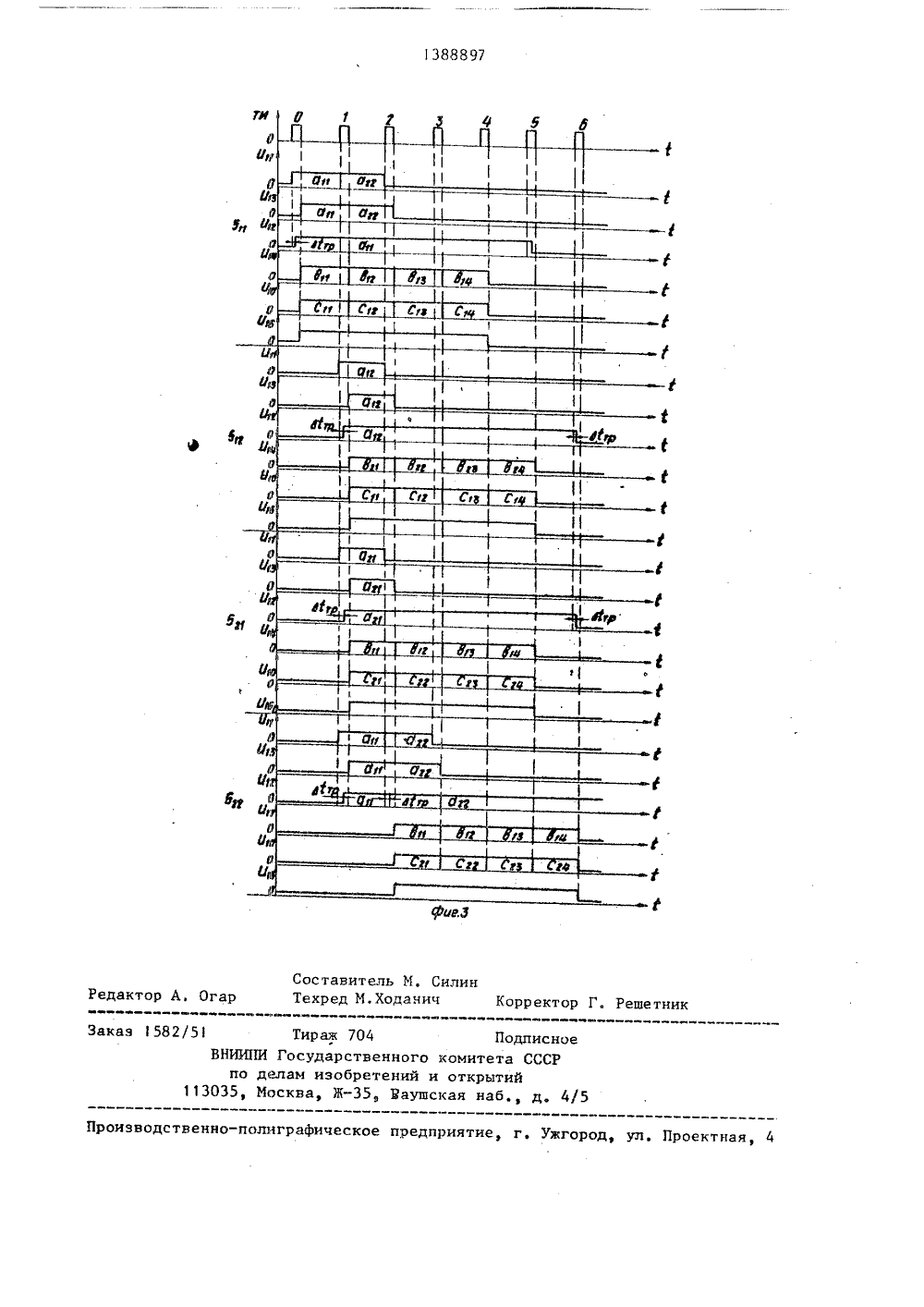

(еЯ 47 151) 4 С 06 БРЕТЕ ЕЛЬСТ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ ОПИСАНИЕ Н АВТОРСКОМУ СВ(56) Авторское свидетельство СССРВ 1236500, кл. С 06 Р 15/347, 1984.Заявка Великобритании 11 2144245,кл. Ь 06 Р 7/52, опублик. 1985.(54) УСТРОЙСТВО ДЛЯ ВЬ 1 ПОЛНЕНИЯ МАТРИЧНЫХ ОПЕРАЦИЙ,вычислительной техники и может бытьиспользовано в специализированных вычислительных машинах и устройствах обработки данных. Цель изобретениярасширение функциональных возможностей устройства за счет выполнения дополнительных операций и повышение быстродействия. Цель достигается тем,что в устройстве, содержащем шр однотипных процессорных элементов, где ши р - размерность матриц А и В соответственно, имеющих три регистра, умножитель и сумматор, в каждый процессорный элемент введены два регистра,три триггера, элемент И и элемент .И-НЕ. Особенностью функционированияустройства являются параллельно-поточная организация вычислений, синхронность исполнения различных частеалгоритма3 ил,13888 97 1 д и,1 1-" ш,о 1 и = сц + а, Ь. Изобретение относится к вычислительной технике и может быть использовано в специализированных вычислительных машинах и устройствах обра 5ботки данных для выполнения над матрицами операции С + АВ.Цель изобретения - расширениефункциональных возможностей устройства за счет выполнения дополнительныхопераций и повышение его быстродействия,На фиг. представлена структурнаясхема устройства для выполнения матричной операции С + АВ с размерностью 5матриц: А-(Зх 2); В-(2 х 4); С-(Зх 4),для ш = 3, п = 4 и р = 2; на фиг,2функциональная схема. соединенных 4процессорных элементов; на Фиг, 3временные диаграммы работы устройства.Устройство для выполнения над матрицами операции С + АВ (Фиг.1) дляш = 3, и = 4 и р = 2 содержит информационные входы 1 1 и 1первойгруппы, информационные входы 2,2 2, и 2 э второй группы, информационные входы 3 и 3 третьейгруппы, вход 4 синхроимпульсов, процессорные элементы 5 ц , 55 ы 30и информационные выходы 6 6 и 6 эгруппы устройства.,Процессорный элемент (фиг.2) содержит первый 7., второй 8 и третий 9информационные входы, регистр 10-14,триггеры 15-17, умножитель 18, сумматор 19, элемент И 20, элемент НЕ 21а также первый 22, второй 23 и третий24 выходы.В основу работы устройства положеналгоритм умножения (шхр) - матрицыА = (а . на (рхп) - матрицу В =Ь;Д,который определяет результирующую матРицУ 0 = 1 Й45с 1; =С; +а;Ь,к: оЕсли й;, = с, то на каждом следующем рекуррентномшаге 1 = 1,р выполняется множество вычислений Особенностями функционирования устройства являются параллельно-по точная организация вычислений, синхронность исполнения различных частей алгоритма, сдвиг накапливаемых сумм на очередном такте работы из 5 -го процессорного элемента в 5;д, -й процессорный элемент (1=1,т; к=1,р) и запись элементов а в соответствующий З-й процессорный элементУстройство работает следующим образом.В исходном состоянии регистры 1 О и триггеры 15-17 устанавливаются в нулевое состояние. Элементы (Ь ,1)Ри (с; , 1) подаются на входы на е-м такте вместе с дополнительным единичным разрядом. Очередность подачи элементов матриц В и С показаны в Форме параллелограммов на фиг.1. Элементы6в; подаются на входы процессорных элементов без дополнительного разряда, очередность подачи элементов матрицы А показана в форме треугольника на фиг.1.оНа нулевом такте элементы а,оц (Ьц , 1) и (сц , 1) подаются на соответствующие входы элементов 5, . По переднему фронту тактового импульсаофиг.З), элемент ац записывается в регистры 11 и 12, так как регистры 11 и 12 реализованы на однотактных триггерах, а триггер 16 в исходном состоянии разрешает запись в регистр 12. По заднему фронту тактового импульса триггер 16 изменяет свое состояние на противоположное и запрещает запись в регистр 12. На выходе элемента НЕ 21 формируется единичный сигнал, который разрешает запись элемен.ота ац в регистр 13, который также реализован на однотактных триггерах. Регистры 10 и 14 реализованы на двухтактных триггерах, следовательно, по заднему фронту тактового импульса в них записываются соответственно элео оменты сц и Ъц . Аналогично двухтактные триггеры 15 и 17 дополнительными единичными разрядами устанавливаются в единичное состояние, С выхода умножителя 18 произведение аЬц подается на вход сумматора 19, на второй вход которого подается с , На выходе сумматора формируется На первом такте на соответствующие входы элемента 5, подаются элементы а , (Ь, 1) и (с, , 1) на соответствующие входы элемента 5 аи(Ьв 1) и (с 1 1), на соответ 1388897ствующие вхо гы элемента 5 - а (Ь, 1) и (с 1).В элементе 5, в регистр 13 записывается элемент а , в регистр 10 -г фэлемент с, в регистр 14 - элемент Ь, на выходе сумматора Формируется й, =с +а Ь,. В элементе 5, в регистр 12чзаписывается элемент а , в регистр 1 О - од, в регистр 14 - Ь на выходео сумматора формируется д = д + а, Ь,. В элементе 5, в регистр 12 записывается элемент а в регистр 10 - злемент с в регистр 14 - Ъ на вы ходе сумматоРа фоРмиРуется Й, = с + + а,Ь.На втором такте в элементе 5в регистр 12 записывается элемент а а триггер 16 изменяет свое состояние и запрещает запись в регистр 12, на выходе сумматора формируется Йд = 1, + а Ь, . В элементах 5; на последующих тактах аналогичным образом формируются с 1;, показанные на временных диаграммах (фиг.3).25Значения соответствующих элементов Й; результирующей матрицы 0 формируются на соответствующих выходах элементов 5; . Количество тактов работы устройства равно (щ+и+р), Длитель 30 ность такта работы устройства определяется выражениемТ =. с ++где 1 - время записи в регистрРУ время умножения; , - время суммиро вания.Для выполнения матричной операции С + АВ над новым потоком данных на соответствующих тактах подаются нулевые дополнительные (К + 1)-е разряды на входы 1 и 3 элементов 5для11 установки в исходное состояние триггеров 16, которые разрешают запись элементов а в регистры 12.45 Для выполнения операции АВ АВ АВ и т,д. в элементах 5," регистры 12 содержат соответствующие элементы а, на входы 1 подаются с =О, а1 Ф на входы 3 - Ь;.50Таким образом, предлагаемое устройство обладает более широкими функциональными возможностями по сравнению с известным, так как в последнем выполняется только перемножение двух 55 патриц, а в предлагаемом устройстве реализуются матричные операции: матричное накопление С + АВ; определяются цепочки матриц АВ АВ, АБ,и т,д.Кроме того, предлагаемое устройство обладает структурой с произвольной размерностью ш, п и р,Ф о р м у л а изобретенияУстройство для выполнения матричных операций, где А - матрица размерности (шхр), В - матрица (рхп), С - матрица (шхп), содержащее шхр однотипных процессорных элементов, содержащих три регистра, умножитель, сумматор, причем первый информационный вход 1.1-го процессорного элемента (=1,ш) соединен с информационным входом первой группы устройства, вторые информационные входы1-го и 1.3-го процессорных элементов Ц=1,р) соединены соответственно с 1.1"м и 1.1-м информационными входа" ми второй группы устройства, третий информационный вход 1.1-го процессорного элемента Я=1,р) соединен с 3-м информационным входом третьей группы устройства, вход синхроимпульсов которого соединен с синхровходами ь,-х процессорных элементов, первый выход .г-го процессорного элемента (г=1, р) соединен с первым информационным входом (х.г 1)-го процессорного элемента, второй выход 1,1-го процессорного элемента соединен с вторым информационным входом (1+1, 3+1) -го процессорного элемента, третий выход Е-го процессорного элемента (1=1, ш) соединен с третьим информационным входом (1+1, 3)-го процессорного элемента, первый выход 1.р-го процессорного элемента подключен к 1-му выходу группы устройства, о т л и ч а ю щ е е с я тем, что, с целью расширения Функциональных возможностей за счет выполнения дополнительных операций и повышения быстродействия, в каждый процессорный элемент введены два регистра, три триггера, элемент И и элемент НЕ, причем информационный вход первого регистра и информационный вход первого триггера соединены соответственно с разрядами с первого по Е-й и (К + 1)-м разрядом первого информационного входа процессорного элемента, где К - разрядность элементов матриц, выход первого регистра соединен с первым входом сумматора, выход сумматора и выход первого триг 1388897гера соединены соответственно с разрядами с первого по К-й и (К + 1)-мразрядом первого выхода процессорно-го элемента, информационный входВторого регистра соединен с вторыминформационным входом процессорногоэлемента, вход разрешения записи вто"рого регистра соединен с входом элеМента НЕ, выход которого соединен сВходом разрешения записи четвертогорегистра, информационный вход которого объединен с информационным входом третьего регистра и соединен сВыходом второго регистра, выход четВертого регистра соединен с вторымВыходом процессорного элемента,Вход разрешения записи третьего регистра соединен с выходом элементаИ, первый вход которого соединен с Оинформационным входом первого тригера, а второй вход - с информационным входом третьего триггера, информационный вход пятого регистра иинформационный вход третьего тригге"ра соединен соответственно с разрядами с первого по К-й и (К + 1)-мразрядом третьего информационноговхода процессорного элемента, выхо"ды третьего и пятого регистров соединены соответственно с первым и вторым входами умножителя, выход которого соединен с вторым входом сумматора, выход пятого регистра и выходтретьего регистра соединены соответственно с разрядами с первого поК-й и (К + 1)-м разрядом третьеговыхода процессорного элемента, входы разрешения записи первого, второго и пятого регистров, первого,второго и третьего триггеров объединены и соединены с синхровходомпроцессорного элемента.1388897 Составитель М, СилинТехред М.Ходанич Корректор Г. Решетник актор А. Ог аказ 1582/5 зводственно-полиграфическое предприятие, г. Ужгор роектная, ТиражВНИИИИ Государпо делаи изо13035) Москва) Ж венного кетений и5, 2 аушск Подписноемитета СССРткрытийя наб д. 4/

СмотретьЗаявка

4134886, 15.10.1986

МИНСКОЕ ВЫСШЕЕ ИНЖЕНЕРНОЕ ЗЕНИТНОЕ РАКЕТНОЕ УЧИЛИЩЕ ПРОТИВОВОЗДУШНОЙ ОБОРОНЫ, ВЫЧИСЛИТЕЛЬНЫЙ ЦЕНТР СО АН СССР

ЯКУШ ВИКТОР ПАВЛОВИЧ, СЕДУХИН СТАНИСЛАВ ГЕОРГИЕВИЧ, МИЩЕНКО ВАЛЕНТИН АЛЕКСАНДРОВИЧ, АВГУЛЬ ЛЕОНИД БОЛЕСЛАВОВИЧ, ПОДРУБНЫЙ ОЛЕГ ВЛАДИМИРОВИЧ

МПК / Метки

МПК: G06F 17/16

Метки: выполнения, матричных, операций

Опубликовано: 15.04.1988

Код ссылки

<a href="https://patents.su/6-1388897-ustrojjstvo-dlya-vypolneniya-matrichnykh-operacijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для выполнения матричных операций</a>

Предыдущий патент: Адаптивный цифровой фильтр

Следующий патент: Анализатор экстремумов функций

Случайный патент: Гидропневматический упругий элемент подвески транспортного средства