Устройство интерполяции для отображения графической информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

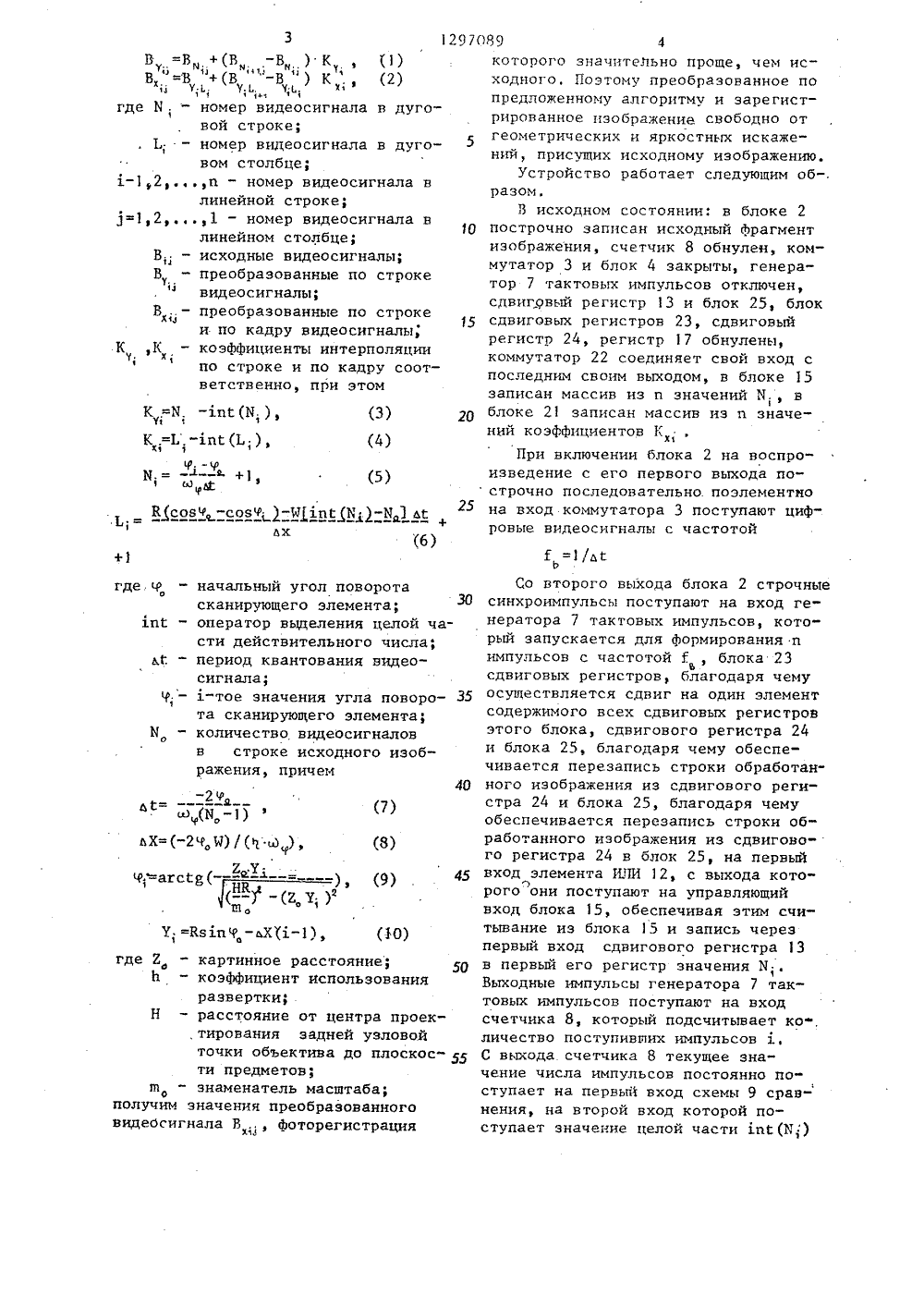

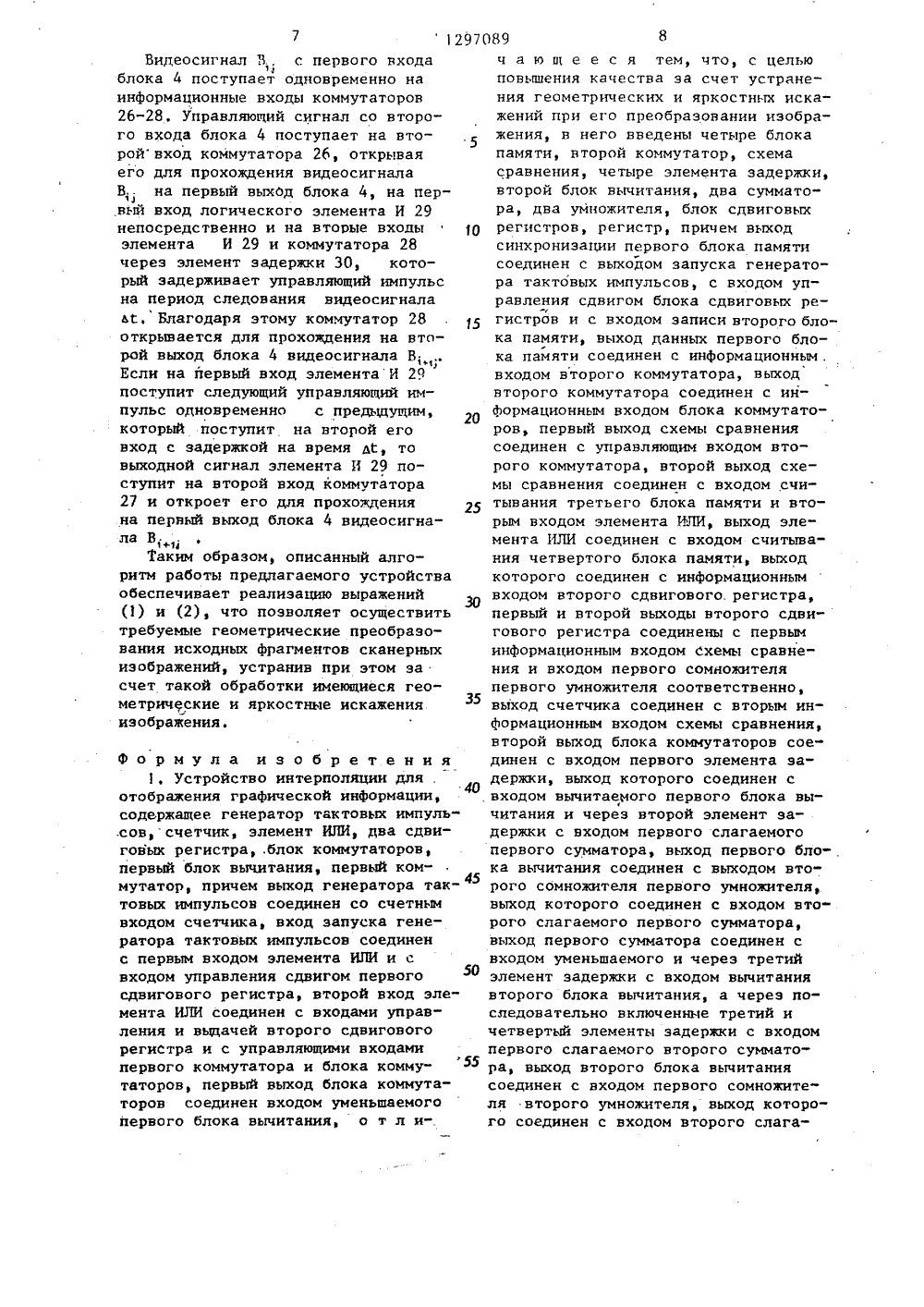

-24 атие дандачи ин 1985,СССР3, 198ДЛЯОРМА к вь ыть исих прео ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ К АВТОРСКОМУ СВИДЕТЕЛЬСТ(57) Изобретение относитсялительной технике и может бпользовано для геометрическ раэований цифровых изображений, получаемых с помощью оптико-электронных приборов с конической разверткойпространства предметов. Целью изобретения является повьппение качестваизображения. Устройство содержит четыре блока 2, 15, 21, 25 памяти, четыре элемента 1, 6, 14, 19 задержки,два коммутатора 3 и 22, блок 4 коммутаторов, два блока 5, 16 вычитания, генератор 7 тактовых импульсов,счетчик 8, схему 9 сравнения, дваумножителя 10 и 18, два сумматора11 и 20, элемент ИЛИ 12, два сдвиговых регистра 13 и 24, регистр 17,блок 23 сдвиговых регистров. 1 з,п.ф-лы, 2 ил,7089 2фазовый генератор сдвиговых импульсов, запускаемый управляющим импульсом), Пни этом количество регистрови их расположение в блоке 23 определяется в соответствии с выражениемщ,=ап 1 (1. . ), где 1 равно 1, 2,п -порядковый номер сдвигового регистра, Счетчик 8 расчитан на иим"пульсов. Сдвигоный регистр 24 сос- Ю тоит иэ генератора сдвиговых импульсов, запускаемого управляющимимпульсом, поступающим на управляемый вход регистра 24 и собственногосдвигового и - элементного регистра.15 Элемент задержки 14 имеет длительность задержки, равную периоду следования синхроимпульсов, т,е. периоду сканирования-2 Ч Т = - - . ек)ф 20 1 129Устройство интерполяции для отображения графической информации.Изобретение относится к вычислительной технике и может быть применено для геометрических преобразований цифрового изображения, получаемого с помощью оптико-электронныхприборов с конической разверткойпространства предметов.Цель изобретения - поныщение качества изображения за счет устранения геометрических и яркостных искажений при его преобразованииНа фиг. 1 приведена функциональная схема устройства; на фиг. 2 -пример конкретной реализации блокакоммутаторов.Устройство содержит (фиг. 1) первый элемент задержки 1 первый блок2 памяти, второй коммутатор З,блок4 коммутаторов, первый блок 5 вычитания, второй элемент задержки 6,генератор 7 тактовых импульсов,счетчик 8, схему 9 сравнения, первый умножитель 10, первый сумматор11, элемент ИЛИ 12, второй сдниговый регистр 13, третий элемент задержки 14, четвертый блок 15 памяти, второй блок 16 вычитания, регистр 17, второй умножитель 18, четвертый элемент задержки 19 сумматор20, третий блок памяти 21, первыйкоммутатор 22, блок 23 сдвиговихрегистров, первый сдвиговый регистр.Сдвйговый регистр 13 содержитдва связанных последовательных регистра, При этом первый выход сдвигового регистра 13 соединен с разрядами целой части числа, записанного в первый регистр. Второй выходсдвигового регистра 13 связан с раз"рядами дробной части числа, записанного во второй регистр. Блоки 15 и21 выполнены циклическими, что обеспечивает многократное, последовательное считывание записанных в них предварительно значений М; и К,. Для предварительной записи указанных массивов блоки 15 и 21 имеют специальныйвход (на фиг, 1 не показан). Блок 23сдвиговых регистров состоит из исдвиговых,щ, - элементных регистрови может быть выполнен, например, наприборах с, зарядовой связью (ПЗС)(в этом случае блок содержит многоЭлемент задержки 30 имеет длительность задержки, равную периодуследования видеосигналов ай, При ко 25 нической развертке пространства предметов траектория визерного луча вплоскости предметов представляет собой дугу окружности с радиусом К,При этом развертка по строке осуще 3 п стнляется с помощью сканирующего элемента с угловой скоростью вращенияау, а развертка по кадру - за счетпоступательного перемещения оптикоэлектронного прибора со скоростью У.Фоторегистрация полученных видеосигналов должна производиться синхроннои синфазно процессу формированияисходного иэображения. Однако этасинхронность и синфазность не всег 4 О да может быть обеспечена ввиду рядатехнических причин (погрешность изготовления и юстировки оптическихдеталей и т.д,), что приводит к заметным геометрическим и яркостным45 искажениям получаемых изображений.Поэтому предлагается для повьпнениякачества сканерных изображений осуществлять их геометрические преобразования к ортогональной проекции,5 О т.е, нидеосигнал, соответствующийдуговому растру, трансформироватьв видеосигнал, соответствующий линейно-строчному растру, образующему.сетку с квадратными ячейками днах55 путем интерполяционного восстановления значений видеосигнала в узлахсетки. Используя формулы линейнойинтерполяции по строке (по оси У)и по кадру по осн.Х), т,е, 1297089(6) начальный угол поворотасканирующего элемента;оператор выделения целой части действительного числа;период квантования видеосигнала;-тое значения угла поворота сканирующего элемента;количество видеосигналовв строке исходного изображения, причем где: Ц3.пг 30 35 10 45 50 55), (9) где Е - картинное расстояние;Ь " коэффициент использованияразвертки;Н - расстояние от центра проек,тирования задней узловойточки объектива до плоскости предметов;в " знаменатель масштаба; получим значения преобразованного видеосигнала В , фоторегистрация В =В, +(В, -В ) К , (1) где И . - номер видеосигнала в дуговой строке;Ь - номер видеосигнала в дуговом столбце;-1,2п - номер видеосигнала влинейной строке;1=1,2 .1 - номер видеосигнала влинейном столбце;В - исходные видеосигналы;В - преобразованные по строкет,видеосигналы;В- преобразованные по строкехци по кадру видеосигналы, К ,К - коэффициенты интерполяциипо строке и по кадру соответственно, при этом К;-И, -Ыг. (И, )К,=1 -1 пС (1; ),Ю -РН=-+1 (5)1 Ь 3Щсозм -сов, -И 1 пг Ь 1-01 ь 1 2 Риэ, (М - 1)ьХ=(-2 Ч,У) /( ы ), ч;=агсг,8 (Е У У =Язв.п 9 -ьХ(з.-1), (ХО) 5 10 15 20 25 которого значитеЛьно проще, чем исходного. Поэтому преобразованное по предложенному алгоритму и зарегистрированное пзображение свободно от геометрических и яркостннх искажений, присущих исходному изображению.Устройство работает следующим об-. разом.В исходном состоянии: в блоке 2 построчно записан исходный фрагмент иэображения, счетчик 8 обнулен, коммутатор 3 и блок 4 закрыты, генератор 7 тактовых импульсов отключен, сдвиговый регистр 13 и блок 25, блок сдвиговых регистров 23, сдвиговый регистр 24, регистр 17 обнулены, коммутатор 22 соединяет свой вход с последним своим выходом, в блоке 15 записан массив из и значений М в1 блоке 21 записан массив из и значений коэффициентов КПри включении блока 2 на воспроизведение с его первого выхода построчно последовательно.поэлементно на вход коммутатора 3 поступают цифровые видеосигналы с частотойГ =1/ььСо второго выхода блока 2 строчные синхроимпульсы поступают на вход генератора 7 тактовых импульсов, который запускается для формирования и импульсов с частотой Г , блока 23 сдвиговых регистров, благодаря чему осуществляется сдвиг на один элемент содержимого всех сдвиговых регистров этого блока, сдвигового регистра 24 и блока 25, благодаря чему обеспечивается перезапись строки обработан" ного изображения из сдвигового регистра 24 и блока 25, благодаря чему обеспечивается перезапись строки обработанного изображения из сдвигово-го регистра 24 в блок 25, на первый вход элемента ИЛИ 12, с выхода кото"орого они поступают на управляющий вход блока 15, обеспечивая этим считывание из блока 15 и запись через первый вход сдвигового регистра 13 в первыи его регистр значения М;. Выходные импульсы генератора 7 тактовых импульсов поступают на вход счетчика 8, который подсчитывает ко личество поступивщих импульсов .С выхода. счетчика 8 текущее значение числа импульсов постоянно поступает на первый вход схемы 9 сравнения, на второй вход которой поступает значение целой части 1 пг;(И )5 129числа, записанного в первый регистрсдвигового регистра 13, с первоговыхода этого регистра. При равенстве значений на обоих входах схемы 9 сравнения на первом и второмвыходах последней формируются управляющие импульсы различной длительности. При этом на первом вь 1 ходе Формируется управляющий импульс, равный по длительности 2/Гт.е. равный периоду следования двух .видеосигналов, На втором выходеформируется импульс половинной длительности, т.е. равный длительности периода следования одного видеосигнала, С первого выхода схемысравнения 9 импульс поступает науправляющий вход коммутатора 3 иоткрывает его на время длительностиуправляющего импульса, т.е, навремя периода следования двух видеосигналов (-того и (.+1)-го, С выхода открытого ключа 3 видеосигналыВ и В. . последовательно поступа+цют на первый вход блока 4. Со второго выхода схемы сравнения 9 импульспоступает на вторые входы блока 4 иэлемента ИЛИ 12 и на управляющие входы сдвигового регистра 13, блока21 обеспечивает считывание и записьочередного х-го значения коэффициента К . в регистр 17. ПоступлениеХ 1первого управляющего импульса обеспечивает переключение коммутатора22 для прохождения входного видеосигнала на первый выход последнего.Очередные х"ые управляющие импульсыпереключают коммутатор 22 для прохождения входного видеосигнала коммутатора 22 В на соответствующийх ,его .-ый выход. Управляющий импульстакже обеспечивает сдвиг на одинэлемент содержимого сдвнгового регистра 13, т.е. перезапись числа И,с его первого во второй его регистр,С выхода элемента ИЛИ 12 импульс поступает на управляющий вход блока15, благодаря чему очередное значение - число Б. считывается из бло+1ка 15 и записывается в первый регистрсдвигового регистра 13, Поступлениеуправляющего импульса на второййход блока 4, а второго видеосигнала В - на второй выход блока 4. Сй. - ,первоговыхода блока 4 Ю-ый видеосигнал через элемент задержки 1,задерживающий на период следованиявидеосигналов ьй, поступает черезэлемент задержки 6, в котором эадер 9 6живается на время обработки випеосигналов в блоках 5 и 10, на первыйвход сумматора 1 О, и на первый входблока 5 вичитЯния одновременно споступлением на его второй вход(Ы )-го видеосигнала. Выходной сигнал (Р -В; ) блока 5 вычитания1 Мпоступает на первый вход умножителя10, на второй вход которого поступаО ет дробная часть числа Ю;, т.е. коэффициент К., со второго выхода сдвигового регистра 13,Выходной сигнал (В -В )КМ, ч, " Чумножителя 10 поступает на второи5 вход сумматора 11, где суммируетсяс соответствующим значением В . С14выхода сумматора 11 частично обработанный видеосигнал В , поступает1непосредственно на первый вход бло"2 ц ка 16 вычитания и через элементзадержки 14, в котором задерживаетсяна время периода следования строчныхсинхроимпульсов Т т,е, на периодследования строк изображения, на25 второй вход блока 16 выхода вычитания, в котором вычисляется значением (Г, . -В , ),и через элемент за - ФЧЬдержки 11, где задерживается на время обработки видеосигналов в блоках30 6 и 18, на второй вход сумматора 20,С выхода блока 6 вычитания видеосигнал (В -В), поступает на перувый вход умножителя8 , на второй ,вход которого с выхода регистра 1 735поступает -ое значение коэйфициента К Выходной сигнал (В -В )"мь; 1 д;дК умножителя 18 поступаетна втоХ;рой.вход сумматора 20, где суммируется с соответствующим значением40 В . С выхода сумматора 20 обрабоС 1танный видеосигнал В, поступает навход коммутатора 22. С соответствующего выхода коммутатора 22 (в зависимости от положения этого коммута 45 тора т.е, от значения ) видеосигнал В,. поступает на соответствуюх;щий х.-нй вход блока сдвиговых регистров 23, в котором, продвигаясь сразличной задержкой (в зависимостиот номера регистра 1), следовательно, в зависимости от значениявидеосигналы В . достигают соответствующего х-го элемента выходного сдвигового регистра 24 и записываются в55нем. В последующих тактах и строкахобработка исходных видеосигналовпроизводится аналогично.Блок 4 работает следующим образом,712970Видеосигнал 3., с первого входа1блока 4 поступает одновременно на информационные входы коммутаторов 26-28. Управляющий сигнал со второго входа блока 4 поступает на вто 5 рой вход коммутатора 26, открывая его для прохождения видеосигнала В на первый выход блока 4, на первий вход логического элемента И 29 непосредственно и на вторые входы 1 О элемента И 29 и коммутатора 28 через элемент задержки ЗО, который задерживает управляющий импульс на период следования видеосигнала ь, Благодаря этому коммутатор 28 открывается для прохождения на второй выход блока 4 видеосигнала В; Если на первый вход элементаИ 29 поступит следующий управляющий импульс одновременно с предыдущим, который поступит на второй его вход с задержкой на время ь, то выходной сигнал элемента И 29 поступит на второй вход коммутатора 27 и откроет его для прохождения 25 на первый выход блока 4 видеосигна- лаВ;.Таким образом, описанный алгоритм работы предлагаемого устройства обеспечивает реализацию выраженийи (2), что позволяет осуществить требуемые геометрические преобразования исходных фрагментов сканерных иэображений, устранив при этом за счет такой обработки имеющиеся геометрические и яркостные искажения изображения. 35 Формула изобретенияУстройство интерполяции для . отображения графической информации, содержащее генератор тактовых импуль.сов, счетчик, элемент ИЛИ, два сдвиговых регистра, .блок коммутаторов, первый блок вычитания, первый коммутатор, причем выход генератора так"45 товых импульсов соединен со счетным входом счетчика, вход запуска генератора тактовых импульсов соединен с первым входом элемента ИЛИ и с входом управления сдвигом первого сдвигового регистра, второй вход эле" мента ИЛИ соединен с входами управления и выдачей второго сдвигового регистра и с управляющими входами первого коммутатора и блока коммутаторов, первый выход блока коммутаторов соединен входом уменьшаемого первого блока вычитания, о т л и-. ч а ю щ е е с я тем, что, с целью повышения качества за счет устранения геометрических и яркостнкх искажений при его преобразовании изображения, в него введены четыре блока памяти, второй коммутатор, схема сравнения, четыре элемента задержки, второй блок вычитания, два сумматора, два умножителя, блок сдвиговых регистров, регистр, причем выход синхронизации первого блока памяти соединен с выходом запуска генератора тактовых импульсов, с входом управления сдвигом блока сдвиговых реюгистров и с входом записи второго блока памяти, выход данных первого блогка памяти соединен с информационным . входом второго коммутатора, выход второго коммутатора соединен с информационным входом блока коммутаторов, первый выход схемы сравнения соединен с управляющим входом второго коммутатора, второй выход схемы сравнения соединен с входом считывания третьего блока памяти и вторым входом элемента ИЛИ, выход элемента ИЛИ соединен с входом считывания четвертого блока памяти, выход которого соединен с информационным входом второго сдвигового. регистра, первый и второй выходы второго сдвигового регистра соединены с первым информационным входом схемы сравнения и входом первого сомножителя первого умножителя соответственно, выход счетчика соединен с вторым информационным входом схемы сравнения, второй выход блока коммутаторов соединен с входом первого элемента задержки, выход которого соединен с входом вычитаемого первого блока вычитания и через второй элемент задержки с входом первого слагаемого первого сумматора, выход первого бло-, ка вычитания соединен с выходом второго сомножителя первого умножителя, выход которого соединен с входом второго слагаемого первого сумматора, выход первого сумматора соединен с входом уменьшаемого и через третий элемент задержки с входом вычитания второго блока вычитания, а через последовательно включенные третий и четвертый элементы задержки с входом первого слагаемого второго сумматора, выход второго блока вычитания соединен с входом первого сомножителя второго умножителя, выход которого соединен с входом второго слагаСоставитель В,БородинРедактор Н,Горват Техред Л.Сердюкова ктор А,Зимокосов 4/54 Тираж 673 ВНИИПИ Государственно по делам изобретени 113035, Москва, Ж, РаПодписное митета СССР ткрытий я наб.,к го й и упс д. 4/5 Производственно-полиграфическое предприятие, г. Ужгород,Проектная 9 2970 емого второго сумматора, выход второго сумматора соединен с информационным входом первого коммутатора, выходы первого коммутатора соединены с информационными входами блока сдвиговых регистров, выходы которого соединены с информационными входами первого сдвигового регистра, выход которого соединен с информационным входом второго блока памяти, выход 10 третьего блока памяти соединен с информационным входом регистра, выход которого соединен с входом второго сомножителя второго умножителя. 152. Устройство по п, 1, о т л ич а ю щ е е с я тем, что блок коммутаторов содержит три коммутатора,элементИ и элемент задержки, причем информационный вход блока соединен с информационными входами с первого по третий коммутаторов, управляющий вход блока соединен с управляющим входом первого коммутатора, с,первым входом элемента И и черезэлемент задержки с вторым входомэлемента И и с управляющим входомтретьего коммутатора, выход элемента И соединен с управляющим входомвторого коммутатора, выход третьего коммутатора является первым выходом блока, выходы первогои второго коммутаторов соединены с вторымвыходом блока

СмотретьЗаявка

3930386, 16.07.1985

ВОЕННЫЙ ИНЖЕНЕРНЫЙ КРАСНОЗНАМЕННЫЙ ИНСТИТУТ ИМ. А. Ф. МОЖАЙСКОГО

БАТРАКОВ АНАТОЛИЙ СЕМЕНОВИЧ, ГАВЕНКО ВИКТОР ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06T 3/00

Метки: графической, интерполяции, информации, отображения

Опубликовано: 15.03.1987

Код ссылки

<a href="https://patents.su/6-1297089-ustrojjstvo-interpolyacii-dlya-otobrazheniya-graficheskojj-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство интерполяции для отображения графической информации</a>

Предыдущий патент: Устройство для магнитной записи-воспроизведения данных амбулаторной карты

Следующий патент: Устройство для контроля работы машин

Случайный патент: Преобразователь "угол-код"