Устройство для исправления ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1287296

Автор: Устинов

Текст

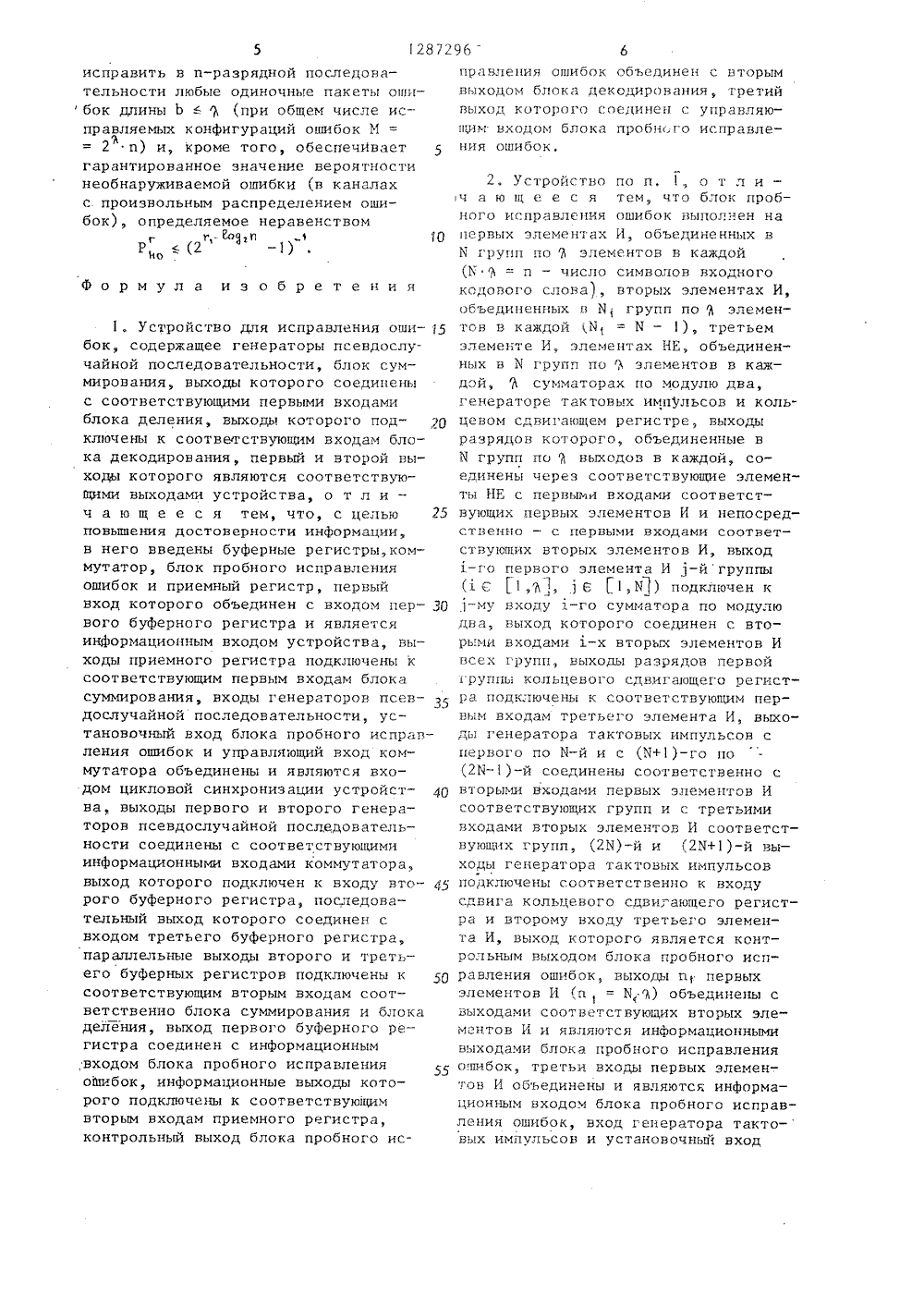

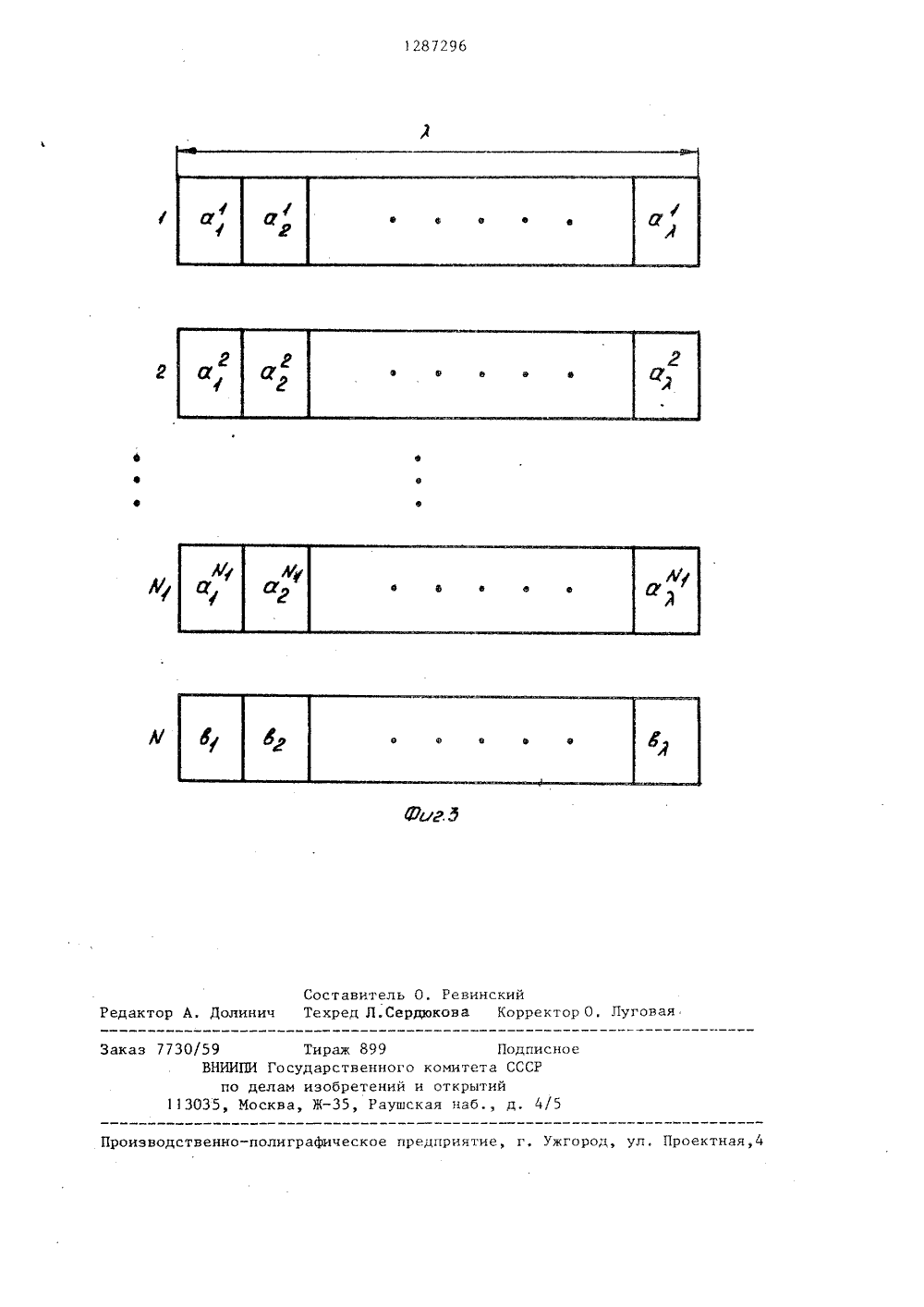

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК 9 8 0 ( 3 М 13/02 НОМИТЕТ СССР ЕНИЙ И ОТНРЫТ ГОСУДАРСТВЕННЫ ПО ДЕЛАМ ИЗОБ ржит бл деления генератор довател бл8 ьнос 1, б тора гисткомму Те и, С 7, в справления ять в и-ра ельности л ехоусх сообвероятностью Р ок длинои трукг вязи, 195 о и =К+формацион г Киг - коных и проверочго (и К)-кода; при общем числе 1, 11, 9чество лов исходн елые числа ных симв11;, фисправляЯ2 и и иисрации ошибок обеспечивае мых кон иг роме тог оваой аран еобн ирован ружива ольным (2 ф ос е до -роизго аспределением о 1) . 1 з.п. ф-л ации.бок соок3 НИЕ ИЗОБРЕТЕНИ ВТОРСНОМУ СВИДЕТЕЛЬСТВУ(53) 621.391.15(088.8)Техника средств связпроводной связи, 197с, 81-85.Коржик В.И., Финк Л.М. Помтойчивое кодирование дискретнщений в каналах со случайнойтурой (Статистическая теориявып. 4), М.: "Связь", 1975, с196, рис. 4.1.(54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯБОК(57) Изобретение относится клительной технике, Его испольние в системах передачи цифроформации обеспечивает повышенстоверности принимаемой инфорУстройство для исправления оши 2 суммирования, блок к 4 декодирования и г 9 псевдослучайной.пос и. Введение приемного ферных регистров 5-7, О и блока 11 пробног ошибок позволяет испр яднои кодовои последоваые одиночные пакеты ошиое значение вероятмой ошибки (в каналков складывают па модулю два, в результате чего получают проверочный отрезок длинь 1двоичных символов (фиг. 3)1 которые дааавляют к г,1 два - ичным символам, Б результате общая длина передаваемой кодовой последовательности делается равной и = Б(11 + 1) 11 двоичных символов, а аб - щее число проверочных символов равным г =г +,Устройство для ис.правления ошибок работает следуюшим образом.Принятая и в разрядн кодовая после - давательность са Входа 12 записывается в первый буферный регистр 5, а и= К + г, ее символов, подвергну - тых на передающем канде псевцастахастическаму преобразованию, заносятся в приемный регис.тр. Одновременна па сигналу циклавай синхронизации со Входа 13 генераторы 8 и 9 формчруют очередные значения двух отрезков псевдослучайных последовательностей длины и, = К + г, двоичных символов каждый, которые через коммутатор 10 заносятся и запоминаются в регистрах 6 и 7, По тому же сигналу са входа 3 в блоке 11 пробного исправления ошибок гервые 1 элементов кольцевого сдвигающего регистра ,6 ус 11 1 с т ан авли в ают ся в и ал Ож енч е 1 , а о ст ал ьные - в и олаж ени е 011Кодовая последовательность, пасту - пающая на вход 12 устройства, Формируется следующим образом. К К двоичныминформационным символам падлежа - 50 шим передаче, добавляют г, двоичных проверочных символов, полученных в соответствии с чспользуемым (и 1,К)- кодом, при этом выполняется равенство и= Ы 1 %, где Ы, и % - целые числа, Над полученной последовательностью длины и двоичных символов производятооперацию псевдастахастическага преобразования, заключающуюся в умнаже:1 ии Изобретение относится к вычислительной технике и может быть ис.попьзоиана в системах передачи цифровойинформации.Целью изобретения является повышение достоверности принимаемой информации.На фиг, 1 приведена блок-схема устройства для исправления ошибок; нафиг. 2 - функциональная схема блока1 Опробного исправления ошибок; нафиг. 3 - структура кодовой последовавтельности, поступающей на вход устройства.Устройство для исправления ошибоксодержит приемный регистр 1, блок 2суммирования, блок 3 деления, блок чдекодирования, первый, второй и третий буферные регистры 5-7, первый ивторой генераторы 8, 9 псевдослучайной последоватеЛьности, коммутатор 10 и блок 11 пробного исправления ошибок, На Фиг. 1 также обозначены информационный вход 12, вход 13цикловой синхронизации, первый и второй выходы 14 и 15,Блок 2 суммирования осуществляетпоразрядное сложение па модулю два,Блок 4 декодирования осуществляетдекодирование с обнаружением ошибокв соответствии с исходным кодом, надкоторым осуществляется операция псевдостохастическога преобразования.Коммутатор 10 служит для поочередного падключения генераторов 8 и 9 кбуФерному регистру О.Блок 11 исправления ошибок (Фиг,2)включает в себя кольцевой сдвигающийрегистр 16, генератор 7 тактовых им -пульсов элементы 18 НЕ, первые,вторые и третий элементы 19, 20, 21 И,сумматоры 22 по модулю два.Генератор 17 тактовых импульсоввыполнен на генераторе импульсов ираспределителе импульсов па модулю непривоиимо 1 О палинома степени и, на п - разрядную псевдослучай -ную последовательность и сложения памодулю два результата ) 11 нажения с дру -1 ОЙ и - раз ряДнай псевдаслз 1 чайной па -следавательнастью, Пасле 11 ь:".7 Рл 1 нОсть,. полученную после псевдастахастическа -го преобразования длины и, = М 1разделяют на Мотрезков длиныкаждый и производят кодирование второй ступени, в соответствии с которымодноименные символы полученных отрезПо завершению приема и-разрядной кодовой последовательности с приемного регистра 1 считываезся преобразованный на передаче отрезок кодо - вай последовательности дли:ы иК + г, в блок 2 суммирования, где производится ега сложение па модулю два с первым и,-разрядным отрезкомпсевдослучайной последовательности,аодщс в регистре 6, а осеэтога - давление па модулю неприва -димага палинома степени и, результата суммирования в блоке Э на значение 17-разрядн 1 О.рез;а псевдаслу 1287296чайной последовательности, хранящимся в регистре 7. Результат деленияв виде отрезка длины Кг, двоичныхсимволов поступает в блок 4 декодирования, где в соответствии с введенными при кодировании г, проверочными символами производится проверкаэтбго отрезка на наличие ошибок.При необнаружении ошибок К-разрядное сообщение поступает на первый Овыход К устройства,При обнаружении ошибок блок 4 декодирования по своему третьему выхо -ду вырабатывает сигнал, который поступает в блок 11 на генератор 17тактовых импульсов, который в своюочередь формирует серию тактовых импульсов, осуществляющих управлениеработой блока 11,Первая серия из М импульсов осуществляет считывание и-разрядной коДовой последовательности, хранящейся в первом буферном регистре 5, через элементы 19 - 19 И в сумматоры 22 25М9по модулю два, где осуществляется суммирование одноименных символов Ы отрезков длиныдвоичных символов каждый (сложение по столбцам), и в приемный регистр 1 с первых выходов ЗО блока 11 пробного исправления ошибок записываются и двоичных символов, При этом считывание через элемент 9 И разрешается с помощью элементов 18 НЕ для тех разрядов кодовой последовательности, которые соответствуют элементам кольцевого сдвигающего регистра 16, находящимся в положении "О" (в начале работы этому положению сов ответствуют все элементы кольцевого сдвигающего регистра 16, кроме перЮ рвых 3 элементов, которые были ранее установлены в положение ) . В результате в приемном регистре 1 будет записана и-разрядная последователь ность,первых символов которой стерты, а в сумматорах 22 по модулю два - результат суммирования одноименных нестертых символов, который записывается в приемный регистр 1 на место стертых символов через злементы 20 И с помощью второй серии из И импульсов (1+12 М) генератора 17 тактовых импульсов. Следующим импульсом с генератора 17 осуществля ется сдвиг содержимого кольцевого сдвигающего регистра 16 на один разряд вправо, а последним импульсом осуществляют с помощью третьего элемента 21 И проверку наличия всех первыхэлементов кольцевого сдвигаю - щего регистра 16 в положении ,что является признаком окончания процесса декодирования.Полученная в результате пробного стираниядвоичных символов и последующего ее восстановления и,-разрядная двоичная последовательность снова подвергается обратному псевдостохастическому преобразованию в блоках 2 и 3, а оттуда поступает в блок 4 декодирования. При необнаружении ошибок К в разрядн сообщение поступает получателю, а при обнаружении ошибки вновь вырабатывается сигнал по тре. - тьему выходу блока 11 обнаружения ошибок на запуск генератора 7 тактовых импульсов, в соответствии с которым осуществляется стирание с последующим восстановлением уже другой комбинации двоичных символов,определяемой элементами кольцевого сдвигающего регистра 16, находящимися в положении1", и повторение цикла декодирования,В случае обнаружения ошибок во всех предусмотренных 1 циклах декодирования блок 11 пробного нсправле - ния ошибок вырабатывает сигнал по второму выходу (именно в этот момент первыеэлементов кольцевого сдвигающего регистра 16 будут находиться в состоянии 1"), который является вторым выходом 1.5 устройства, о наличии неисправляемой комбинации ошибок.Значение 1 - максимально необходимое число циклов декодирования призаданных значениях и, г, - определяется минимальным числом комбинацийстираемых символов, включающих в себя остальные комбинации стираний,которые могут быть исправлены используемым кодом при условии отсутствия ошибок в остальных символахкодовой последовательности,Очевидно, что значение 1, которое может быть реализовано, удовлетворяет неравенство 11 , В рассматрн%ваемом варианте устройства для ис - правления ошибок 1 = и +1 число ис - правляемых сочетаний стираний М =2 и.ЪТаким образом, устройство для исправления ошибок за счет введения в передаваемую информацию г = г, + Я проверочных символов позволяет с вег,- Ь,и роятностью Р, = 1 - и (2 -)исправить в п-разрядной последова - тельности любые одиночные пакеты о 1 г-бок длины Ь(при общем числе исправляемых конфигураций ошибок М =2 п) и, кроме того, обеспечиваетгарантированное значение вероятностк необнаруживаемой ошибки (в каналах с произвольным распределением ошибок), определяемое неравенствомг "- д 3 г в 10РноФормула изобретения1. Устройство для исправления оши бок, содержащее генераторы псевдослучайной последовательности, блок суммирования выходы которого соединены с соответствующими первыми входами блока деления, выходы которого под п ключены к соответствующим входам блока декодирования, первый к второй выходы которого являются соответствуюЩими выходами устройства, о т л и - ч а ю щ е е с я тем, что, с целью 25 повьппения достоверности информации, в него введены буферные регистры,коммутатор, блок пробного исправления ошибок и приемный регистр, первый вход которого объединен с входом пер- ЗО вого буферного регистра и является инФормационным входом устройства, выходы приемного регистра подключены к соответствующим первым входам блока. суммирования, входы генераторов псевдослучайной последовательности, установочный вход блока пробного исправления ошибок и управляющий вход коммутатора объединены и являются входом цикловой синхронизации устройства, выходы первого и второго генераторов псевдослучайной последовательности соединены с соответствующими информационными входами коммутатора, выход которого подключен к входу втс-,5 рого буферного регистра, последовательный выход которого соединен с входом третьего буферного регистра, параллельные выходы второго и третьего буферных регистров подключены к соответствующим вторым входам соответственно блока суммирования и блока деления, выход первого буферного регистра соединен с информационным ,входом блока пробного исправления ошибок, информационные выходы которого подключены к соответствующим вторым входам приемного регистра, контрольный выход блока пробного ксправления ошибок объединен с вторым выходом блока декодирования, третий выход которого соедкнен с управляю - щкм входом блока пробного исправления ошибок. 2, Устройство по п. 1 о т л и ч а ю щ е е с я тем, что блок пробного ксправленкя ошибок выполнен на гервых элементах И, объединенных в К групп по Я элементов в каждой (Е=п -кодового слова, вторых элементах И, объединенных в Б; групп по Я элементов в каждой Л = 11 - 1), третьем элементе И, элементах НЕ, объединенных в И групп по 5 элементов в каждой, 5 сумматорах по модулю два, генераторе тактовьх импльсов и кольцевом сдвкгающем регистре, выходы разрядов которого, объединенные в Ь 1 групп по 9, выходов в каждой, соединены через соответствующие элементы НЕ с первьпчк входами соответствующих первых элементов И и непосредственно - с первыми входами соответствующих вторых элементов И, выход г-го первого элемента И -йгруппь (1 С 11,3 " 1 Е 1,111) подключен к 1-му входу 1-го сумматора по модулю цва, выход которого соединен с вторь:мк входами 1-х вторых элементов И всех групп, выходы разрядов первойруппы кольцевого сдвигающего регистра подключены к соответствующим первым входам третьего элемента И, выходы генератора тактовых импульсов с первого по И-й и с (Ч+1)-го по (2 Б)-й соединены соответственно с вторыми входами первых элементов И соответствующих групп и с третьими входами вторых элементов И соответствующих групп, (2 Б)-й и (2 М+1)-й выходы генератора тактовых импульсов подключены соответственно к входу сдвига кольцевого сцвкгающего регистра к второму входу третьего элемента И, выход которого является контрольным выходом блока пробного исправления ошибок, выходы и первых элементов И (и= 11 1) объединены с выходамк соответствующих вторых элементов И к являются информационньпи выходами блока пробного исправления ошбок, третьи входы первых элементов И объединены и являются информационным входом блока пробного исправления ошибок, вход генератора такто- вых импульсов и установочньп входкольцевого сдвигающего регистра являются соответственно управляюшим и установовным вхОлами бл 1 еа пробноОисправления ошибок.1287296 Лугов аказ 7730/ 59 Тираж 899 ВНИИПИ Государственнпо делам изобретен 3035, Москва, Ж, Ра Подписноеитета СССР к й и крытиинаб., д. 4 а Проектная,4 дактор А. Долин изводственно-поли Составитель О. Ревинск Техред Л.Сердюкова К ское предприятие, г. Ужгород,

СмотретьЗаявка

3853240, 25.12.1984

ПРЕДПРИЯТИЕ ПЯ Р-6609

УСТИНОВ ГЕННАДИЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: H03M 13/51

Метки: исправления, ошибок

Опубликовано: 30.01.1987

Код ссылки

<a href="https://patents.su/6-1287296-ustrojjstvo-dlya-ispravleniya-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления ошибок</a>

Предыдущий патент: Устройство для коррекции ошибок

Следующий патент: Устройство для декодирования линейных кодов

Случайный патент: Устройство для опрессовки электрических обмоток