Устройство для выбора заданного числа повторений двоичных чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1267402

Автор: Калиниченко

Текст

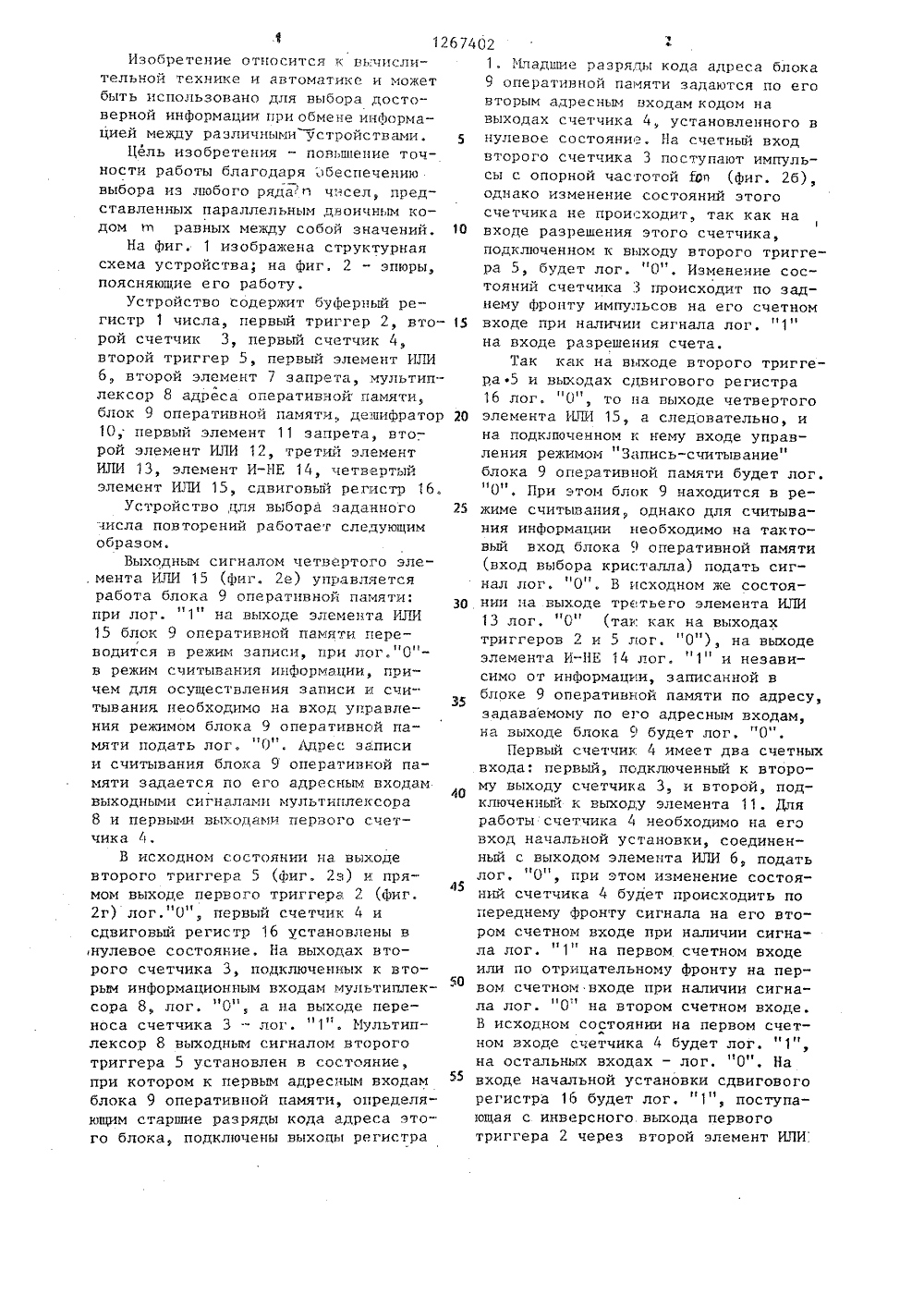

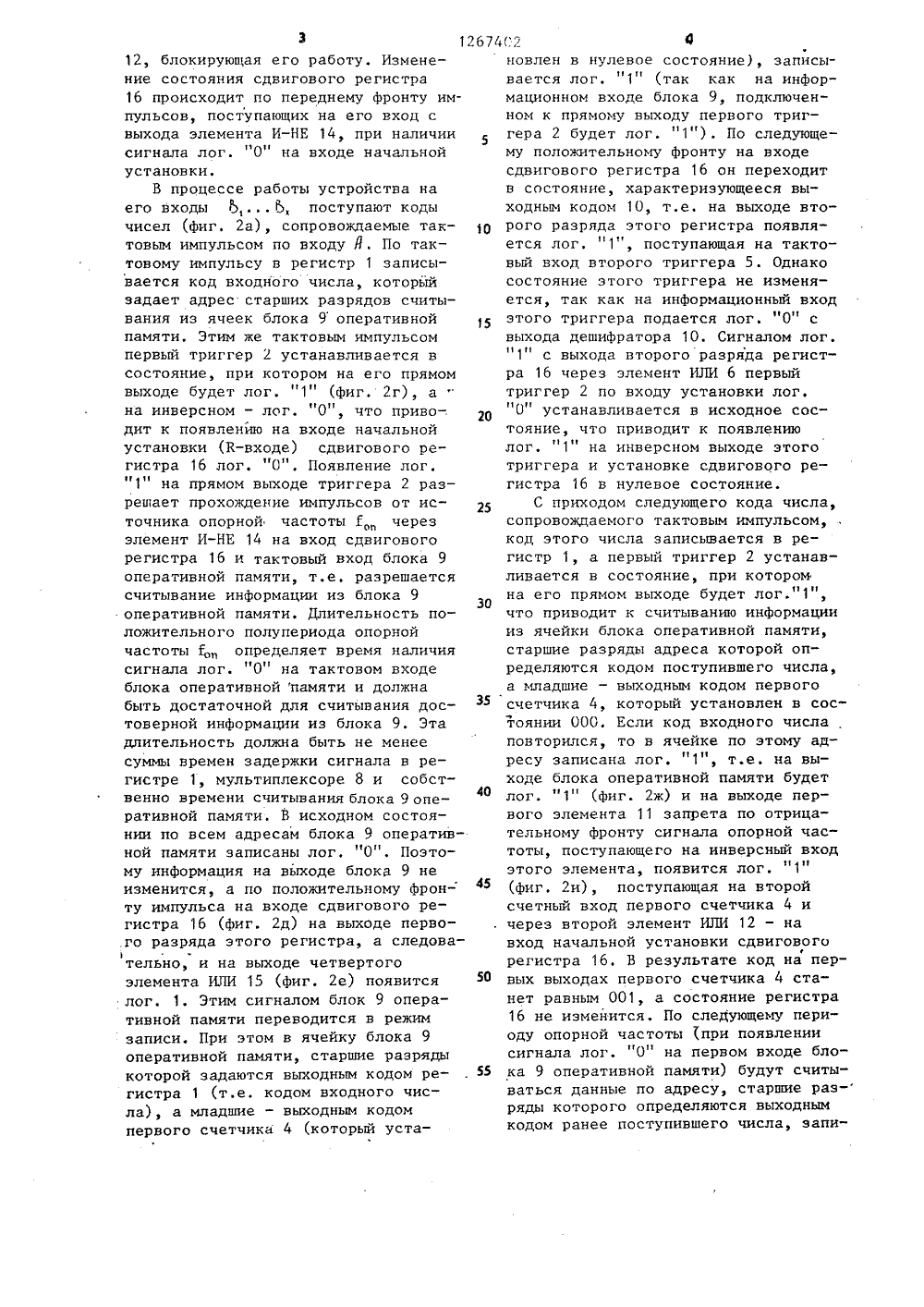

.10.81,(54) УСТРОЙС ЧИСЛА ПОВТОР (57) Изобрет лительной те может быть и достоверной информацией ВО ДЛЯ ВЫБОРА 3 НИИ ДВОИЧНЫХ ЧИ ние относится к нике и автоматик пользовано для в нформации при о ежду различными изобретения явл АДАННОГЕЛвычисе и ыбораменеустройяется стоя ствами, Цель ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЬПИИ(56) Авторское свидетФ 378842, кл. С 06 РПатент Великобритакл. С 4 А, опублик. 1 повышение точности работы благодаряобеспечению выбора из любого ряда ичисел, представленных параллельнымдвоичным кодом ш равных между собойзначений, Устройство содержит буферный регистр числа, счетчики, триггеры, элементы ИЛИ, запрета, И-НЕ, блокоперативной памяти, мультиплексорадреса оперативной памяти, дешифратор, сдвиговый регистр. В блок оперативной памяти устройства записыва"ется массив чисел, имеющий ш равныхчисел.,Цикл работы заканчиваетсяпосле выбора кода числа, записываемого в регистре, ш раз. При отсутствии равных чисел устройство автоматически устанавливается в исходное12Изобретение относится к вь,числительной технике и автоматике и можетбыть использовано для выбора достоверной информации при обмене информа -цией между различными устройствами.Цель изобретения - повышение точности работы благодаря обеспечениювыбора из любого ряда:о чсел, представленных параллельным двоичным кодом п равных между собой значений.На фиг, 1 изображена структурнаясхема устройства; на Фиг. 2 - эпюры,поясняющие его работу,Устройство содержит буферный регистр 1 числа, первый триггер 2, второй счетчик 3, первый счетчиквторой триггер 5, первый элемент ИЛИ6, второй элемент 7 запрета, мультиплексор 8 адреса оперативной памяти,блок 9 оперативной памяти дешифратор10, первый элемент 11 запрета, вто-,рой элемент ИЛИ 12, третий элементИЛИ 13, элемент И-НЕ 14, четвертыйэлемент ИЛИ 15, сдвиговый регистр 16.Устройство для выбора заданногочисла повторений работает следующимобразом,Выходным сигналом четвертого эле,мента ИЛИ 15 (Фиг. 2 е) управляетсяработа блока 9 оперативной памяти;при лог. "1" на выходе элемента ИЛИ15 блок 9 оперативной памяти переводится в режим записи, при лог, 0"в режим считывания информации, причем для осуществления записи и считывания необходимо на вход управления режимом блока 9 оперативной памяти подать лог, "О". Адрес записии считывания блока 9 оперативной памяти задается по его адресным входамвыходными сигналами мультиплексора8 и первыми выходами первого счетчикаВ исходном состоянии на. выходевторого триггера 5 (Фиг. 2 з) и прямом выходе первого триггера 2 (фиг,2 г) лог."0", первый счетчик 4 исдвиговый регистр 16 установлены внулевое состояние. На выходах второго счетчика 3, подключенных к вторым информационным входам мультиплексора 8, лог.О", а на выходе переноса счетчика 3 - лог. "1. Мультиплексор 8 выходным сигналом второготриггера 5 установлен в состояниепри котором к первым адресным входамблока 9 оперативной памяти, определяющим старшие разряды кода адреса этого блока, подключены выходы регистра 674021. Младшие разряды кода адреса блока 9 оперативной памяти задаются по его вторым адресным входам кодом на выходах счетчика 4, установленного в нулевое состояние, На счетный вход второго счетчика 3 поступают импульсы с опорной частотой Гоп (фиг. 2 б), однако изменение состояний этогосчетчика не прои. ходит, так как на1входе разрешения этого счетчика, подключенном к выходу второго триггера 5, будет лог. "О", Изменение состояний счетчика 3 происходит по заднему фронту импульсов на его счетномвходе при наличии сигнала лог. "1" на входе разрешения счета.Так как на выходе второго триггера 5 и выходах сдвигового регистра16 лог. "0", то на выходе четвертогоэлемента ИЛИ 15, а следовательно, и на подключенном к нему входе управления режимом "Запись-считывание"блока 9 оперативной памяти будет лог."0". При этом блок 9 находится в режиме считывания, однако для считывания информации необходимо на тактовый вход блока 9 оперативной памяти (вход выбора кристалла) подать сигнал лог. "О", В исходном же состоянии на выходе третьего элемента ИЛИ 13 лог. "О" (так как на выходах триггеров 2 и 5 лог. "О"), на выходе элемента И-НЕ 14 лог. "1" и независимо от информации, записанной вблоке 9 оперативной памяти по адресу, задаваемому по его адресным входам, на выходе блока 9 будет лог, "О".Первый счетчик 4 имеет два счетныхвхода: первый, подключенный к второму выходу счетчика 3, и второй, подключенный к выходу элемента 11. Для работы счетчика 4 необходимо на его вход начальной установки, соединенный с выходом элемента ИЛИ 6, подать лог, "О", при этом изменение состояний счетчика 4 будет происходить по переднему Фронту сигнала на его втором счетном входе при наличии сигнала лог. "1" на первом счетном входе или по отрицательному фронту на первом счетном входе при наличии сигнала лог. О 1 на втором счетном входе.В исходном состоянии на первом счетном входе счетчика 4 будет лог. "1" на остальных входах - лог. "О". На входе начальной установки сдвигового регистра 16 будет лог, "1", поступающая с инверсного выхода первого триггера 2 через второй элемент ИЛИ:3 1 12, блокирующая его работу. Изменение состояния сдвигового регистра16 происходит по переднему фронту импульсов, поступающих на его вход с выхода элемента И-НЕ 14, при наличии сигнала лог. "0" на входе начальной установки.В процессе работы устройства на его входы Ь, Ь поступают коды чисел (фиг. 2 а), сопровождаемые тактовым импульсом по входу В . По тактовому импульсу в регистр 1 записывается код входного числа, которйй задает адрес старших разрядов считывания из ячеек блока 9 оперативной памяти. Этим же тактовым импульсом первый триггер 2 устанавливается в состояние, при котором на его прямом выходе будет лог. "1" (Фиг. 2 г), ана инверсном - лог. "0", что приводит к появленйю на входе начальной установки (К-входе) сдвигового регистра 16 лог. "0". Появление лог. "1" на прямом выходе триггера 2 раз - решает прохождение импульсов от источника опорной частоты Гчерез элемент И-НЕ 14 на вход сдвигового регистра 16 и тактовый вход блока 9 оперативной памяти, т.е. разрешается считывание информации из блока 9 оперативной памяти. Длительность положительного полупериода опорной частоты Гопределяет время наличия сигнала лог. 0" на тактовом входе блока оперативной памяти и должна быть достаточной для считывания достоверной информации из блока 9. Эта длительность должна быть не менее суммы времен задержки сигнала в регистре 1, мультиплексоре 8 и собственно времени считывания блока 9 оперативной памяти. В исходном состоянии по всем адресам блока 9 оперативной памяти записаны лог. "0", Поэтому информация на выходе блока 9 не изменится, а по положительному Фрон- ту импульса на входе сдвигового регистра 16 (Фиг. 2 д) на выходе первого разряда этого регистра, а следовательно, и на выходе четвертого элемента ИЛИ 15 (фиг. 2 е) появится лог. 1. Этим сигналом блок 9 оперативной памяти переводится в режим записи, При этом в ячейку блока 9 оперативной памяти, старшие разряды которой задаются выходным кодом регистра 1 (т.е. кодом входного числа), а младшие - выходным кодом первого счетчика 4 (который уста 267402 4 новлен в нулевое состояние), записывается лог. "1" (так как на информационном входе блока 9, подключенном к прямому выходу первого триггера 2 будет лог. "1"). По следующему положительному фронту на входесдвигового регистра 16 он переходитв состояние, характеризующееся выходным кодом 10, т.е. на выходе второго разряда этого регистра появляется лог. "1", поступающая на тактовый вход второго триггера 5. Однакосостояние этого триггера не изменяется, так как на информационный входэтого триггера подается лог. "0 свыхода дешифратора 10. Сигналом лог."1" с выхода второго разряда регистра 16 через элемент ИЛИ 6 первыйтриггер 2 по входу установки лог,"0" устанавливается в исходное состояние, что приводит к появлению 10 15 20 лог, "1" на инверсном выходе этого 25ЗО4050 триггера и установке сдвигового регистра 16 в нулевое состояние.С приходом следующего кода числа, сопровождаемого тактовым импульсом, код этого числа записывается в регистр 1, а первый триггер 2 устанавливается в состояние, при которомна его прямом выходе будет лог."1",что приводит к считыванию информациииз ячейки блока оперативной памяти,старшие разряды адреса которой определяются кодом поступившего числа,а младшие - выходным кодом первогосчетчика 4, который установлен в состоянии 000. Если код входного числаповторился, то в ячейке по этому адресу записана лог. "1", т.е. на выходе блока оперативной памяти будетлог. "1" (фиг. 2 ж) и на выходе первого элемента 11 запрета по отрицательному фронту сигнала опорной частоты, поступающего на инверсный вход этого элемента, появится лог. "1" (фиг. 2 и), поступающая на второй счетный вход первого счетчика 4 и через второй элемент ИЛИ 12 - на вход начальной установки сдвиговогоФ регистра 16. В результате код на первых выходах первого счетчика 4 станет равным 001, а состояние регистра 16 не изменится. По следующему периоду опорной частоты (при появлении сигнала лог. "0" на первом входе блока 9 оперативной памяти) будут считываться данные по адресу, старшие раз- ряды которого определяются выходным кодом ранее поступившего числа, запиУстройство для выбора заданного числа повторений двоичных чисел, содержащее блок оперативной памяти, первый счетчик, второй счетчик, о тл и ч а ю а; е е с я тем, что, с цель)о упрощения, в него введены буФерный регистр числа, .мультиплексор адреса оперативной памяти, первый, второй, третий и четвертый элементы ИЛИ, дешиФратор, первьй и второй триггеры,3 12674санного в регистре 1, а младшие - выходным кодом первого счетчика 4,равным 001. По этому адресу в блоке 9 в исходном состоянии был записан лог. 0", поэтому по следующемуположительному Фронту импульса, пос 5тупающему на счетный вход регистра16, последний переходит в состояние,при котором на выходе его пер:вогоразряда будет лог, "1", Выходным сигналом первого разряда регистра 16блок оперативной памяти переводитсяв режим записи и в него по адресу,определяемому кодами на выходах регистра 1 и счетчика 4, записываетсялог. "1", после чего первый триггер2 и регистр 16 устанавливаются в исходное состояние аналогичн описанному. При этом выходным сигналом первого элемента ИЛИ 6 первый счетчик 420по входу начальной установки такжеустанавливается в исходное состояние,При поступлении кода числа, отличного от предыдущих, лог. "1" запишется в ячейку блока 9 оперативной памяти, старшие разрядьг которогоравны коду этого числа, а младшиеравны 000,Если код числа. повторяется М раз(для случая, показанного на Фиг,2,п 1= 3), то после 11 -го повторениякода первый счетчик 4 установится всостояние, при котором на выходедешиФратора 1 Г), а следовательно, ина выходе элемента 7 запрета пояпит 1 (фиг. 2 к) что свидетель ствует о повтореьии кода числа, записанного в регистре 1, Ф раз.После этого при установке регистра 16 в состояние, при котором наЯего втором выходе, подключенном ктактовому входу триггера 5 появитсясигнал лог, "1 , первый первьй триггер 2 устанавливается в исходное состояние, а триггер 5, на инФормационном входе которого лог. 1 с выхода, мдешиФратора 10, устанавливается всостояние лог. "1" (Фиг. 2 з), чтоблокирует прохождение сигнала лог."1" с выхода дешиФратора 10 черезэлемент 7 запрета и разрешает ра 50боту второго счетчика 3. Мультиплексор 8 устанавливается в состояние,при котором к первым адресным входамблока 9 оперативной памяти подключаются выходы второго счетчика 3. Таккак на выходе второго триггера 5лог, "1", то через элемент ИЛИ 1блок 9 переводится в режим записи. Ф о р м у и а изобретения7 12 первый и второй элементы запрета, сдвиговый регистр, элемент И-НЕ, причем группа информационных входов устройства сбединена с группой информационных входов буферного регистра числа, а тактовый вход устройства подключен к входу записи буферного регистра числа и входу установки в "1"первого триггера, выходы буферного регистра числа подключены к первой группе информационных входов мультиплексора, вторая группа информационных входов которого соединена с выходами разрядов второго счетчика, выход переноса второго счетчика подключен к первому счетному входу первого счетчика, второй счетный вход которого соединен с выходом первого элемента запрета, выходы мультиплексора соединены с первой группой адресных входов блока оперативной памяти, вторая группа адресных входов которого подключена к выходам разрядов первого счетчика и входам дешифратора, выход дешифратора подключен к информационному входу второго триггера и входу второго элемента запрета, выход второго элемента запрета является выходом устройства, счетный вход второго счетчика, первый вход элемента И-НЕ, инверсный вход первого элемента запрета подключены к входу сигнала опорной частоты устройства, прямой вход первого элемента запрета соединен с выходом блока оперативной памяти, выход первого элемента запрета подключен к первому входу второго элемента ИЛИ, вто 67402 8рой вход которого йодключен к инверсному выходу первого триггера прямойвыход которого подключен к информационному входу блока оперативной 5 памяти и первому входу третьего элемента ИЛИ, выход которого соединенс вторым входом элемента И-НЕ, выход элемента И-НЕ соединен с тактовым входом блока оперативной памяти 10 и входом управления сдвигом сдвигового регистра, вход начальной установки которого подключен к выходувторого элемента ИЛИ, выход первогоразряда сдвигового регистра подключен к первому входу четвертого элемента ИЛИ, второй вход которого соединен с выходом второго триггера, инверсным входом второго элемента запрета, входом разрешения счета второго счетчика, управляющим входом мультиплексора и вторым входом третьегоэлемента ИЛИ, выход четвертого элемента ИЛИ подключен к входу управления режимом блока оперативной памя ти,.выход второго разряда сдвигового регистра подключен к первому входу первого элемента ИЛИ и к тактовому входу второго триггера, вход установки в "О" которого соединен с выходом переноса первого счетчика ивторым входом первого элемента ИЛИ,вход установки в "1" второго триггера соединен с третьим входом первого элемента ИЛИ и входом начальной 35установки устройства, выход первогоэлемента ИЛИ соединен с входами установки в"О" первого триггера ипервого счетчика.1267407 Составитель В, Журавледактор М. Петрова Техред М,Ходанич рректор Е. Ро дписно Проектная,оизводственно-полиграФическое предприятие, г. Ужгоро 75/47ВНИИПИ Гопо делам113035, Моск ираж 671 Парственного комитета СССРзобретений и открытийБ, Раушская наб д

СмотретьЗаявка

3832984, 29.12.1984

ПРЕДПРИЯТИЕ ПЯ В-2599

КАЛИНИЧЕНКО ВИКТОР ФЕДОРОВИЧ

МПК / Метки

МПК: G06F 7/02

Метки: выбора, двоичных, заданного, повторений, чисел, числа

Опубликовано: 30.10.1986

Код ссылки

<a href="https://patents.su/6-1267402-ustrojjstvo-dlya-vybora-zadannogo-chisla-povtorenijj-dvoichnykh-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для выбора заданного числа повторений двоичных чисел</a>

Предыдущий патент: Устройство для ввода информации

Следующий патент: Устройство для сортировки чисел

Случайный патент: Ферритовый фазовращатель