Преобразователь последовательного кода в параллельный

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1231613

Авторы: Голованов, Ковнир, Федулов, Цодыковский

Текст

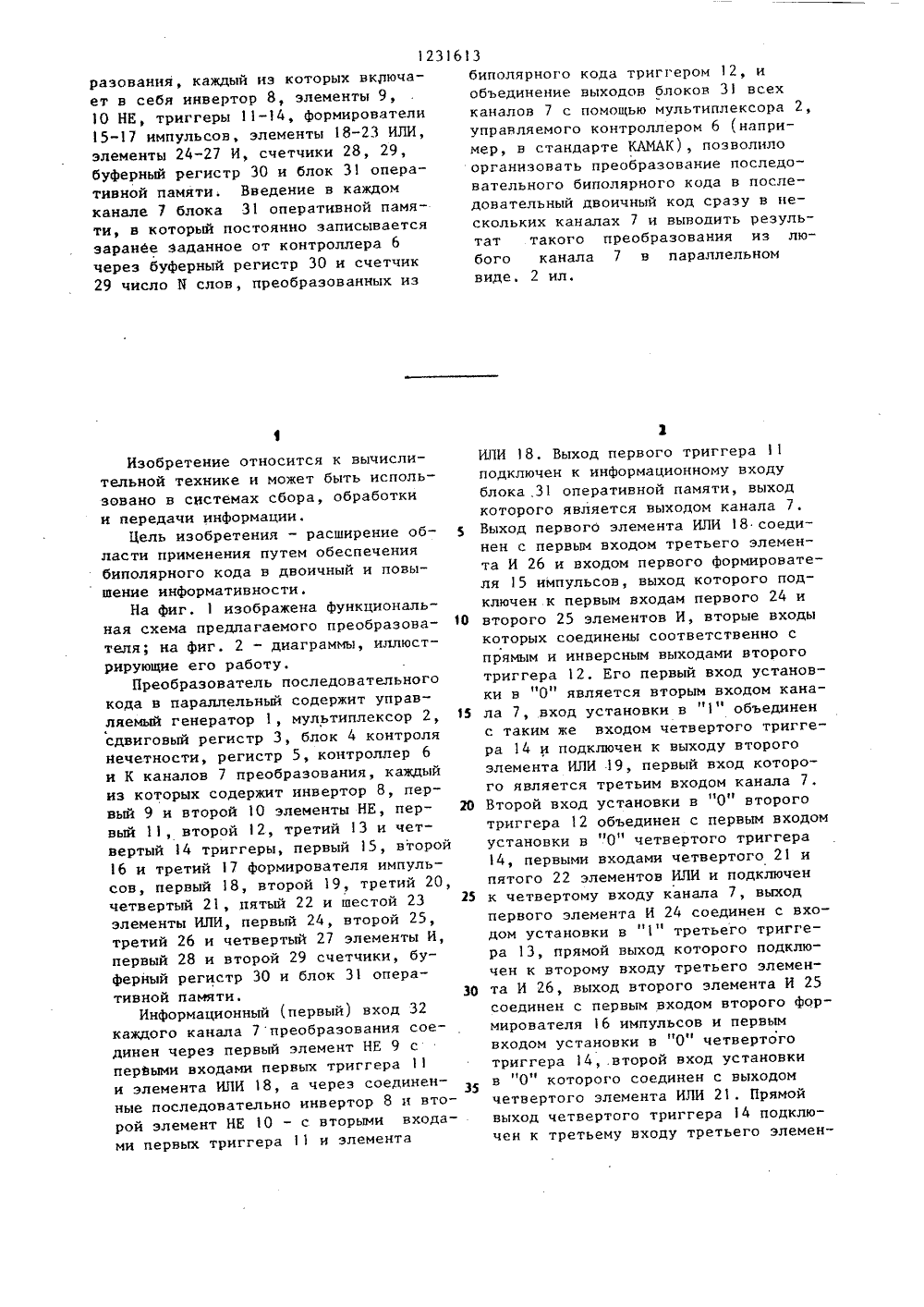

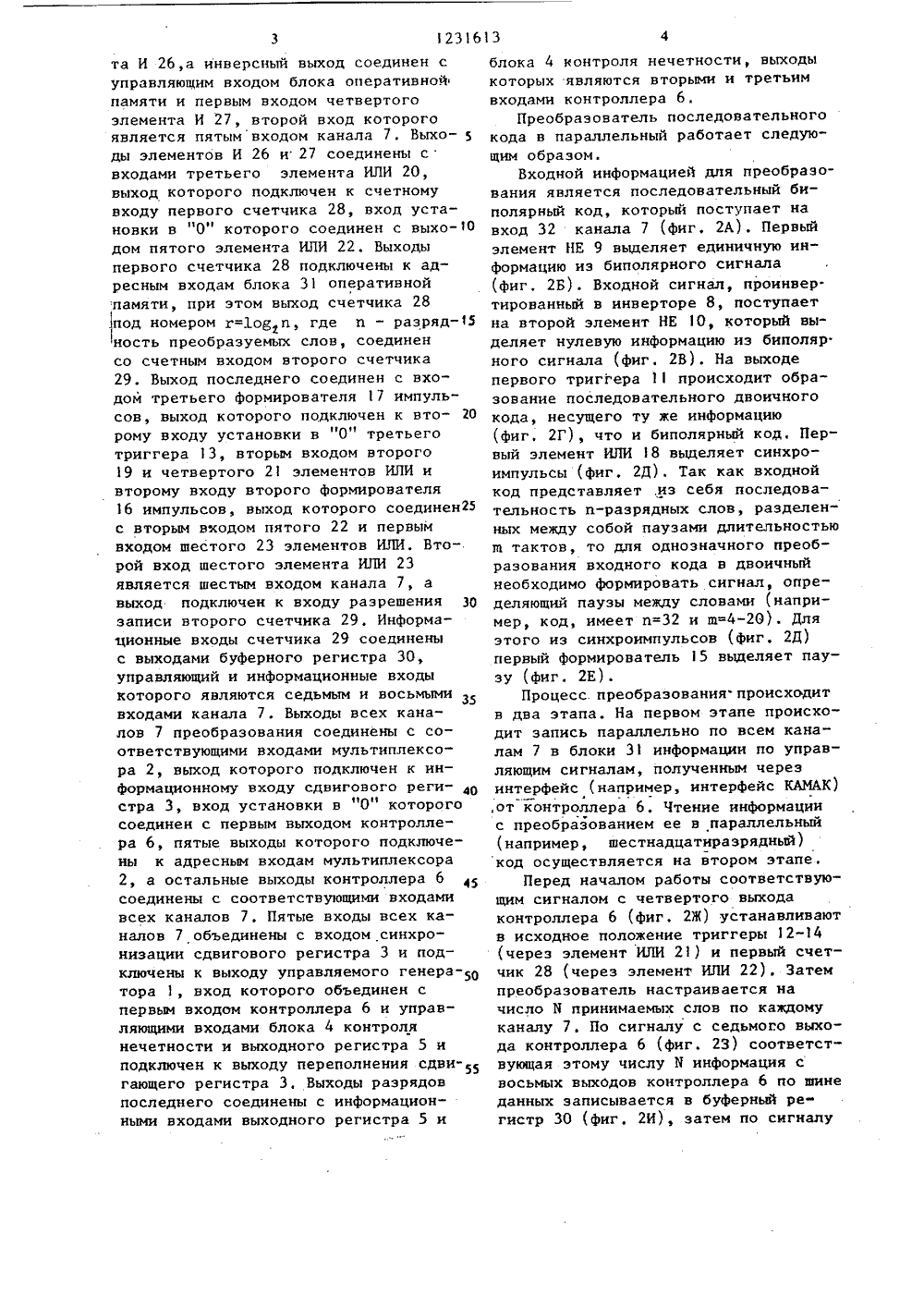

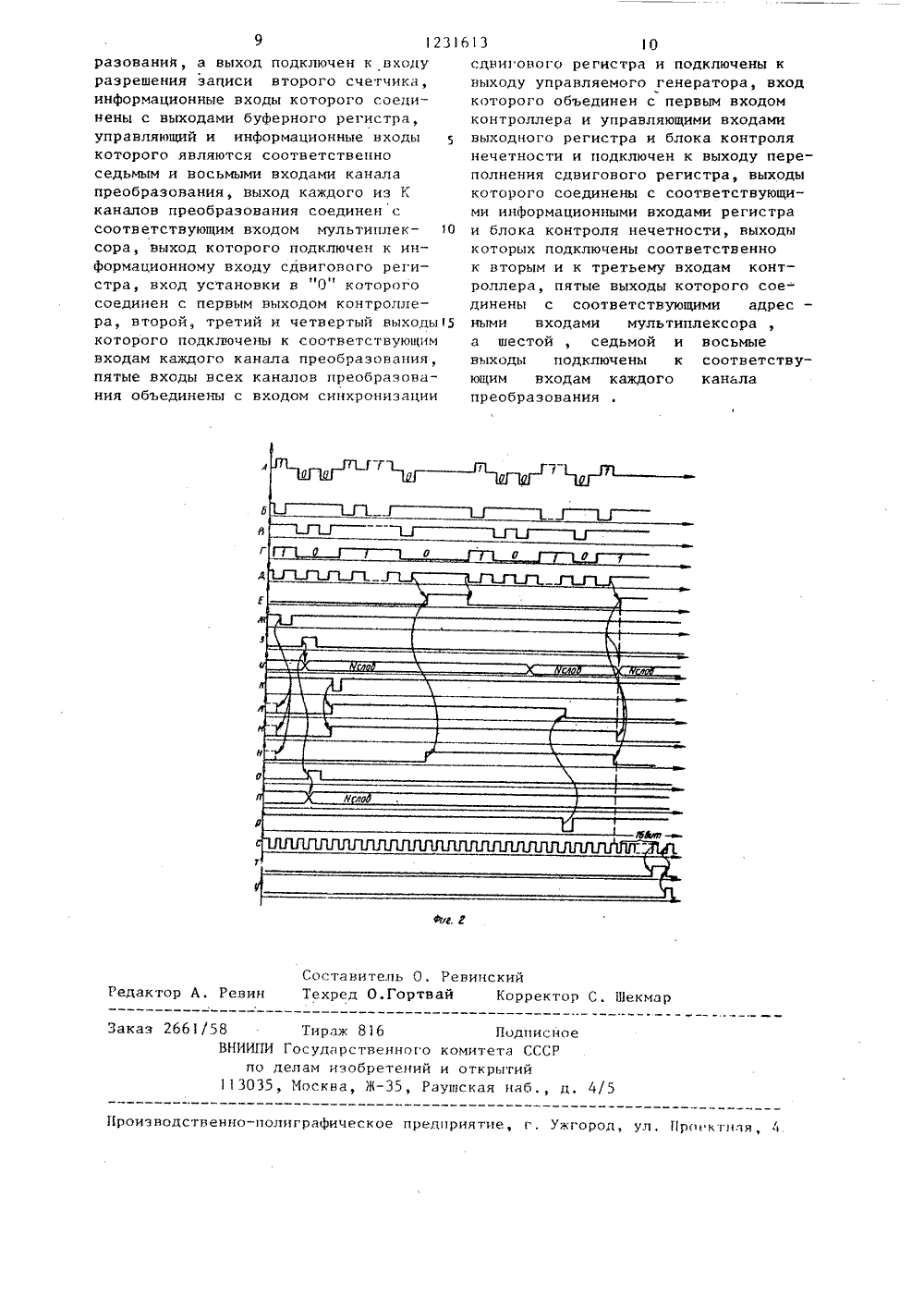

(191 ИИ бо 4 Н 03 М 9/00 5/18 ОПИСАНИЕ ИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ ГОСУДАРСТВЕННЫЙ НОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(54) ПРЕОБРАЗОВАТЕЛЬ ПОСЛЕДОВАТЕЛЬНОГО КОДА В ПАРАЛЛЕЛЬНЫЙ(57) Изобретение относится к вычислительной технике и может быть использовано в системах сбора, обработки и передачи информации, Изобретениепозволит расширить область применения путем обеспечения преобразаваниябиполярного кода в двоичный и повысить информативность. Преобразовательсодержит управляемый генератор 1мультиплексор 2, сдвиговый регистр 3блок 4 контроля нечетности, регистр5, контроллер 6 и К каналов 7 преоб12316 разования, каждый иэ которых включает в себя инвертор 8, элементы 9, 10 НЕ, триггеры 11-14, формирователи 15-17 импульсов, элементы 18-23 ИЛИ, элементы 24-27 И, счетчики 28, 29, буферный регистр 30 и блок 31 оперативной памяти. Введение в каждом канале 7 блока 31 оперативной памяти, в который постоянно записывается заранее заданное от контроллера 6 через буферный регистр 30 и счетчик 29 число И слов, преобразованных из 13биполярного кода триггером 12, иобъединение выходов блоков 31 всехканалов 7 с помощью мультиплексора 2,управляемого контроллером 6 (например, в стандарте КАИАК), позволилоорганизовать преобразование последовательного биполярного кода в последовательный двоичный код сразу в нескольких каналах 7 и выводить результат такого преобразования из любого канала 7 в параллельномвиде, 2 ил.Изобретение относится к вычислительной технике и может быть использовано в системах сбора, обработки и передачи информации.Цель изобретения - расширение области применения путем обеспечения биполярного кода в двоичный и повышение информативности.На фиг. 1 изображена функциональная схема предлагаемого преобразователя; на фиг. 2 - диаграммы, иллюстрируюи 1 ие его работу.Преобразователь последовательного кода в параллельный содержит управляемый генератор 1, мультиплексор 2, сдвиговый регистр 3, блок 4 контроля нечетности, регистр 5, контроллер 6 и К каналов 7 преобразования, каждый из которых содержит инвертор 8, первый 9 и второй 10 элементы НЕ, первый 11, второй 12, третий 13 и четвертый 14 триггеры, первый 15, второй 16 и третий 17 формирователя импульсов, первый 18, второй 19, третий 20, четвертый 21, пятый 22 и шестой 23 элементы ИЛИ, первый 24, второй 25, третий 26 и четвертый 27 элементы И, первый 28 и второй 29 счетчики, буферный регистр 30 и блок 31 оперативной памяти.Информационный (первый) вход 32 каждого канала 7 преобразования соединен через первый элемент НЕ 9 с первыми входами первых триггера 1 и элемента ИЛИ 18, а через соединенные последовательно инвертор 8 и второй элемент НЕ 10 - с вторыми входами первых триггера 11 и элемента 1 О 15 20 25 30 35 ИЛИ 18. Выход первого триггера 11подключен к информационному входублока,31 оперативной памяти, выходкоторого является выходом канала 7.Выход первого элемента ИЛИ 18 соединен с первым входом третьего элемента И 26 и входом первого формирователя 15 импульсов, выход которого подключен к первым входам первого 24 ивторого 25 элементов И, вторые входыкоторых соединены соответственно спрямым и инверсным выходами второготриггера 12. Его первый вход установки в "0" является вторым входом канала 7, вход установки в "1" объединенс таким же входом четвертого триггера 14 и подключен к выходу второгоэлемента ИЛИ 19, первый вход которого является третьим входом канала 7,Второй вход установки в 0 второготриггера 12 объединен с первым входомустановки в "0" четвертого триггера14, первыми входами четвертого 21 ипятого 22 элементов ИЛИ и подключенк четвертому входу канала 7, выходпервого элемента И 24 соединен с входом установки в "1" третьего триггера 13, прямой выход которого подключен к второму входу третьего элемента И 26, выход второго элемента И 25соединен с первым входом второго формирователя 16 импульсов и первымвходом установки в "0" четвертоготриггера 14,.второй вход установкив "0" которого соединен с выходомчетвертого элемента ИЛИ 21. Прямойвыход четвертого триггера 14 подключен к третьему входу третьего элемента И 26,а инверсный выход соединен суправляющим входом блока оперативнойпамяти и первым входом четвертогоэлемента И 27, второй вход которогоявляется пятым входом канала 7. Выходы элементов И 26 и 27 соединены свходами третьего элемента ИЛИ 20,выход которого подключен к счетномувходу первого счетчика 28, вход установки в "0" которого соединен с выходом пятого элемента ИЛИ 22. Выходыпервого счетчика 28 подключены к адресным входам блока 31 оперативной:памяти, при этом выход счетчика 28.под номером г=1 оц и, где и - разряд ность преобразуемых слов, соединенсо счетным входом второго счетчика29. Выход последнего соединен с входом третьего формирователя 17 импульсов, выход которого подключен к второму входу установки в "0 третьеготриггера 13, вторым входом второго19 и четвертого 21 элементов ИЛИ ивторому входу второго формирователя16 импульсов, выход которого соединен 25с вторым входом пятого 22 и первымвходом шестого 23 элементов ИЛИ. Второй вход шестого элемента ИЛИ 23является шестым входом канала 7, авыход подключен к входу разрешения ЗОзаписи второго счетчика 29, Информационные входы счетчика 29 соединеныс выходами буферного регистра 30,управляющий и информационные входыкоторого являются седьмым и восьмымивходами канала 7. Выходы всех каналов 7 преобразования соединены с соответствующими входами мультиплексора 2, выход которого подключен к информационному входу сдвигового регистра 3, вход установки в 0" которогосоединен с первым выходом контроллера 6, пятые выходы которого подключены к адресным входам мультиплексора2, а остальные выходы контроллера 6соединены с соответствующими входамивсех каналов 7, Пятые входы всех каналов 7 объединены с входом синхронизации сдвигового регистра 3 и подключены к выходу управляемого генера-отора 1, вход которого объединен спервым входом контроллера 6 и управляющими входами блока 4 контролянечетности и выходного регистра 5 иподключен к выходу переполнения сдви-гающего регистра 3Выходы разрядовпоследнего соединены с информационными входами выходного регистра 5 и блока 4 контроля нечеткости, выходы которых являются вторыми и третьим входами контроллера 6.Преобразователь последовательного кода в параллельный работает следующим образом.Входной информацией для преобразования является последовательный биполярный код, который поступает на вход 32 канала 7 (фиг, 2 А). Первый элемент НЕ 9 вьщеляет единичную информацию из биполярного сигнала (фиг, 2 Б), Входной сигнал, проинвертированный в инверторе 8, поступает на второй элемент НЕ 10, который выделяет нулевую информацию из биполяр. ного сигнала (фиг. 2 В). На выходе первого триггера 11 происходит образование последовательного двоичного кода, несущего ту же информацию (фиг, 2 Г), что и биполярный код. Первый элемент ИЛИ 18 вьщеляет синхроимпульсы (фиг, 2 Д). Так как входной код представляет ,из себя последовательность и-разрядных слов, разделенных между собой паузами длительностью ш тактов, то для однозначного преобразования входного кода в двоичный необходимо формировать сигнал, определяющий паузы между словами (например, код, имеет п=32 и ш=4-2 О). Для этого из синхроимпульсов (фиг, 2 Д) первый формирователь 15 вьщеляет паузу (фиг. 2 Е).Процесс преобразования происходит в два этапа. На первом этапе происходит запись параллельно по всем каналам 7 в блоки 31 информации по управляющим сигналам, полученным через интерфейс (например, интерфейс КАИАК) ,от контроллера 6. Чтение информации с преобразованием ее в параллельный (например, шестнадцатиразрядный) код осуществляется на втором этапе.Перед началом работы соответствующим сигналом с четвертого выхода контроллера 6 (фиг. 2 Ж) устанавливают в исходное положение триггеры 12-14 (через элемент ИЛИ 21) и первый счетчик 28 (через элемент ИЛИ 22), Затем преобразователь настраивается на число И принимаемых слов по каждому каналу 7, По сигналу с седьмого выхода контроллера 6 (фиг. 23) соответствующая этому числу И информация с восьмых выходов контроллера 6 по шине данных записывается в буферный регистр 30 (фиг, 2 И), затем по сигналус шестого выхода контроллера 6(фиг. 20) данные из буферного регистра 30 переписываются во второй счетчик 29 (фиг. 2 П), Таким образом, насчетчике 29 будет информация о количестве Ы слов преобразования в каждомканале 7, По сигналу с третьего выхода от контроллера 6, являющемусяпусковой командой (фиг, 2 К), тригге- Оры 12 и 14 устанавливаются в(фиг. 2 Л и 2 М) через второй элементИЛИ 19. С приходом паузы сигнал спервого формирователя 15 (Фиг, 2 Е)поступает на первый элемент И 24. 5Благодаря этому, учитывая разрешениеот триггера 12, устанавливается втриггер 13. Таким образом, триггер 14 запрещает импульсы от управляемого генератора 1 на четвертомэлементе И 27 и разрешает вместе стриггером 13 синхроимпульсы с первогоэлемента ИЛИ 18 на третьем элементеИ 26, Синхроимпульсы (фиг. 2 Д) черезтретий элемент ИЛИ 20 отсчитывают адреса ячеек памяти блока 31 с помощьюсчетчика 28. Выход пятого разряда(в случае п=32) счетчика 28 заводится на синхровход счетчика 28, рабо"тающего на вычитание. Таким образом, 30когда в блок 31 запишется заранеезаданное (занесенное в регистр 30)число Б слов, счетчик 29 вырабатываетсигнал переполнения, По этому сигналуимпульс с третьего формирователя 17 35сбрасывает триггер 13 (через элементИЛИ 19), подтверждает установку триггера 12 и формирует одиночный импульсна втором Формирователе 16, которыйв свою очередь через элемент ИЛИ 22 40сбрасывает счетчик 28 в исходное состояние и через элемент ИЛИ 23 вновьнастраивает счетчик на число Б слов,Пауза с первого формирователя 15вновь устанавливает триггер 13 в "1".45Весь цикл записи повторяется для словпо тем же адресам ячеек памяти блока31. Режим записи устанавливается сиг"налом с инверсного выхода триггера 4,50Когда необходимо считать информацию с какого-то канала 7, с второговыхода контроллера 6 вырабатываетсясигнал, поступающий только в данныйканал 7 (фиг. 2 Р), По этому сигналутриггер 12 сбрасывается, но записьслова в память продолжается до егоокончания, По командной части этого сигнала вырабатывается сигнал напервом выходе контроллера 6, которыйустанавливает сдвиговый регистр 3 висходное состояние,С приходом паузы импульс с формирователя 15 через элемент И 25 сбрасывает триггер 14, тем самым подключая управляемый генератор 1 к синхровходу счетчика 28 вместо синхроимпульсов с элемента ИЛИ 18, Этим жесигналом с выхода элемента И 25 запускается Формирователь 16 импульсов,который через элемент ИЛИ 22 сбрасывает счетчик 28 в исходное состояние,а через элемент ИЛИ 23 устанавливаетна счетчике 29 число Б считываемыхиз блока 31 слов, триггер 14 единичным сигналом на своем инверсном выходе устанавливает режим считываниядля блока 31 При обращении к данному каналу 7 для чтения из сигналаконтроллера 6 выделяется ее адреснаячасть.(в структуре интерфейса КАИАК)и с пятых выходов контроллера 6 пода 1ется на мультиплексор 2 для выбораканала 7, Импульсы с генератора 1перебирают с помощью счетчика 28 адреса ячеек памяти в блоке 31, Параллельно эти импульсы подаются на синхровход сдвигового регистра 3, на выходе данных которого появляется синхронно информация из ячеек памяти блока 31.через мультиплексор 2. Такимобразом, информация последовательносдвигается в регистре 3, Когда шестнадцать тактовых импульсов устанавливают нй шестнадцати выходах регистра 3 параллельный выходной код(фиг. 2 С), на выходе переполнениярегистра 3 появляется сигнал, индицирующий завершение преобразования,шестнадцатиразрядов. Этот сигналблокирует управляемый генератор 1 и,поступая на первый вход контроллера6, сигнализирует (например, черезинтерфейс КАМАК) либо о готовностик считыванию, либо о прерывании основной программы для считывания этогокода (фиг. 2 Т). На первом выходеконтроллера 6 появляется команда"Чтение" (фиг. 2 У), которая сбрасывает сдвиговый регистр 3 в исходноесостояние и считывает шестнадцатиразрядное слово из выходного регистра 5. Индицнрующий импульс с выходапереполнения регистра 3 фиксируетинформацию в выходном регистре 5 иблоке ч контроля нечетности. Если произошел сбой по нечетности, то блок 4 контроля вырабатывает сигнал прерывания и подает его на третий вход контроллера 6. Как только сдви говый регистр 3 устанавливается в исходное состояние, снимается блокировка с управляемого генератора 1, следующие шестнадцать бит преобразуются и считываются на вторые входы10 контроллера 6. Когда считается последнее слово, фомирователь 17 импульсов своим выходным сигналом через элементы ИЛИ 19 и 21 и формирователь 6 импульсов устанавливает канал 715 для продолжения записи в блок 31.Формула изобретенияПреобразователь последовательного кода в параллельный, содержащий управляемый генератор, сдвиговый регистр, блок контроля нечетности и первый канал преобразования, состоящий из первого и второго триггеров,25 первого и второго элементов И и первого счетчика, о т л и ч а ю щ и йс я тем, что, с целью расширения области применения путем обеспечения преобразования биполярного кода в 30 двоичный и повышения информативности, в него введены мультиплексор, регистр и контроллер, в первый канал преобразования - третий и четвертый триггеры, второй счетчик, блок оперативной памяти, буферный регистр, первый, второй и третий формирователи импульсов, третий и четвертый элементы И, элементы ИЛИ с первого по шестой, первый и второй элементы НЕ и инвер О тор, и Каналогично первому выполненных каналов преобразования, в каждом из которых вход инвертора объединен с входом первого элемента НЕ и подключен к первому входу канала 45 преобразования, выход первого элемента НЕ соединен с первыми входами первых триггера и элемента ИЛИ, выход инвертора через второй элемент НЕ подключен к вторым входам первых 5 О триггера и элемента ИЛИ, выход первого триггера соединен с информационным входом блока оперативной памяти, выход которого является выходом первого канала преобразования, выход 55 первого элемента ИЛИ подключен к первому входу третьего элемента И и входу первого формирователя импульсов, выход которого соединен с первыми входами первого и второго элементов И, вторые входы которых подключены соответственно к прямому и инверсному выходам второго триггера, первыйвход установки в "О" которого является вторим входом канала преобразования, входы установки в 1" второгои четвертого триггеров объединеныи подключены к выходу второго элемента ИЛИ, первый вход которого являетсятретьим входом канала преобразования,второй вход установки в "Овторогои первый вход установки в "О третьего триггеров объединены с первымивходами четвертого и пятого элементов ИЛИ и подключены к четвертомувходу канала преобразования, выходпервого элемента И соединен с входомустановки в "1" третьего триггера,прямой выход которого подключен квторому входу третьего элемента И,выход второго элемента И соединен спервым входом второго формирователяимпульсов и первым входом установкив "О" четвертого триггера, второйвход установки в О" которого подключен к выходу четвертого элемента ИЛИ,прямой выход соединен с третьим входом третьего элемента И, а инверсный - с управляющим входом блокаоперативнойпамяти и первым входомчетвертого элемента И, второй входкоторого является пятым входом канала преобразования, выходы третьегои четвертого элементов И подключенык входам третьего элемента ИЛИ, выход которого соединен с счетным входом первого счетчика, вход установкив "Окоторого подключен к выходупятого элемента ИЛИ, выходы первого счетчика соединены с адреснымивходами блока оперативной памяти, выход первого счетчика с номером г=1 ояп, где и - разрядность преобразуемого слова, соединен с счетнымвходом второго счетчика, выход которого подключен ко входу третьего формирователя импульсов, выход которогосоединен с вторым входом установкив "О третьего триггера, вторымивходами второго и четвертого элементов ИЛИ и вторым входом второго формирователя импульсов, выход которогоподключен к второму входу пятого элемента ИЛИ и первому входу шестогоэлемента ИЛИ, второй вход которогоявляется шестым входом канала преоб1231613 Составитель О, РевинскийРедактор А. Ревин Техред О.Гортвай Корректор С. Шекмар Заказ 2661/58 Тираж 816 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5Лроизводственно-полиграфическое предприятие, г. Ужгород, ул, Лроктл:зя, 4. разований, а выход подключен к входуразрешения записи второго счетчика,информационные входы которого соединены с выходами буферного регистра,управляющий и информационные входыкоторого являются соответственноседьмым и восьмыми входами каналапреобразования, выход каждого из Кканалов преобразования соединен ссоответствующим входом мультиплексора, выход которого подключен к информационному входу сдвигового регистра, вход установки в "Окоторогосоединен с первым выходом контроллера, второй, третий и четвертый выходыкоторого подключены к соответствующимвходам каждого канала преобразования,пятые входы всех каналов преобразования объединены с входом синхронизации сдвигового регистра и подключены квыходу управляемого генератора, входкоторого объединен с первым входомконтроллера и управляющими входамивыходного регистра и блока контролянечетности и подключен к выходу переполнения сдвигового регистра, выходыкоторого соединены с соответствующими информационными входами регистра 10 и блока контроля нечетности, выходыкоторых подключены соответственнок вторым и к третьему входам контроллера, пятые выходы которого соединены с соответствующими адрес - 5 ными входами мультиплексораа шестой , седьмой и восьмыевыходы подключены к соответствующим входам каждого каналапреобразования

СмотретьЗаявка

3763991, 28.06.1984

ПРЕДПРИЯТИЕ ПЯ М-5537

ГОЛОВАНОВ НИКОЛАЙ АЛЕКСАНДРОВИЧ, КОВНИР ВИКТОР ИВАНОВИЧ, ФЕДУЛОВ АЛЕКСАНДР НИКОЛАЕВИЧ, ЦОДЫКОВСКИЙ ЕВГЕНИЙ ИСИДОРОВИЧ

МПК / Метки

Метки: кода, параллельный, последовательного

Опубликовано: 15.05.1986

Код ссылки

<a href="https://patents.su/6-1231613-preobrazovatel-posledovatelnogo-koda-v-parallelnyjj.html" target="_blank" rel="follow" title="База патентов СССР">Преобразователь последовательного кода в параллельный</a>

Предыдущий патент: Прямоотсчетный преобразователь частоты в код

Следующий патент: Приемо-передающий модуль

Случайный патент: Йсесоюзная i