Формирователь сигналов записи и считывания

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

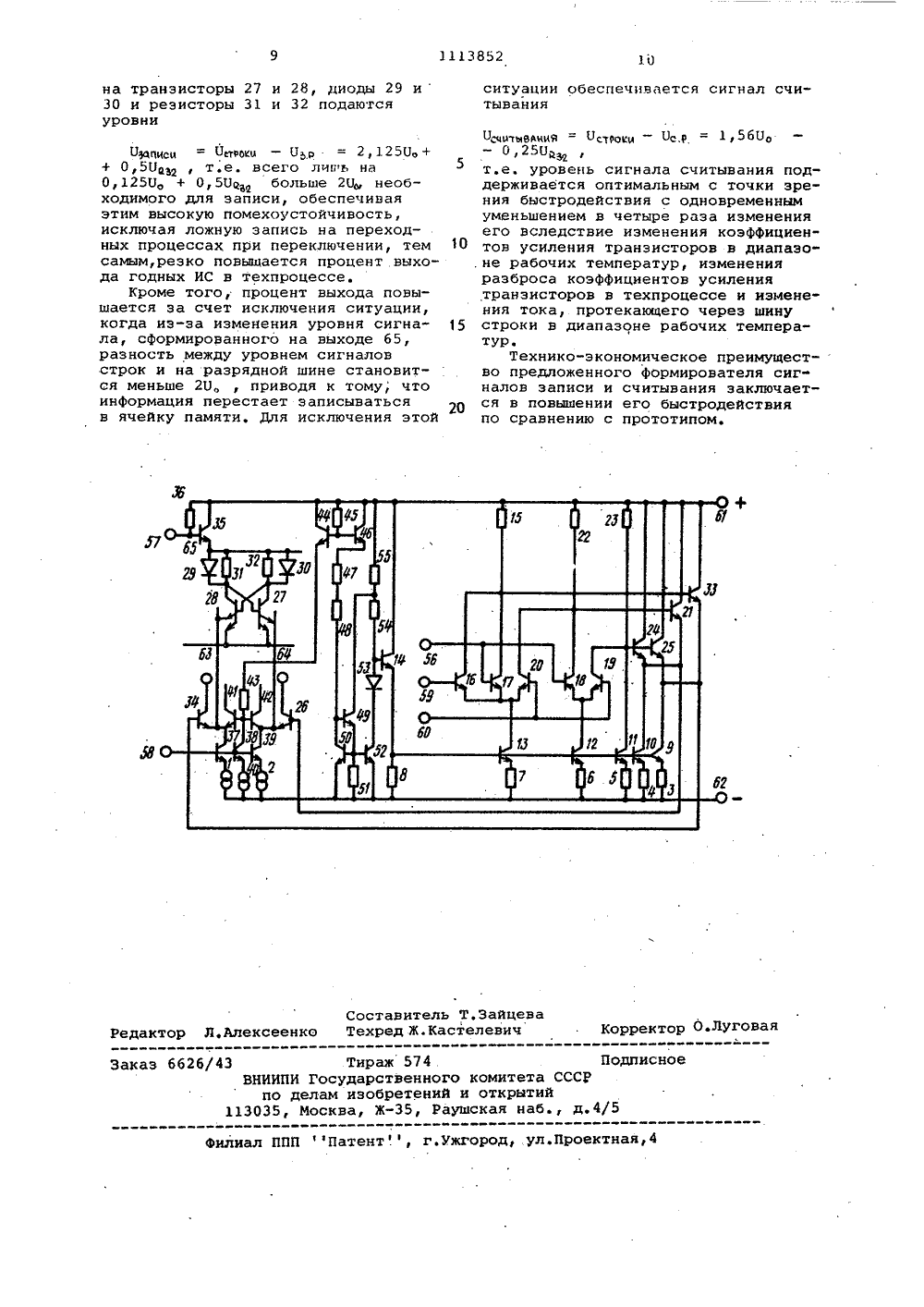

СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕОИХРЕСПУБЛИК 385 9) ОПИСАНИЕ ИЗОБРЕТЕНИЯК АВТОРСКОМЪГ СВИДЕТЕЛЬСТВУ(56) 1.Тарабринпо интегральнымЭнергия, 192.Немудрон Ввующие БИС на иМ., Радио и с105, 131-133 (п Бюл. Р 34ик, И.В.Черняк,П.Сахаров088,8)Б Видр. Смикросхемам.81, с, 307..Г. и др, Быстроереключателях товязь, 1982, с.рототип) . правочник М.,ст 0 ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИЙ(54)(57) ФОРМИРОВАТЕЛЬ СИГНАЛОВ ЗАПИСИ И СЧИТЫВАНИЯ, содержащий переключающие транзисторы с первого подвенадцатый, первый управляющийтранзистор, источники тока, резисторы и усилительные транзисторыс первого по пятый, эмиттеры которых соединены с первыми выводами резисторов с первого по пятый, а базы -с первым выводом шестого резистораи эмиттером первого переключающегорезистора, коллектор которого соединен с первыми выводами резисторов сседьмого по девятый, коллекторамиседьмого, восьмого, девятого и одиннадцатого переключающих транзисторов и шиной питания, причем второйвывод седьмого резистора подключенк базе одиннадцатого переключающеготранзистора и коллекторам второго итретьего переключающих транзисторов,эмиттеры которых соединены с коллекторами пятого усилительного транзистора и эмиттером шестого переключающего транзистора, коллектор которого подключен к второму выноду восьмого резистора, базе седьмого переключающего транзистора и коллекторучетвертого переключающего транзисто"ра, эмиттер которого соединен с коллектором четвертого усилительноготранзистора и эмиттером пятого переключающего транзистора, коллектор которого подключен к второму выводудевятого резистора, коллектору третьего усилительного транзистора ибазам восьмого и девятого переклю-"чающих транзисторов, змиттеры которых соединены соответственно сзмиттером второго усилительного,эмиттером седьмого переключающегои базой десятого переключающеготранзисторов и с змиттером первогоусилительного, эмиттером одиннадцатого переключающего и базой двенадцатого переключающего транзисторов, первые выводы первого и второ- .го источника тока и вторые выводырезисторов с первого по шестой подключены к шине нулевого потенциала, эВбаза второго переключающего транзистора является информационным входомформирователя, базы третьего и четвертого переключающих транзисторовявляются первым управляющим входомформирователя, базы пятого и шестого Дпереключающих транзисторов являютсявходом опорного напряжения, первыйвывод десятого резистора соединен сшиной питания и коллектором первогоуправляющего транзистора, база кото- Фивамрой и второй вывод десятого резисто-,ра являются нторым управляютим вхо- Ъдом формирователя,а эмиттер является (,фодним из адресных выходов формирователя, коллекторы десятого и двенадцатого переключающих транэисто- Яров являются соответственно единичным и нулевым контрольными выходамиформирователя, о т л и ч а ю щ и йс я тем, что, с целью повышениябыстродействия формирователя, в него введены управляющие транзисторыс второго по шестой, стабилизирующие транзисторы с первого по пятый;третий источник тока, диод и резис-.торы с одиннадцатого по семнадцатый,причем эмиттер первого стабилизирующего транзистора соединен с первымвыводом одиннадцатого резистора, а1113852 50 15 база подключена к первому выводудвенадцатого резистора и базе второго стабилизирующего транзистора,эмиттер которого соединен с первымвыводом тринадцатого резистора, нторой вывод которого подключен к первому выводу четырнадцатого резистора, второй вывод которого соединенс базой третьего и коллектором четвертого стабилизирующих транзисторон, коллектор третьего стабилизирующего транзистора подключен к первым выводам шестнадцатого и семнадцатого резисторов, а змиттер - кпервому выводу пятнадцатого резистора и базам четвертого и пятого стабилизирующих транзисторов, эмиттерыкоторых, второй вывод пятнадцатогорезистора и первый вывод третьегоисточника тока соединены с шинойнулевого потенциала, коллектор пятого стабилизирующего транзистора подключен к катоду диода, анод котороИзобретение относится к нычислителькой технике и может быть использовано при создании полупроводниковых .интегральных схем памяти. Известен формирователь сигналов записи и считывания, содержащий транзисторы с первого по восьмой и резисторы, причем коллекторы первого и второго транзисторов подключены соотнетстненно к первым выводам перного и второго резисторов, вторые выводы которых, коллекторы транзисторов с третьего по шестой и первые выводы третьего и четвертого резисторон соединены с шиной нулевого потенциала, эмиттеры первого и второго транзисторов соединены с первым выводом пятого резистора, а базы соответственно с базами третьего и четвертого транзисторов, эммитеры которых подключены к первым выводам шестого и седьмого резисторов, эмиттеры пятого и шестого транзисторов соединены с первыми выводами восьмого и девятого резисторов, а базы - соответственно с вторыми выводами третьего и четвертого резисторов и коллекторами седьмого и. восьмого транзисторов, эмиттеры которых подключены к первому выводу десятого резистора, а базы являются одними иэ входов формирователя, вторые ны" воды резисторов с пятого по десятый подключены к шине питания, другими входами формирователя являются базы первого и второго транзисторон,го соединен с базой первого переключающего транзистора и вторым вынодом шестнадцатого резистора, коллекторы первого и второго стабилизирующих транзисторов и вторые выводы двенадцатого и семнадцатогорезисторов подключены к шине питания, эмиттеры управляющих транзисторон с второго по четвертый соединеныс вторыми выводами источников токас первого по третий, а базы являются третьим управляющим входом формирователя, базы пятого и шестогоуправляющих транзисторов подключенык второму выводу одиннадцатого резистора и коллектору второго управляЬщего транзистора, коллекторы -к шике питания, а эмиттеры - соответственно к коллекторам второго ичетвертого управляющих транзисторови эмиттером двенадцатого и десяТогопереключающих транзисторов и являются адресными выходами формирователя. а выходами - эмиттеры транзисторон стретьего по шестой 11Недостатком этого формирователяявляется низкое быстродействие. Наиболее близким к предагаемому является формирователь сигналов записи и считывания, состоящий из первого и второго источников тока, первые концы которых соединены с шиной земля, которая подключена к первым концам первого - шестого резисторов, вторые концы которых соединены соответственно к эмиттерам первого - пятого транзисторов, базыкоторых соединены с нторым концомшестого резистора и эмиттером шестого транзистора, коллектор которогосоединен с шиной питания и седьмымрезистором, второй конец которойсоединен с коллектором седьмого транзистора, база которого соединена с входом Э", а эмиттер - с коллектором пятого транзистора и эмиттером восьмого транзистора, коллектор которого соединен с коллектором седьмого транзистора, а база - свходом ЗП/СЧ и базой девятоготранзистора, эмиттер которого соединен с коллектором четвертого транзистора и эмиттером десятого транзис 30 тора, база которых соединена с входом Оарри базой одиннадцатоготранзистора, эмиттер которого соединен с эмиттером восьмого транзистора,а коллектор -с коллектором девятоготранзистора, базой двенадцатого травзистора и восьмым резистором, второйконец которого соединен с шиной питания и первым концом девятого резистора, второй конец которого соединен с коллектором десятого и третьего транзисторов, а также с базами 5тринадцатого и четырнадцатого транзисторов, коллекторы которых соединены с шиной питания и коллекторомдвенадцатого транзистора, эмиттеркоторого соединен с эмиттером тринадцатого транзистора, коллекторомвторого транзистора и базой пятнадцатого транзистора, коллектор которого соединен с выходом 1, аэмиттер - с первой разрядной шиной, 15к которой подключен первый эмиттерпервого двухэмиттерного транзистора,второй эмиттер которого включен вцепь хранения, а база соединена сколлектором второго двухэмиттерного транзистора, катодом первого диода и десятым резистором, второй конец которого соединен с анодом первого диода, шиной строки и эмиттеромшестнадцатого транзистора, база котого соединена с входоми через одиннадцатый резистор с коллектором шестнадцатого транзистора,шиной питания и коллектором семнадцатого транзистора, база которогосоединена с коллектором восьмоготранзистора, а эмиттер - с эмиттером четырнадцатого транзистора, коллектором первого транзистора и базойвосемнадцатого транзистора, коллектор которого соединен с выходом "О", а 35эмиттер - с второй разрядной шиной,к которой подключен первый змиттер второгодвухэмиттерного транзистора, второйэмиттер которого включен в цепь хранения, а база соединена с катодом 40второго диода и первым концом двенадцатого резистора, второй конецкоторого соединен с анодом второгодиода и шиной строка, кроме тогопервая разрядная шина соединена с 45вторым концом первого источника токаи эмиттером девятнадцатого транзистора, коллектор которого соединен с шиной питания, а база с выходом 1 фи базой двадцатого транзистора,эмиттер которого соединен с вторымконцом второго источника тока и второй разрядной шиной, а коллектор -с шиной питания и коллектсром шестого транзистора, база которого соединена через тринадцатый резистор с 55шиной питания, а через три последовательно включенных в прямом направлении диода - с шиной земля Г 21,Недостатками этого формирователясигналов записи и считывания являют- бОся низкие быстродействие при считывании и процент выхода годных ИС .приих изготовлении, связанные с тем,что разность уровней напряжения,формируемая цепью строка 1 65 разрядная шина иа ячейку памяти,сильно меняется от образца к образцу, а также в диапазоне рабочих температур из-за того, что большой токвыбранной строки, протекая черезтранзистор, формирующий сигнал записи и считывания строки, создаетсвоим базовым током довольно зиач:. -тельное падение напряжения иа резисторе в цепи его базы, .сильно зависящее от тока записи и считываниястроки, который сильно меняется вдиапазоне рабочих температур, отразброса коэффициента усиления транзистора. Цель изобретения - повышение быстродействия формирователя при считывании.Поставленная цель достигается тем, что в формиоователь сигналов записи и считывания, содержащий переключающие транзисторы с первого по двенадцатый, первый управляющий транзистор, источники тока, резисторы и усилительные транзисторы с первого по пятый, эмиттеры которых соединены с первыми выводами резисторов с первого по пятый, а базы - с первым выводом шестого резистора и змиттером первого переключающего транзистора, коллектор которого соединен с первыми выводами резисторов с седьмого по девятый, коллекторами седьмого, восьмого, девятого и одиннадцатого переключающих транзисторов и шиной питания, причем вывод седьмого резистора подключен к базе одиннадцатого переключающего транзистора и коллекторам второго и третьего переключающих транзисторов, зммитеры которых соединены с коллектором пятого усилительного транзистора и эмиттеоом шестого переключающего транзистора, коллектор которого подключен к второму выводу восьмого резистора, база седьмого переключающего транзистора и коллектор четвертого переключающего транзистора, эмиттер которого соединен с коллектором четвертого усилительного транзистора и эмиттером пятого ,переключающего транзистора, коллектор которого подключен к второму выводу девятого резистора, коллектору третьего усилительного транзистора и базам восьмого и девятого переключающих транзисторов, эмиттеры которых соединены соответственно с эмиттером второго усили,тельного, эмиттером седьмого переклю,чающего и базой десятого переключающего транзисторов и с эмиттером первого усилительного, эмиттером одиннадцатого переключающего и базой двенадцатого переключающего транзисторов, первые выводы первого и второго источников тока и вторыевыводы резисторов с первого по шестой подключены к шине нулевого потенциала, база второго переключаю. -щего транзистора является информационным входом формирователя, базытретьего и четвертого переключающих транзисторов являются первымуправляющим входом формирователя,базы пятого и шестого переключающихтранзисторов являются входом опорного напряжения, первый вывод десятого резистора соединен с шиной питания и коллектором первого управляющего транзистора, база которого ивторой вывод десятого резистора являются вторым управляющим входом фор мирователя, а эмиттер является однимиз адресных выходов формирователя,коллекторы десятого и двенадцатогопереключающих транзисторов являютсясоответственно единичным и нулевымконтрольными выходами формирователя,введены управляющие, транзисторы свторого по шестой, стабилизирующиетранзисторы с первого по пятый, третий источник тока, диод и резисторыс одиннадцатого по семнадцатый, причем эмиттер первого стабилизирующего транзистора соединен с первым выводом одиннадцатого резистора, абаза подключена.к первому выводудвенадцатого резистора и базе второго стабилизирующего транзистора,эмиттер которого соединен с первымвыводом тринадцатого резистора, второй вывод которого подключен к первому выводу четырнадцатого резистора, 35второй вывод которого соединен с базой третьего и коллектором четвертого стабилизирующих транзисторов,коллектор третьего стабилизирующеготранзистора подключен к первым выво пдам шестнадцатого и семнадцатогорезисторов, а эмиттер - к первомувыводу пятнадцатого резистора и базам четвертого и пятого стабилизирующих транзисторов, эмиттеры которых, второй вывод пятнадцатого резистора и первый вывод третьегоисточника тока соединены с шинойнулевого потенциала, коллектор пятого стабилизирующего транзистораподключен к катоду диода, анод которого соединен с базой первого переключающего транзистора и вторым выводом шестнадцатого резистора, коллекторы первого и второго стабилизирующих транзисторов и вторые выводы двенадцатого и семнадцатогорезисторов подключены к шине питания, эмиттеры управляющих транзисторов с второго по четвертый соединены с вторыми выводами источников то- бйка с первого по третий, а базы являются третьим управляющим входом формирователя, базы пятого и шестогоуправляющих транзисторов подключенык второму выводу Одиннадцатого резистора и коллектору второго управляющего транзистора, коллекторы " кшине питания, а эмиттеры - соответственно к коллекторам второго и четвертого управляющих транзисторов иэ.нттерам двенадцатого и десятогопереключающих транзисторов и являются другими адресными выходами формирователяНа чертеже представлена принципиальная схема предложенного формирователя.Формирователь содержит первый 1и второй 2 источники тока, резисторы 3-8 с первого по шестой, усилительные транзисторы 9-13 с первогопо пятый,первыйпереключающий транзистор 14, седьмой резистор 15, переключающие транзисторы 16-21 свторого по седьмой., восьмой 22 идевятый 23 резисторы, переключающиетранзисторы 24-26 с восьмого по десятый,На чертеже показана ячейка памяти,состоящая из запоминающих транзисторов 27 и 28, диодов 29 и 30 и резисторов 31 и 32,Формирователь содержит такжеодиннадцатый ЗЗ и двенадцатый 34переключающие транзисторы, первыйуправляющий транзистор 35, десятыйрезистор 36, управляющие транзисторы 37-39 с второго по четвертый,третий источник 40 тока, пятый 41 ишестой 42 управляющие транзисторы,одиннадцатый резистор 43, первыйстабилизирующий транзистор 44, двенадцатый резистор 45, второй стабилизирующий транзистор 46, тринадцатый 47 и четырнадцатый 48 резисторы,третий 49 и четвертый 50 стабилизирующие транзисторы, пятнадцатый резистор 51, пятый стабилизирующийтранзистор 52, диод 53, шестнадцатый 54 и семнадцатый 55 резисторы.На чертеже обозначены первый 56,второй 57 и третий 58 управляющиеи информационный 59 входы формирователя, вход 60 опорного напряженияформирователя, шина 61 питания ишина 62 нулевого потенциала, выходы63, 64 и 65 формирователя,К выходам 63 и 64 подключаются разрядные шины ячейки памяти, а к выходу 65 - шина строки.Формирователь сигналов записи и считывания работает следующим образом.Уровни записи и считывания формируемые на транзисторах 9-13, 16-21, 24, 25 и 33 и резисторах 3-7, 15,22 и 23 определяются отношениями резисторов:уровень записи 0;уровень считывания 25 где Елл напряжение питания нашине 61;Б - напряжение на базахтранзисторов 11, 12и 13,30ЪВЭЗ, ЪЭзлЛОйг- ПадЕНИЕ НаПряжЕНИя Напереходах база-эмиттер транзисторов 33,34 и 35.С учетом того,что падение напряжения Ц, на переходах база-эмиттерразличных транзисторов в интегральной технологии с большой степеньюточности выдерживается одинаковыми,можно записать 2 г 7 Мо + а а отсюда Влс,р Епллт. В1,5 лйз где По - падение напряжения на переходах база-эмиттер транзисторов.Напряжение Бр определяется источником стабилизирующего напряжения на транзисторе 44 и резисторе 45, которые применяются в качестве отслеживающего элемента, моделирующего сдвиг уровня строки ячейки памяти за счет изменения тока строки в диапазоне рабочих температур, изменения коэффициента усиления транзисторов в диапазоне рабочих температур,а также от разброса коэффициента усиления транзисторов, получаемого в техпроцессе. Транзистор с резисто ром 32 формируют уровень сигнала на выходе 65, позволяя отслеживать уровень сигнала синхронно с изменением уровня, сформированного на шинестРоки, тем самым повышая быстродей-, 5 280 75,йэвр. = Еяллс, - (2 л 560, л. 0,750 )уровень записи 1; с учетом напряжения на объединенных базах транзисторов 11,12 и 13, задаваемого транзисторами 46, 49 и 50, диодом 53 и резисторами 48, 47, 51, 54 и 55Учитывая сдвиг этих уровней на транзисторах 26 и 34, уровни сигналов, формируемые на разрядных выхо дах 63 и 64 можно записать в видейлэ ( (1. в =пллт ( Пв -(1 Юэ 8) 3 Ъэ ззв- ,8 (уровень сигнала записи);ВгПс.р Ест ( ) й (Ъл) ) Фэ гвб- (1 (уровень сигнала считывания),стние формирователя и, кроме того, (а это является самым главным) выбирая ток, задаваемый в эмиттер транзистора 44 со всех выбранных разрядов ячеек памяти (покаэан лишь один разряд, выполненный на транзисторах 27 и 2 О, равный току через транзистор 35, получим на резисторе 45 падение напряжения, абсолютно идентичное падению напряжения на реэис- торе 36 в любых условиях и для любого экземпляра ИС, Таким образом, напряжение на коллекторе транзистора 52 будет повторять напряжение на его коллекторе, равное 20 но превышая его на величину падения напряжения на резисторе 45, так как в цепи коллектора транзистора 52 нагрузка идентична нагрузке в цепи коллектора транзистора 50 за вычетом цепи, моделирующей падение напряжения на резисторе 36..Поэтому напряжение на базе транзистора 14 равно=3 П, - Ц,Для того, чтобы исключить в дальнейшем при работе формирователя вдиапазоне рабочих температур насыщение транзисторов 16-20 (что снизило бы его быстродействие), сдвигаютпервоначальный уровень сигнала записи и считывания на 0,25 (1 путемподключения коллектора транзистора49 к общей точке резисторов 54 и 55,Таким образом, напряжение на базе транзистора 14 равно получается уровень записи на разрядной шине Ъ.р. Еллллт (3 ю 125о л 1 л 5 ПР ) ю уровень считывания на разряднойшине С учетом уровня сформированногона шине строки, т.е. выходе 651113852 Составитель Т.Зайцеваедактор Л,Алексеенко Техред Ж.Кастелевич тор О.Луговая з 6626/43 5 Подписно ВНИИПИ ве Р по де ет 113035, М 354/574нного комитета СССений и открытийРаушская наб., д Тираж Государст лам изобр осква, ЖПатент, г.ужгород, ул.Проектная,4 Фил на транзисторы 27 и 28, диоды 29 и30 и резисторы 31 и 32 подаютсяуровни Ъщиси = бюстики - Ур = 2, 1255, + + 0,50 аз 2, т.е. всего лнгь на 0,1250 + 0,50 больше 2 Ц необходимого для записи, обеспечивая этим высокую помехоустойчивость, исключая ложную запись на переходных процессах при переключении, тем самым,резко повышается процент выхода годных ИС в техпроцессе.Кроме того, процент выхода повышается за счет исключения ситуации, когда иэ-за изменения уровня сигнала, сформированного на выходе 65, разность между уровнем сигналов строк и на разрядной шине становится меньше 20 , приводя к тому, что информация перестает записываться в ячейку памяти, Для исключения этой ситуации обеспечивается сигнал считывания счевия 0 стРом 1,Р. 1 ю 5 61 о0,250т.е. уровень сигнала считывания поддерживается оптимальным с точки зрения быстродействия с одновременнымуменьшением в четыре раза измененияего вследствие изменения коэффициен тов усиления транзисторов в диапазо, не рабочих температур, измененияразброса коэффициентов усилениятранзисторов в техпроцессе и изменения тока, протекающего через шину 15 строки в диапазоне рабочих температур,Технико-экономическое преимущество предложенного формирователя сигналов записи и считывания заключается в повышении его быстродействияпо сравнению с прототипом.

СмотретьЗаявка

3595587, 27.05.1983

ОРГАНИЗАЦИЯ ПЯ А-3106

БОТВИНИК МИХАИЛ ОВСЕЕВИЧ, ЧЕРНЯК ИГОРЬ ВЛАДИМИРОВИЧ, ЕРЕМИН ЮРИЙ НИКОЛАЕВИЧ, САХАРОВ МИХАИЛ ПАВЛОВИЧ

МПК / Метки

МПК: G11C 7/04

Метки: записи, сигналов, считывания, формирователь

Опубликовано: 15.09.1984

Код ссылки

<a href="https://patents.su/6-1113852-formirovatel-signalov-zapisi-i-schityvaniya.html" target="_blank" rel="follow" title="База патентов СССР">Формирователь сигналов записи и считывания</a>

Предыдущий патент: Лентопротяжный механизм

Следующий патент: Дешифратор на кмдп-транзисторах

Случайный патент: Устройство для изготовления арматурных каркасов