Запоминающее устройство с многоформатным доступом к данным

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

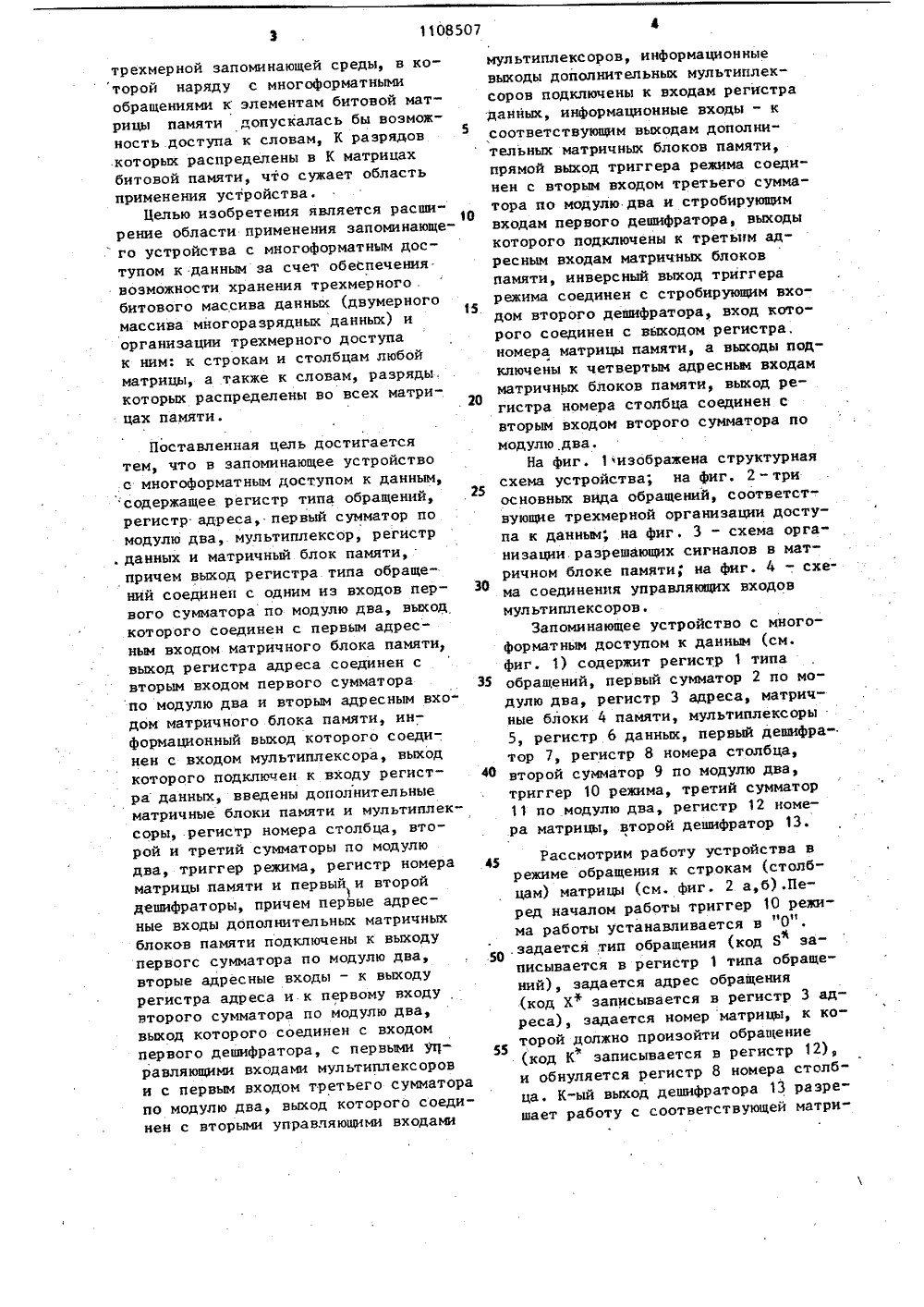

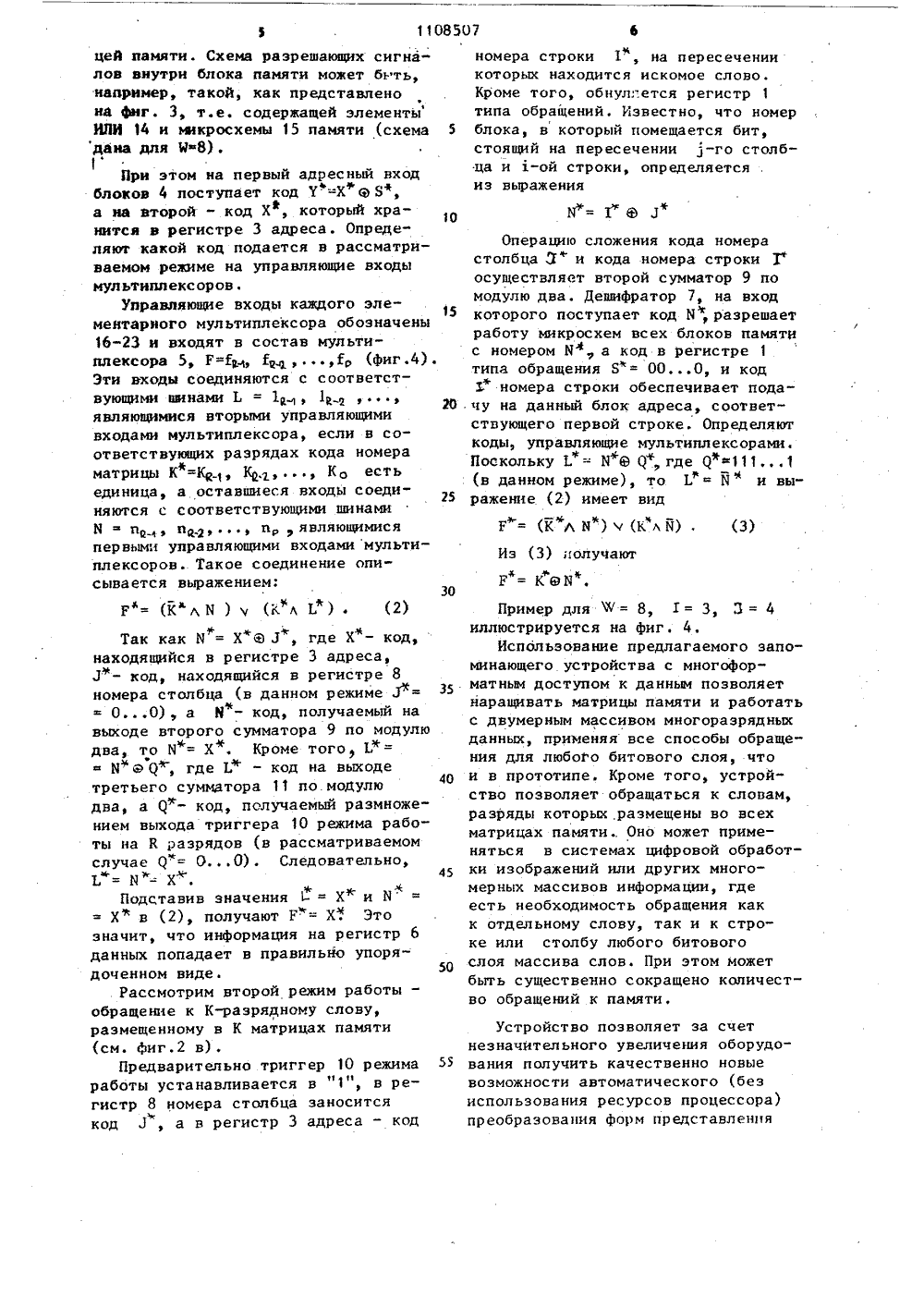

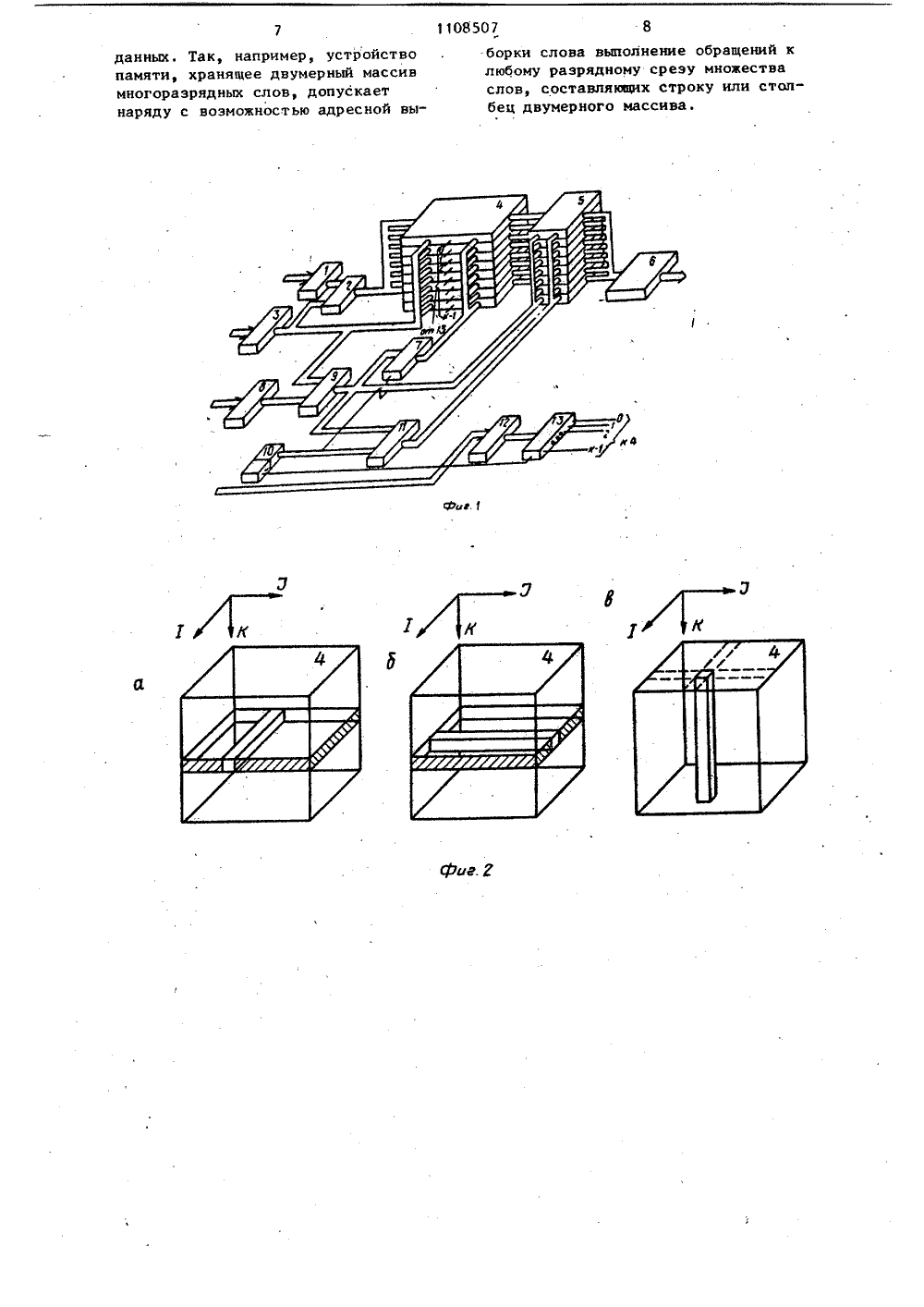

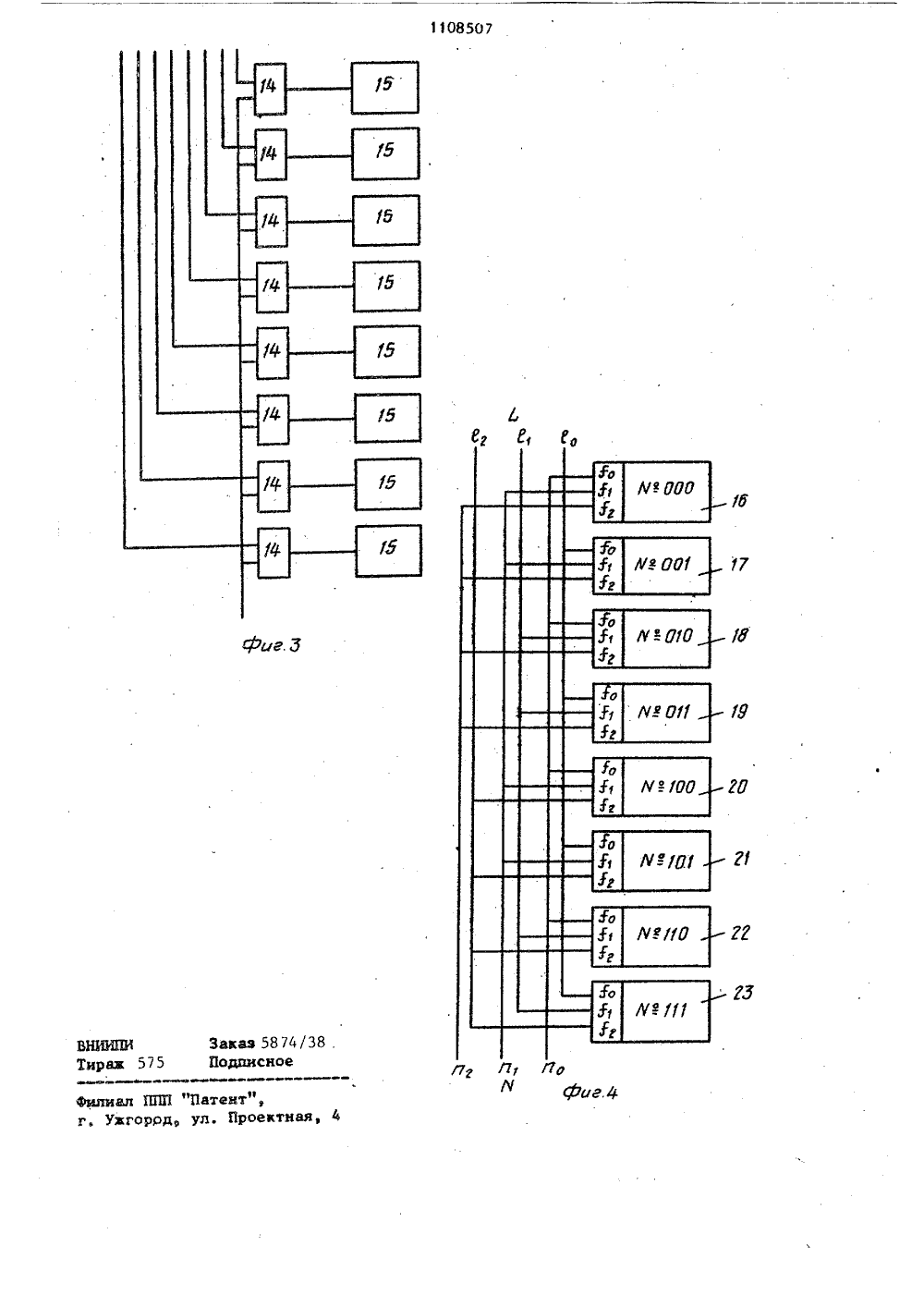

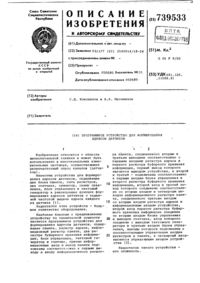

09) 01) СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИН Ь 11 С 15/00 ЩЩ, 1) ПИСАНИЕ ИЗОБРЕТЕНИВТОРСКОМУ СВИДЕТЕЛЬСТВУ етлицкий Ленина т им. тивные"Мир" 74 (про 1 ОСУДАРСТВЕНН) )Й НОМИТЕТ СССПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫТИ(54)(57) ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО СМНОГОФОРМАТНЪМ ДОСТУПОМ К ДАННЫМ,содержащее регистр типа обращений,регистр адреса, первый сумматор помодулю два, матричный блок памяти,мультиплексор и регистр данных,причем выход регистра типа обращений соединен с одним из входов первого сумматора по модулю два, выходкоторого соединен с первым адреснымвходом матричного блока памяти,выход регистра адреса соединен свторым входом первого сумматора помодулю два и вторым адресным входомматричного блока памяти, информационный выход которого соединен совходом мультиплексора, выход которого подключен к входу регистра данных, отличающееся тем,что, с целью расширения областиприменения устройства за счет обеспечения, трехмерного доступа к данным, в него введены дополнительные матричные блоки памяти и мультиплексорь 1, регистр номера столбца, второйи третий сумматоры по модулю два,триггер режима, регистр номера матрицы памяти, первый и второй децяфра"торы, причем первые адресные входыдополнительных матричных блоковпамяти подключены к выходу первогосумматора по модулю два, вторыеадресные входы - к выходу регистраадреса и к первому входу второгосумматора по модулю два, выход которого соединен с входом первогодешифратора, с первыми управляющимивходами мультиплексоров и с первымвходом третьего сумматора по модулюдва, выход которого соединен с вторыми управляющими входами мультиплексоров, информационные выходыдополнительных мультиплексоровподключены к входам регистра данных,информационные входы. - к соответствующим выходам дополнительных матричных блоков памяти, прямой выходтриггера режима соединен с вторымвходом третьего сумматора по модулюдва и стробирующим входом первогодешифратора, выходы. которого подклю-,чены к третьим адресным входам матричных блоков памяти, инверсныйвыход триггера режима соединен сстробирующим входом второго дешифратора, вход которого соединен свыходом регистра номера матрицыпамяти, а выходы подключены к четвертым адресным входам матричныхблоков памяти, выход регистра номера столбца соединен с вторым входомвторого сумматора по модулю цва.07 3 11085Изобретение относится к вычисли- -тельной технике, в частности к запоминаюврюм устройствам, и может бытьиспользовано в специализированныхфсистемах хранения и цифровой обработки изображений, а также в ассоциативных вычислительных системах.Известно запоминающее ;стройствос многоформатным доступом к даннымсодержащее блок памяти и средствадиагональной адресации, допускающиехранение двумерных бинарных массивов с возможностью параллельногодоступа к их строкам и столбцам 13.Недостатком этого устройстваявляются большие аппаратные затраты,Наиболее близким техническимрешением к изобретению является ассоциативное запоминающее устройство,содержащее регистр типа обращений,регистр адреса, сумматор по модулюдва, блок мультиплексоров, регистрданных и блок памяти, причем выходрегистра типа обращений соединен содним иэ входов сумматора по модулюдва, выход которого соединен с первым адресным входом блока памяти,выход регистра адреса соединен суправляющим входом блока мультиплексоров данных, вторым входом 30сумматора по модулю два и вторымадресным входом блока памяти,выход которого соединен через блокмультиплексоров с регистром данных.Блок памяти этого устройства постро 35ен на интегральных микросхемах памяти емкостью 2 бит каждая, где К=1,2,3, Для хранения информациииспользуется Я интегральных микросхем памяти (Я=Р) . Для реализациимногоформатного (к строкам и столб 40цам) доступа, элементы запоминаемойматрицы (бинарного массива ЦЯ)размещаются в интегральных микросхемах памяти таким образом, чтобы45все элементы любой строки или столбца попадали в разные микросхемы памяти. Это обеспечивает возможнбстьодновременной выборки произвольнойстроки или:столбца, Для описаниясоответствия между элементами за 50поминаемой матрицы, номерами интегральных микросхем памяти и адресамив них введем следующие обозначения:3, 1 - номер столбца, строки запоминаемой матрицы: д = 0 -. (14-1); 551 = 0 - (И); Я - номер интегральной микросхемы памяти Н = О-;(М);А - К - разрядный адрес, определяющнй выборку бита в одной микросхемепамяти, Б - тип обращения, Б0 - : (Ъ 7-1),Конкретные значения 3, 1, И,А, Б можно рассматривать как двоичные векторы и обозначить соответственно Л, 1 , М , А , Б. В дальнейшем используются поразрядные операции коньюнкцни Л, дизъюнкции У, сложения по модулю два Э и отрицание - над двоичными векторами,Каждый двоичный элемент запоминаемой матрицы с координатами 1, 3 хранится в микросхеме памяти, код номера которой определяется из соотношения:И=10+3 (1) Для подачи адресов на микросхемыпамяти используются две шины Х и У.По шине Х подается код адреса (Х") срегистра адреса устройства, а пошине У поступает код (У) с выходасумматора по модулю два, на вход+ %которого заведены Х и Б т.е.У=ХО+Б Такое соединение обеспечивает Бразличных способов обращения, причем при Б = 0000 обращение про-.исходит к строкам запоминаемой матрицы, а при,Б= 1111 - к столбцамзапоминаемой матрицы, Номер строкии столбца задается кодом Х+Выражение (1), определяющеераспределение элементов строк (столбцов) по микросхемам памяти, указывает, что для различных строк (столбцов) порядок элементов на шине данных блока памяти различный. Этотпорядок для строки (столбца) с номером 1 (1) определяется соответствующим диадным (по модулю два) сдвигом.Чтобы обеспечить однозначную упоря;доченность при выборке любой строки(стопбца) в устройстве используетсямультиплексор данных, состоящийиз 1 о 8 У групп. Каждая группареализует перестановку элементовстроки (столбца), соответствующуюодиадному сдвигу определенного2", 2, ,2 Ч порядка. Управление включения групп мультиплексора данных осуществляется в зависимости от состояния разрядов регистра адреса Т 2 1,Недостатком этого устройства является невозможность реализациитр ехмер ной зап оми нающей ср еды, в которой наряду с многоформатными обращениями к элементам битовой матрицы памяти допускалась бы возможность доступа к словам, К разрядов которых распределены в К матрицах битовой памяти, что сужает область применения устройства.Целью изобретения является расширение области применения запоминающе го устройства с многоформатным доступом к данным за счет обеспечения- возможности хранения трехмерного . битового массива данных (двумерного массива многоразрядных данных) и организации трехмерного доступа к ним: к строкам и столбцам любой матрицы, а также к словам, разряды, которых распределены во всех матрицах памяти.Поставленная цель достигается тем, что в запоминающее устройство с многоформатным доступом к данным, содержащее регистр типа обращений, регистр адреса, первый сумматор по модулю два, мультиплексор, регистр . данных и матричный блок памяти, причем выход регистра типа обращений соединен с одним из входов первого сумматора по модулю два, вькод которого соединен с первым адресным входом матричного блока памяти, выход регистра адреса соединен с вторым входом первого сумматора по модулю два и вторым адресным входом матричного блока памяти, информационный выход которого соединен с входом мультиплексора, выход которого подключен к входу регистра данных, введены дополнительные матричные блоки памяти и мультиплексоры,.регистр номера столбца, второй и третий сумматоры по модулю два, триггер режима, регистр номера матрицы памяти и первый и второй дешифраторы, причем первые адресные входы дополнительных матричных блоков памяти подключены к выходу первогс сумматора по модулю два, вторые адресные входы - к выходу регистра адреса и к первому входу второго сумматора по модулю два, выход которого соединен с входом первого дешифратора, с первыми уцравляющими входами мультиплексоров и с первым входом третьего сумматора по модулю два, выход которого соединен с вторыми управляющими входами мультиплексоров, информационныевыходы дополнительньк мультиплексоров подключены к входам регистраданных, информационные входы " ксоответствующим вькодам дополнительных матричньк блоков памяти,прямой выход триггера режима соединен с вторым входом третьего сумматора по модулю два и стробирующим 10входам первого дешифратора, выходыкоторого подключены к третьим адресным входам матричньк блоковпамяти, инверсный выход триггерарежима соединен с стробирующим входом второго дешифратора, вход которого соединен с выходом регистра.номера матрицы памяти, а выходы подключены к четвертым адресным входамматричньк блоков памяти, вькод регистра номера столбца соединен свторым входом второго сумматора помодулю два.На фиг. 1 изображена структурнаясхема устройства; на фиг. 2 - три 25основньк вида обращений, соответствующие трехмерной организации доступа к данным; на фиг, 3 - схема орга"низации.разрешающих сигналов в матричном блоке памяти, на фиг. 4 - схеЗ 0 ма соединения управляющих входовмультиплексоров.Запоминающее устройство с многоформатным доступом к данныи (см.фиг. 1) содержит регистр 1 типа 35 обращений, первый сумматор 2 по мо"дулю два, регистр 3 адреса, матричные блоки 4 памяти, мультиплексоры5, регистр 6 данных, первый дешифратор 7, регистр 8 номера столбца, 410 второй сумматор 9 по модулю два,триггер 1 О режима, третий сумматор11 по модулю два, регистр 12 номера матрицы, второй дешифратор 13.45Рассмотрим работу устройства врежиме обращения к строкам (столбцам) матрицы (см. фиг. 2 а,б) .Перед началом работы триггер 10 режи 1ма работы устанавливается в 0.задается тип обращения (код 8 записывается в регистр 1 типа обращений), задается адрес обращения(код Хф записывается в регистр 3 адреса), задается номер матрицы, к которой должно произойти обращение 55(2) Пример для Ф= 8, 1= 3, 3= 4иллюстрируется на фиг, 4.Использование предлагаемого запоминающего устройства с многоформатным доступом к данным позволяетнаращивать матрицы памяти и работатьс двумерным массивом многоразрядныхданных, применяя все способы обращения для любого битового слоя, что40 и в прототипеКроме того, устройство позволяет обращаться к словам,разряды которых .размещены во всехматрицах памяти Оно может применяться в системах цифровой обработ 4 ки изображений или других многомерных массивов информации, гдеесть необходимость обращения какк отдельному слову, так и к строке или столбу любого битовогослоя массива слов. При этом можетбыть существенно сокращено количество обращений к памяти. цей памяти. Схема разрешающих сигналов внутри блока памяти может бьть,например, такой, как представленона 4 аг, 3, т.е. содержащей элементыИДИ 14 и микросхемы 15 памяти (схемадана для Ю 8),При этом на первый адресный входблоков 4 поступает код У. - .Х е 8+,а яа второй - код Х, который храйнится в регистре 3 адреса. Определяют какой код подается в рассматриваемом режиме на управляющие входымул ьтиплекс оров .Управляющие входы каждого элементарного мультиплексора обозначены16-23 и входят в состав мультиплексора 5, Г=Е., ЕГр (фиг,4).Эти входы соединяются с соответствующими шинами Ь = 1., 1являющимися вторыми управляющимивходами мультиплексора, если в соответствующих разрядах кода номераматрицы К =Кр 1, К Ко есть%единица, а оставшиеся входы соединяются с соответствующими шинамиИ п , пя. пр явяющиипервыми управляющими входами мультиплексоров. Такое соединение описывается выражением:Г = (К"лИ)ч (кп Ь)а Так как И = Х О+ 3, где Х - код, находящийся в регистре 3 адреса, ,1"- код, находящийся в регистре 8 номера столбца (в данном режиме 3 ф=00), а К"- код, получаемый на выходе второго сумматора 9 по модулю два, то И = Х, Кроме того Ь=Иэ Я; где Ь+ - код на выходе третьего сумматора 11 по модулю два, а Я- код, получаемый размножением выхода триггера 10 режима работы на К разрядов (в рассматриваемом случае С = 00). Следовательно, Ь=И=ХПодставив значения Ь = Х и ИХ в (2), получают Г. - . Х Это значит, что информация на регистр 6 данных попадает в правильно упорядоченном видеРассмотрим второй режим работы - обращение к К-разрядному слову, размещенному в К матрицах памяти (см. Фиг.2 в).Предварительно триггер 10 режима работы устанавливается в "1", в регистр 8 номера столбца заносится код 1, а в регистр 3 адреса - код номера строки 1, на пересечении которых находится искомое слово .Кроме того, обнул:.ется регистр 1 типа обращений, Известно, что номер 5 блока, в который помещается бит,стоящий на пересечении 1-го столбца и .-ой строки, определяется из выражения Операцию сложения кода номерастолбца 3 и кода номера строки Г осуществляет второй сумматор 9 по модулю два. Дешифратор 7, на вход 5 которого поступает код И, разрешаетработу микросхем всех блоков памяти с номером И" а код в регистре 1 типа обращения Я= 000, и кодномера строки обеспечивает пода чу на данный блок адреса, соответствующего первой строке. Определяют коды, управляющие мультиплексорами.Поскольку Ь = И 9 Я+, где Я 1111 (в данном режиме), то Ье Й " и вы ражение (2) имеет видГ = (К л И ) м (К л Й) , (3) Устройство позволяет за счетнезначительного увеличения оборудо 55 вания получить качественно новыевозможности автоматического (безиспользования ресурсов процессора)преобразования форм представленияданных. Так, например, устройствопамяти, хранящее двумерный массивмногоразрядных слов, допускаетнаряду с воэможностью адресной вы 11 О 85 О 8-борки слова выполнение обращений клюбому разрядному среэу множестваслов, составляющих строку или столбец двумерного массива,

СмотретьЗаявка

3539217, 10.01.1983

ЛЕНИНГРАДСКИЙ ОРДЕНА ЛЕНИНА ЭЛЕКТРОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. И. УЛЬЯНОВА

КАВЕРЗНЕВ ВАЛЕРИЙ ВАСИЛЬЕВИЧ, МЕТЛИЦКИЙ ЕВГЕНИЙ АРОНОВИЧ

МПК / Метки

МПК: G11C 15/00

Метки: данным, доступом, запоминающее, многоформатным

Опубликовано: 15.08.1984

Код ссылки

<a href="https://patents.su/6-1108507-zapominayushhee-ustrojjstvo-s-mnogoformatnym-dostupom-k-dannym.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство с многоформатным доступом к данным</a>

Предыдущий патент: Способ записи и стирания информации на электролюминесцентной структуре

Следующий патент: Аналоговое запоминающее устройство

Случайный патент: Свинцово-кислотного аккумулятора