Вычислительная система

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

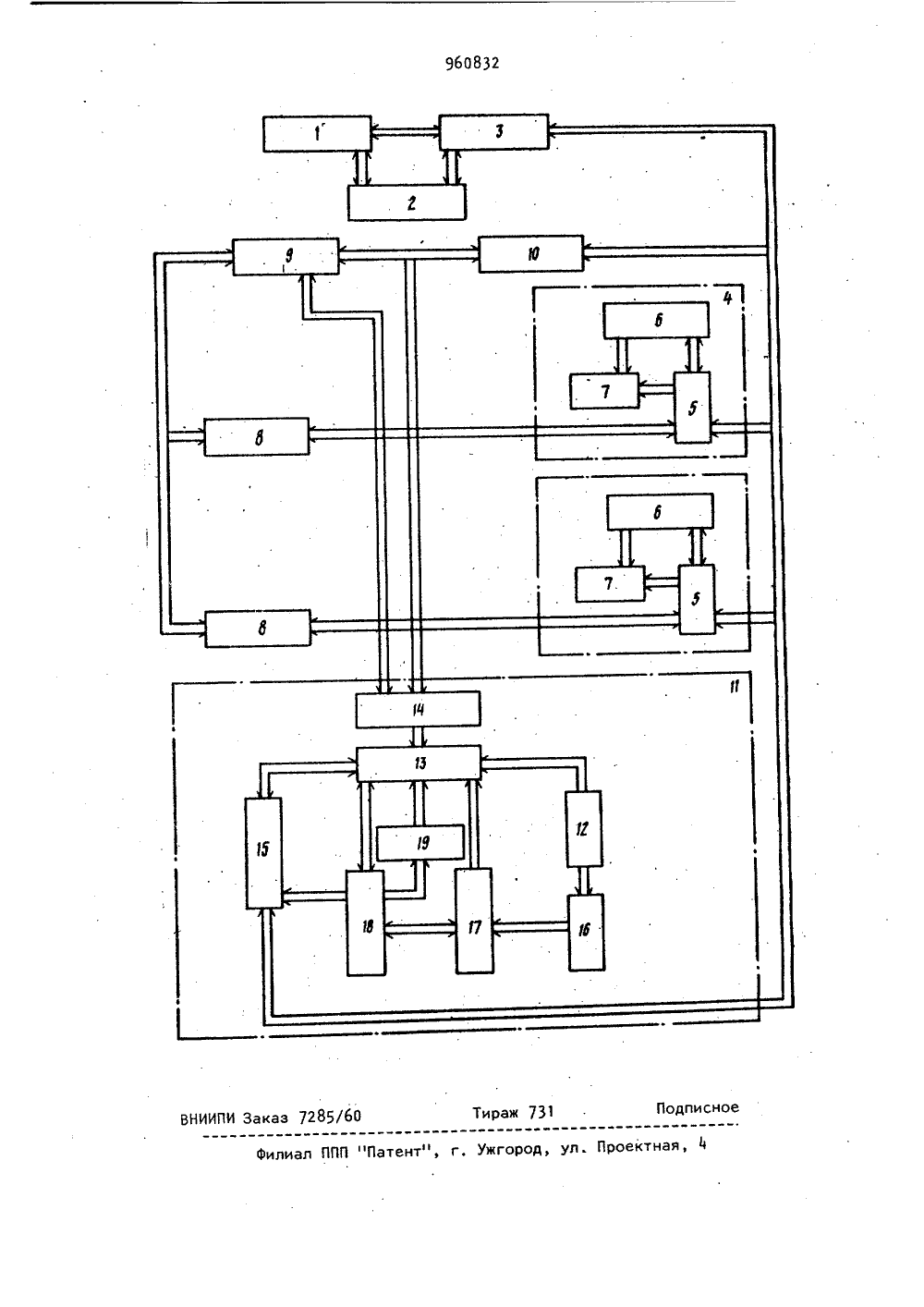

О П И С А Н И Е пи 960832ИЗОБРЕТЕН ИЯ Соизз СоветсникСоциалистическихРеспубпик К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(51)М. Кл.С 06 Г 15/16 С 06 Г 11/00 3 Ьоударотминый квинтет СССР во делзи изобретений и открытий(54) ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА 1Изобретение относится к вычислительной технике и может быть использо.вано для рациональной организации ко"нтроля вычислительных компонентов,состоящих из одной или несколькихвычислительных машин и различных внеш них устройств,Известен вычислительный комплекс,в состав которого входят процессор,блоки управления терминальными устФройствами, блоки связи с устройствомконтроля данных о работе терминалов,устройство контроля данных о работетерминалов 1 11.Недостатком такого вычислительно. го комплекса является ограниченная15глубина контроля, зависящая от используемых наборов входных сигналов,которые генерируются при функционировании комплекса и не являются оптимальными с точки зрения контроля, атакже снижение надежности, обусловленное существованием скрытых неисправностей терминалов в период между 2двумя циклами контроля. Этот период случаен и определяется интенсивностью обмена информацией между процессором и терминалом.Наиболее близкой по технической сущности к предлагаемой является вычислительная система, содержащая оперативное запоминающее устройство,первые входы и первые выходы которого соответственно соединены с первыми вы" ходами и первыми входами процессора, вторые входы и вторые выходы - соответственно с первыми входами канала ввода-вывода, вторые входы и вторые выходы которого соответственно подключены к вторым выходам и вторым входам процессора, третьи входы и третьи выходы - соответственно к первым выходам блока связи с каналом, первым. выходам внешних и к первым входам блока связи с каналом, первым входам внешних устройств, вторые входы и вторые выходы которых соединены соответственно с первыми выходами3 96083 соответствующих формирователей кодов, вторые входы и вторые выходы которых подключены соответственно к первым выходам и первым входам анализатора состояний внешних устройств, вторые входы и вторые выходы которого соединены соответственно с вторыми выходами и вторыми входами блока связи с каналом2 1.Недостатком известной вычислитель о ной системы является снижение быстродействия, которое вызывается возможностью повторения одних и тех же контрольных операций при Функционировании и тестировании .внешних устройств. 15Целью изобретения является повышение быстродействия системы.Для достижения поставленной цели в вычислительную систему, содержащую оперативное запоминающее устрой-о ство, первая группа входов-выходов которого соединена с первой группой вхрдов-выходов процессора, вторая группа входов-выходов которого подключена к первой группе входов-выходов канала ввода-вывода, вторая группа входов-выходов которого подключена к второй группе входов-выходов процессора, третья группа входов-выходов канала ввода-вывода подключена к пер- З вой группе входов-выходов блока связи с каналом, первой группой входов-выходов каждого внешнего устройства, группа выходов каждого. из которых соединена с первой группой входов-выЗ 5 ходов соответствующих Формирователей кодов, вторые группы входов-выходов которых подключены соответственно к первой группе входов-выходов анализатора состояний внешних устройств, вторая группа входов-выходов которого соединена соответственно с второй , группой входов-выходов блока связи с каналом, введено устройство управления очередностью контроля, содержащее блок сопряжения, блок буферной45 памяти, блок обмена, блок вывода данных, генератор сигналов, формирователь адресов блок согласования и блок сравнения, при этом первая группа входов-выходов которого соединена с первой группой входов-выходов форми рователя адресов, вторая группа входов-выходов которого соединена с первой группой входов-выходов блока буферной памяти, первая группа входов- выходов которого подключена к первой группе входов-выходов блока обмена, вторая группа входов-выходов которо 2 4го подключена соответственно к первойгруппе входов внешних устройств, третья группа входов-выходов формирователя адреса подключена к второй группе входов-выходов блока буферной памяти, третья группа входов-выходовкоторого соединена с второй группойвходов-выходов формирователя адреса,четвертая группа входов-выходов блока буферной памяти через блок согласования с четвертой .группой входов-выходов блока сравнения, пятая группавходов-выходов блока буферной памятисоединена с первой группой входов-выходов блока ввода данных, шестая группа входов-выходов блока буферной памяти соединена с группой входов-выходов блока сопряжения, первая группауправляющих входов-выходов которогоподключена к третьей группе входов-выходов анализатора состояния, втораягруппа входов-выходов которого подключена к второй группе управляющихвходов-выходов блока сопряжения, вторая группа выходов блока ввода данныхчерез генератор сигналов подключенак третьей группе входов формирователяадресов. На чертеже приведена блок-схема вычислительной системы.Система содержит процессор 1, оперативное запоминающее устройство 2, канал 3 ввода-вывода, внешние устройства 1, каждое из которых имеет блок 5 обмена, блок 6 логицеской обработки, блок 7 самоконтроля, формирователи 8 кодов, анализатор 9 состояний внешних устройств, блок 10 связи с каналом, устройство 11 управления очередностью контроля, включающее блок 12 ввода данныхублок 13 буферной памяти, блок 11 сопряжения, блок 15 обмена, генератор 16 сигналов, формирователь 17 адресов, блоки 18 и 19 сравнения и согласования.Вычислительный комплекс работает следующим образом.В исходном положении в блоке 13 содержится информация об адресах, количестве и периодах тестового контроля внешних устройств, ячейки с признаками обмена внешних устройств с каналом обнулены. Генераторы 16 настроены на Формирование временных меток с расчетным периодом тестового контроля внешних устройств. Подготовка, ввод и последующая корректировка данных в блоки 13 буферной памяти и генерато5 9608 ры 16 производится с блока 12 вводаданных.В процессе решения функциональных задач внешние устройства обмениваются информацией с каналом 3. Блок 7 осуще-з ставляет контроль работоспособности соответствующего внешнего устройства, формирует информацию о его состоянии и обмене с каналом 3. Данная информация поступает на формирователь 8, 1 ф который формирует код состояния внешнего устройства с признаком обмена Анализатор 9 осуществляет периодический (с малым периодом) опрос фор" мирователей 8 и производит анализ ко ю дов состояния. При наличии изменений в состоянии внешнего устройства 4 код состояния поступает в блок 10 и затем в канал 3При появлении признака обмена внешнего устройства с каналом код состояния с анализатора 9 поступает в блок14, а затем в блок 13 в соответствии с адресами внешних устройств.В блоке 13 производится накопление 23 кодов состояния с признаками обмена по соответствующим устройствам.Генератором 16 осуществляется формирование временных меток с заданными периодами тестового контроля внешних 1 р устройств 4, которые поступают на вход Формирователя 17, формирующего список адресов внешних устройств,контролируемых с данным периодом, инФармация по которым записана в блоке13. После Формирования списка по управляющему сигналу Формирователя 17код состояния первого внешнего устройства из сформированного списка пог ступает из блока 13 в блок 18. В блоке 18 производится анализ признака обмена в коде состояния. Анализ производится путем сравнения поступившего кода состояния с эталонным, Приотсутствии признака обмена в коде состояния адрес соответствующего внешнего устройства поступает в блок 19,согласования, где производится формирование кодограммы для ввода в процессор, После этого производится анализ кода состояния второго внешнегоустройства из списка, затем третьего и т, д.По завершению анализа блоком 18 вырабатывается управляющий сигнал,который поступает в блок 15, а сформированная кодограмма из блока 19 записывается в блок 13. Блок 15 обмена выставляет требование на обмен, по 32 4которому канал 3 осуществляет стандартную операцию ввода-вывода по считыванию с блока 13 буферной памяти и записи в оперативное запоминающее устройство массива данных о смене, После считывания производится обнуление соответствующих ячеек буферной памяти.По программе обработки массива данных, находящейся в устройстве 2, определяется перечень внешних .устройств, подлежащих тестовому контролю за данный временной период. На основании сформированного, перечня управляющей программой тестового контроля производится контроль внешних устройствКонтролируются только внешние устройства, которые в течение периода контроля не участвовали в рабочем обмене. Это позволяет сократить затраты времени на контроль и повысить быстродействие системы.формула изобретенияВычислительная система, содержащая оперативное запоминающее устройство, первая группа входов-выходов которого .соединена с первой, группой входов-выходов процессора, вторая группа вхо-. дов-выходов которого подключена к пер" вой группе входов-выходов канала ввода-вывода, вторая группа входов-выходов которого подключена к второй группе входов-выходов процессора, третья группа входов-выходов канала ввода-вывода подключена к первой группе входов-выходов блока связи с каналом, первой группой входов-выходов каждого внешнего устройства, группа выходов каждого из которых, соединена с первой группой входов-выходов соответствующих формирователей кодов, вторые группы входов-выходов которых подключены соответственно к первой группе входов-выходов анализатора состояний внешних устройств, вторая группа, входов-выходов которого соединена соответственно с второй группой входов-выходов блока связи с каналом, о т л и ч а ю щ а я с я тем, что, с целью повышения быстродействия системы, она содержит устройство управления очередностью контроля, содержащее блок сопряжения, блок буферной памяти, блок обмена, блок вывода данных, генератор сигналов, формирователь адресов, блок согласования иблок сравнения, при этом первая группа входов-выходов которого соединенас первой группой входов-выходов формирователя адресов, вторая группавходов-выходов которого соединенас первой группой входов-выходов блока буферной памяти, первая группа вхо.дов-выходов которого подключена кпервой группе входов-выходов блокаобмена, вторая группа входов-выходов 10которого подключена соответственнок первой группе входов внешних устройств, третья группа входов-выходовформирователя адреса подключена квторой группе входов-выходов блока 5буферной памяти, третья группа входов-выходов соединена с второй группой входов-выходов формирователя адресов, четвертая группа входов-выходов блока буферной памяти,.через блок 20согласования с четвертой группой входов-выходов блока сравнения, пятаягруппа входов-выходов блока буферной памяти соединена с первой группой входов-выходов блока ввода данных, шестая группа входов-выходов блока буферной памяти соединена с группойвходов-выходов блока сопряжения, первая группа управляющих входов-выходовкоторого подключена к третьей группевходов-выходов анализатора состояния,вторая группа входов-выходов которого подключена к второй группе управляющих входов-выходов блока сопряжения, вторая группа выходов блока ввода данных через генератор сигналовподключена к третьей группе входовформирователя адресов. Источники информации,принятые во внимание при экспертизе 1, Патент Франции М 2197483,кл. С 06 Г 3/04, опублик. 1979,2. Авторское свидетельство СССР У 570899, кл. С 06 Г 15/00, 1975

СмотретьЗаявка

2842111, 16.11.1979

ПРЕДПРИЯТИЕ ПЯ А-3517

ДАШКОВ ВЛАДИМИР АНДРЕЕВИЧ, ШВЫДКОВ АНАТОЛИЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 17/00

Метки: вычислительная

Опубликовано: 23.09.1982

Код ссылки

<a href="https://patents.su/5-960832-vychislitelnaya-sistema.html" target="_blank" rel="follow" title="База патентов СССР">Вычислительная система</a>

Предыдущий патент: Микропроцессорный модуль

Следующий патент: Устройство для вероятностного моделирования работы транспортных систем

Случайный патент: Уплотнение штока