Устройство для выполнения логических операций при решении дифференциальных уравнений

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 955081

Авторы: Головченко, Гузик, Евтеев, Крюков

Текст

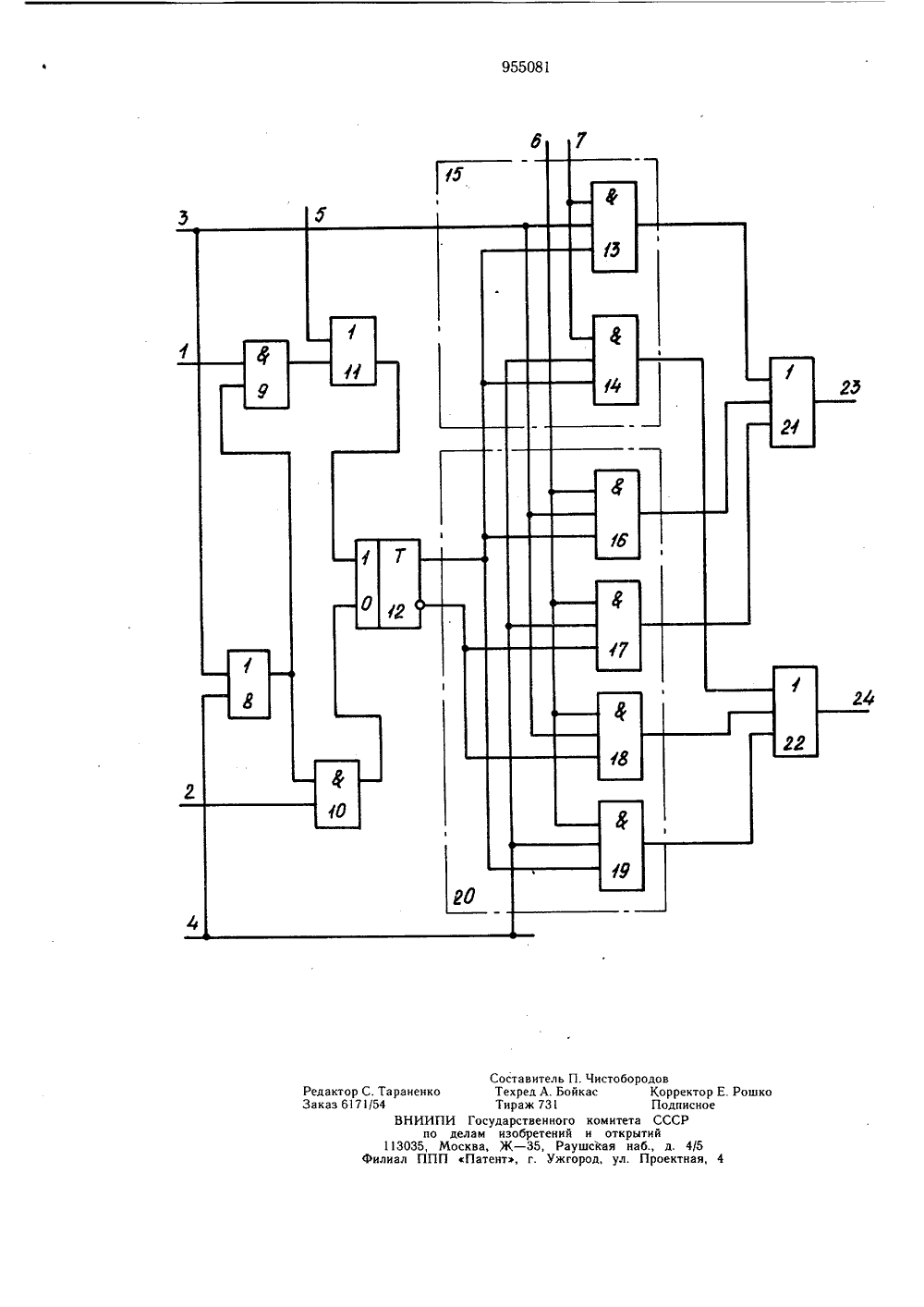

О П И С А Н И Е ( )955081ИЗОБРЕТЕНИЯ Союз СоветскихСоциалистическихРеспублик фл К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(51) М. Кл з б 06 Г 15/31 Гввудврственнме кемнтет пе лелем нзебретеннй и втврмтий(72) Авторы изобретения А. Н. Головченко, В. Ф. Гузик, Г. Н. Евтеев и . М. Крюков4 сТаганрогский радиотехнический институт им Д. КалмыковаВВЭР(54) УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ЛОГИЧЕСКИХ ОПЕРАЦИЙ ПРИ РЕШЕНИИ ДИФФЕРЕНЦИАЛЬНЫХ УРАВНЕНИЙИзобретение относится к вычислительной технике и предназначено для использования в цифровых интегрирующих машинах и структурах, оперирующих с одноразрядными приращениями с тернарным способом кодирования последних.Известен блок логических операций, содержащий узел накопления приращений, сумматор подынтегральной функции, узел управляющих импульсов и потенциалов, узлы выходных приращений и выработки и хранения поправки, экстраполятор и регистр кода операции 11.Недостатком этого блока является большой расход оборудования и невозможность применения его для выполнения логических операций при использовании в цифровых интегрирующих машинах и структурах одноразрядных приращений с тернарным спо; собом кодирования.Наиболее близким к изобретению техническим решением является устройство для выполнения логических операций, содержащее триггеры, схемы совпадения, схемы сборки, инверторы, причем шина выдачи приращений подынтегральной функции подсоединена к первым входам первой и второй схем совпадения и через инвертор - к первому входу третьей схемы совпадения, шина выдачи приращений независимой переменной подсоединена к вторым входам второй и третьей схем совладения и через инверторк второму входу первой схемы совпадения, выход первой схемы совпадения подсоединен к единичному входу первого триггера, выход третьей схемы совпадения - к его нулевому входу, выходы второй и третьей схем совпадения через схему сборки подключены к единичному входу второго триггера, нулевой вход которого соединен с выходом первой схемы совладения, единичный выход первого триггера подсоединен к третьему входу второй схемы совпадения, а единичный выход 5 второго триггера - через схему совпадения,первый и второй входы которой подключены соответственно к источнику синхронизирую- щего импульса знака и выходу схемы сборки команд условного и безусловного переходов, 2 в и схему сборки, второй выход которой подсоединен к выходу схемы совпадения, входы .которой связаны с источниками команд безусловного перехода, кода подынтегральной функции и синхронизирующего импульса знака, подключен к единичному входу третьУ 6+1) - квантованное значение подынтегральной функции;61 А 1 в функц ограничения;Ядп 1 Л 1 - функции знака.Выполнение логической функции знака осуществляется устройством следующим образом.По входу 6 из источника команд режимов подается разрешающий потенциал на элементы И 16 - 19 блока 20. Триггер 12 устанавливается в единичное состояние сигналом, поступающим на его единичный вход по входу 5 установки в исходное положение через элемент ИЛИ 11. Положительные значения подынтегральной функции поступают в устройство по входу 1 положительных значений независимо от знака приращений независимой переменной, которые, проходя через элемент ИЛИ 8, открывают элемент И 9, подтверждают единичное состояние триггера 12, который выдает разрешающий потенциал на элементы И 16 и 19 блока 20. Если приращения независимой переменной положительные, то они, проходя по входу 3 через элемент И 16 и элемент ИЛИ 21, поступают на выход 23 устройства, Если приращения независимой переменной отрицательные, то они, пройдя по входу 4 через элемент И 19 и элемент ИЛИ 22, поступят на выход 23 устройства. При отрицательном значении подынтегральной функции, поступающем на нулевой вход триггера 12 по входу 2 выдачи отрицательных значений подынтегральной функции з 0 через элемент И 1 О, независимо от знака приращений независимой переменной, триггер устанавливается в нулевое состояние и выдает разрешающий потенциал на элементы И 17 и 18 блока 20. Если приращения независимой переменной положительные, З 5 то они проходят по входу 3 через элемент И 18 и элемент ИЛИ 22 на выход 24 устройства. Если приращения независимой переменной отрицательные, то они проходят по входу 4 через элемент И 17 и элемент ИЛИ 21 на выход 23 устройства. Таким40 образом при отрицательном значении подынтегральной функции происходит переадресация независимой переменной с канала плюс (выход 23) на канал минус (выход 24). Если значение подынтегральной 45 функции станет равным нулю, триггер 12 запоминает предыдущее ее значение гр 1 и выдает разрешающий потенциал либо на элементы И 16 и 19 при положительном значении грг, либо на элементы И 17 и 1850 при отрицательном значении Ур 1.Выполнение логической операции ограничения осуществляется подачей из источника команд режимов разрешающего потенциала по входу 7 на входы элементов И 13 и 14 блока 15, Триггер 12 устанавли вается в единичное состояние сигналом по входу 5 через элемент ИЛИ 11. Положительные значения подынтегральной функции,поступающие в устройство по входу 1 через элементы И 9 и ИЛИ 11 на единичный вход триггера 12, независимо от знака приращений независимой переменной, которые через вход элемента ИЛИ 8 открывают элемент И 9, подтверждают единичное состояние триггера 12. Единичный потенциал с выхода триггера 12 поступает на входы элементов И 13 и 14 блока 15. Положительные или отрицательные значения независимой переменной передаются соответственно либо по входу 3 через элемент И 13 и элемент ИЛИ 21 на выход 23, либо по входу 4 через элемент И 14 и элемент ИЛИ 22 на выход 24 устройства. При отрицательном значении подынтегральной функции, поступающем в устройство по входу 2, триггер 12, независимо от знака приращений независимой переменной, открывающих через элемент ИЛИ 18 элемент И 10, устанавливается в нулевое состояние и приращения независимой переменной не пропускаются на выходы 23 и 24 устройства. При нулевом значении подынтегральной функции триггер 12 вспоминает предыдущее ее значение гр 1 и схема работает аналогично.Введение в устройство новых узлов и связей позволяет упростить его структуру и расширить функциональные возможности устройства с одновременным повышением точности выполняемых им логических операций за счет использования тернарной сис- . темы кодирования приращений. Сравнение затрат оборудования на реализацию прототипа и предлагаемого устройства показало, что при объеме вычислительного устройства цифровой интегрирующей структуры в 100 решающих блоков на реализацию прототипа потребуется 2900 переключательных элементов в базисе И-НЕ, а на реализацию предлагаемого устройства - 1400 переключательных элементов,Форму.га изобретения1. Устройство для выполнения логических операций при решении дифференциальных уравнений, содержащее первый и второй элементы И, первый элемент ИЛИ, триггер, вход установки которого соединен с выходом первого элемента ИЛИ, первый вход которого соединен с выходом первого элемента И, первый вход которого соединен с первым входом второго элемента И, выход которого соединен с входом сброса триггера, второй вход второго элемента И соединенс входом отрицательных значений подынтегральной функции устройства, второй вход первого элемента И соединен с входом положительных значений поды нтегральной функции устройства, отличающееся тем, что, с целью расширения функциональных возможностей за счет увеличения класса решаемых задач, в него введены второй элемент ИЛИ, блокформирования функции ограничения, блок формирования знака, третий и четвертый элементы ИЛИ, выходы которых являются положительным и отрицательным выходами устройства соответственно, первый вход третьего элемента ИЛИ подключен к первому выходу блока формирования функции ограничения, а второй и третий входы к первому и второму выходам блока формирования функции знака соответственно, второй выход блока формирования функции ограничения подключен к первому входу четвертого элемента ИЛИ, второй и третий входы которого соединены с третьим и четвертым выходами блока формирования функции знака соответственно, кодовые входы блока формирования функции знака и блока формирования функции ограничения под. ключены к первому и второму кодовым входам устройства соответственно, первый вход второго элемента ИЛИ соединен с входом положительных значений независимой переменной устройства, входом положительных данных блока функции ограничения и входом положительных данных блока формирования функции знака, второй вход второго элемента ИЛИ соединен с входом отрицательных значений независимой переменной устройства, входом отрицательных данных блока формирования функции ограничения и входом отрицательных данных блока формирования функции знака, второй вход первого элемента ИЛИ соединен с входом начальной установки устройства, прямой выход триггера соединен с входом режима блока формирования функции ограничения и первым входом режима блока формирования функции знака, второй вход режима которого подключен к инверсному выходу триггера.2. Устройство по п. 1. отличающееся тем, что блок формирования функции ограничения содержит первый и второй элементы И, первые выходы которых объединены и подключены к первому кодовому входу блока, вторые входы элементов И объединены и подключены к входу режимов блока, третий вход первого элемента И соединен с входом положительных данных блока, третий вход второго элемента И соединен с входом отрицательных данных блока.3, Устройство по п. 1, отличающееся тем, что блок формированя функции знака содержит четыре элемента И, первые входы которых объединены и подключены к кодовому входу блока, вторые входы первого и четвертого элементов И объединены и подключены к первому входу режима блока, вторые входы второго и третьего элементов И объединены и подключены к второму входу режима блока, третьи входы первого и третьего элементов И объединены и подключены к входу положительных данных блока, третьи входы второго и четвертого элементов И объединены и подключены к входу отрицательных данных блока.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССР415675, кл. 6 06 Г 7/00, 1974.2. Авторское свидетельство СССР213423, кл. б 06 Я 1/02, 1969 (прототип).Составитель П. Чистоо Техред А. БойкасТираж 73ПИ Государственного комито делам изобретений и отМосква, Ж - 35, РаушскаяП Патент, г. Ужгород, у Редактор С. Тараненк Заказ 6171/54 ВНИИ п 113035,Филиал ППбородовКорректор ЕПодписноеета СССРрытийна 6., д. 4/5Проектная, 4

СмотретьЗаявка

2943128, 19.06.1980

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

ГОЛОВЧЕНКО АЛЬБЕРТ НИКОЛАЕВИЧ, ГУЗИК ВЯЧЕСЛАВ ФИЛИППОВИЧ, ЕВТЕЕВ ГЕННАДИЙ НИКОЛАЕВИЧ, КРЮКОВ РУДОЛЬФ МИХАЙЛОВИЧ

МПК / Метки

МПК: G06F 17/10, G06F 17/13

Метки: выполнения, дифференциальных, логических, операций, решении, уравнений

Опубликовано: 30.08.1982

Код ссылки

<a href="https://patents.su/5-955081-ustrojjstvo-dlya-vypolneniya-logicheskikh-operacijj-pri-reshenii-differencialnykh-uravnenijj.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для выполнения логических операций при решении дифференциальных уравнений</a>

Предыдущий патент: Устройство для моделирования конечных автоматов

Следующий патент: Цифровой функциональный преобразователь

Случайный патент: Флюс для автоматической сварки