Параллельно-последовательный аналого-цифровой преобразователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 940295

Автор: Чепалов

Текст

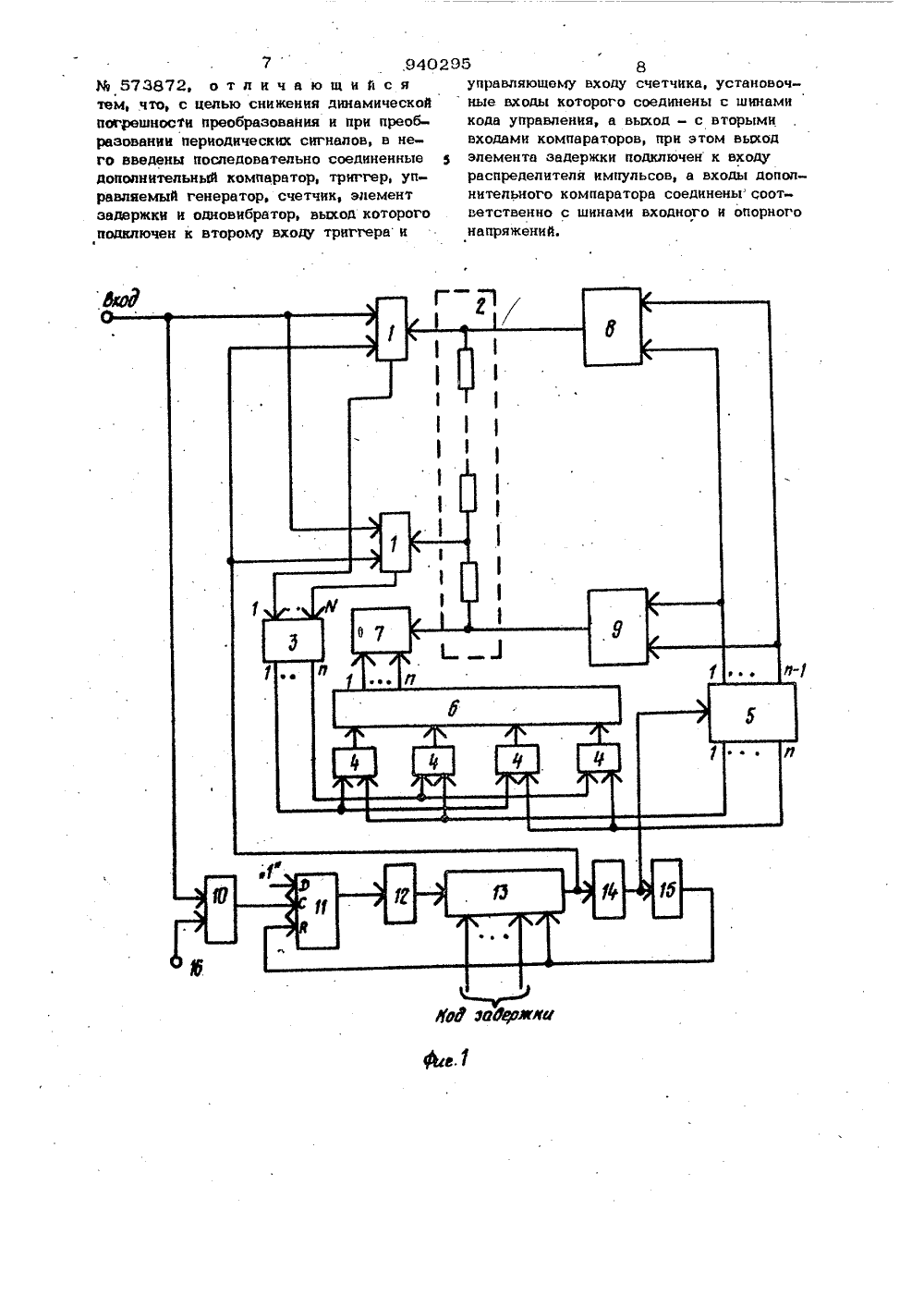

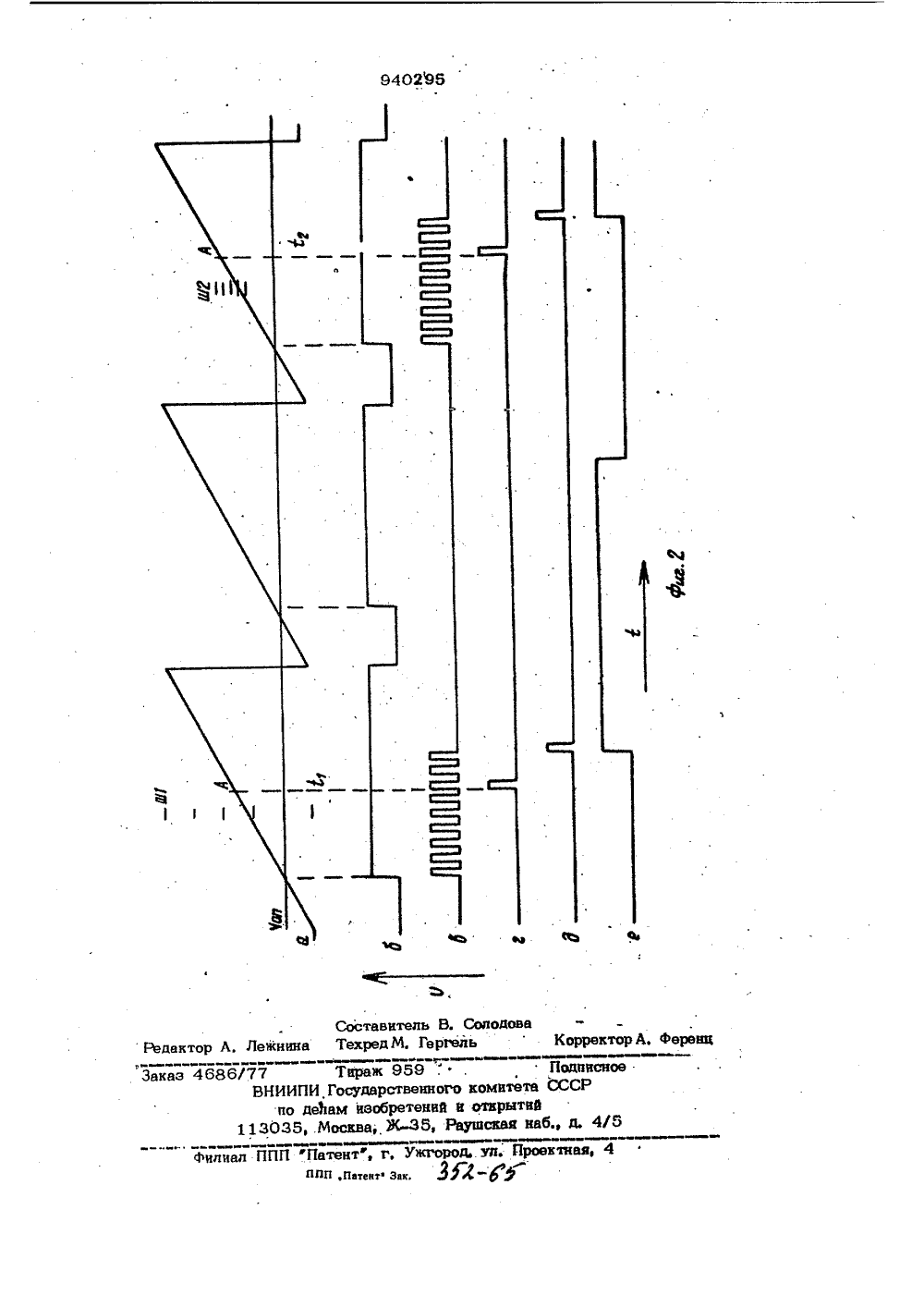

ОП ИСАНИЕ ИЗОБРЕТЕНИЯ К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(088.8 Опубликовано 30,06.82, оюллетень М 24 Дата опубликования описания 30,06.82(54) ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ АНАЛОГО-ЦИФРОВОЙ ПРЕОБРАЗОВАТЕЛЬ 1Изобретение относится к аналого-цкф ровой вычислительной и измерительной технике и можетбыть использовано при автоматическом измерении широкополооных периодических сигналов.5По основному авт, св. М 573872 известен параллельно-последовательный аналого-цифровой преобразователь, содержащий компараторы, выходы которых цодключены к входам шифратора, соединенным10 с первыми входами элементов И, вторые входы которых подключены к распредели телю импульсов, делитель напряжения, включенный между оатими входами компа 1 раторов и выходамн управляемого генератора тока, регистр, подключенный к выходам элементов И, цифро-аналоговый преобразователь, соединенный с выходом регистра, и дополнительный управляемый генератор тока, входы которога подключены к выходам распределителя импуль сов, а выход - к нижнему зажиму делителя напряженИя. 2Преобразование входного напряженияосуществляется в несколько тактов, причем в каждом такте определяется несколько разрядов вьтхотаого кода, Благодаря наличйю двух управляемых генераторов тока в преобразователе получено повышен ное быстродействие и высокая точность.Недостатком указанного устройства является большая величина динамическойпогрешности нреобраэования, определяемаяизменением входного ситчтала за время преобразования, Динамическая погрешносФьопределяется по формуле А Я т, пР, где8 - скорОсть, изменения входного ситяалаа т,пР время преобразования преобраэова теля,Время преобразования преобразователя имеет значительную величину, пмзопьку преобразование осутцествляется в несколько тактов, которые непрерывно следуют друт за другом.Цель изобретения - уменьшение дина мической и м решности преобраэования ипри преобразовании периодических секулов.Укаэанная цель достигается тем, чтов параллельно-последовательный аналогоцкфровой преобразователь введены последовательно соединенные дополнительныйкомпаратор, триггер, управляемый генератор, счетчик элемент задержки иоднооибратор выход которого подключенк второму входу триггера и управляюше Ому входу счетчнка, установочные входыкоторого соединены с шинами кода управ ленияа выход - с вторыми входами компараторов, при этом выход элемента задержки подключен к входу распределите 4.ля импульсов, а входы дополнительногокомпаратора соединены соответственнос шинами входного и опорного напряжений,Техническая сущность предлагаемогоустройства заключается в снижении динамической погрешности преобразования засчет того, что разные такты преобразовання осуществляются и разных периодахвходного сигналц,Компараторы в предлагаемом устройстве имеют дополнительный вход опроса.Прк этом компаратор изменяет свое состояние только прн наличии импульса по входу опроса, таким образом можно зафиксировать состояние компаратора в определенный момент времени т.е. п 1)оизвес-.ти сравнение в определенной точке преобразуемого сигнала,На фиг. 1 изображена функциональнаясхема предлагаемого преобразователя;на фиг. 2 - временные диаграммы,35Преобразователь содержит ч компараторов 1, делитель 2 напряжения шифратор 3,элементы И 4, распределитель 5 нмпульсов, регистр 6, цифро-аналоговый преоб 40раэователь ( ЦАП) 7, управляемые генераторы 8 и 9 тока, дополнительный компаратор 10, триггер 11, управляемыйгенератор 12, счетчик 13, элемент 14задержки одновибратор 15, вход 16опорного напряжения (цепи начальной ус 45тановкн регистра 6, распределителя 5импульсов, счетчика 13, триггера 11условно не показаны).В исходном состояннн триггеры регистра 6 находятся в состоянии "0", соответственно, и выходное напряжение ЦАП7 тоже равно нулю, Генераторы 8 и 9тока вырабатывают максимальные по величине токи, причем последние равнымежду собой и противоположны по направлению, Под воздействием токов генераторов 8 и 9, протекающих через делитель2, пороги срабатывания компараторов 1 устанавливаются такими, что весь диапазон изменения входной величины оказывается разбитым на 2 зон; где Ичксло параллельно определяемьи двоичньиразрядов. Пороги срабатывания компараторов при этом образуют шкалу Ш 1(фиг, 2 а).При превышении периодическим входным сигналом (фиг. 2 а) опорного уровнясинхронизации Уопна выходе дополнительного компаратора 10 формируется импульсный сигнал (фиг, 2 б), поступающий на динамический вход С 9- триггера 11. Навход 1)-триггера постоянно подаетсяуровень логической " 1". При поступлениина вход С переднего фронта сигнала(фиг. 2 б), на выходе триггера 1 1 устанавливается уровень логической "1 которымзапускается управляемый генератор 12,на выходе которого формируется последовательность импульсов (фиг. 2 в),В счетчик 13 предварительно заносится код задержки величина которого определяет задержку момента преобразованиявходного сигнала относительно моментапревышения входным сигналом опорногоуровня, Код задержки подается на установочные входы счетчика 13 постоянно,а его запись в него осуществляется импульсом, поступающим на вход занесениясчетчика,При поступлении на счетный входсчетчика 13 (М-к)-го импульса с управляемого генератора 12 (где М- полная ем-,кость счетчика 13; к - предварительнозанесенный код) на вьиоде счетчика 13формируется импульс переполнения (фиг,2 г),поступающий на входы опроса компараторов 1 и на вход элемента 14 задерж-.ки, В результате по импульсу (фиг. 2 г)в момент времени 1 происходит сравнение сигнала (фиг. 2 а) со шкалой Ш 1,компараторамн 1 фиксируется единичныйкод, который шифратором 3 преобразуется в двоичный код старших разрядов выходного кода,С выхода элемента 14 задержки задержанный импульс (фиг. 28) поступает на вход распределителя 5 импульсов н вход одновибратора 15. При поступлении на вход импульса (фиг, 2 Э) распределитель 5 импульсов выдает по первым выходам импульсы, которыми через элемент И 4 заносятся в регистр 6 код старших разрядов и переключаются токи управляемьи генераторов 8 и 9 тока. Токк генераторов 8 и 9 тока уменьшаются в Й+ 1 раз, вследствие чего падение напряжения на5 9402 резисторах делителя 2 уменьшается во столько же раэ, Поскольку в регистр 6 занесен код старших разрядов, на выходе ЦАП 7 устанавливается напряжение, соответствующее коду старших разрядов. 5 После окончания переходных процессов,ьвызванных переключениями, пороги срабатывания компараторов 1 образуют шкалу Ш 2 (фиг, 2 а) лля определения младших разрядов выходного кода. Элемент О 14 задержки необходим для того, чтобы занесение информации в регистр 6 через элементы И ) происходило после установления информации на выходе шифратора 3, т.е. лля компенсации задержки в цепях 1% компараторов 1 и шифратора 3.При поступлении импульса (фиг.23) с выхода элемента 14 задержки одновиб-ратор 15 формирует импульс (фиг.26), постуйающи, на вход КВ-триггера 11. длительность импульса олновибратора 1 5 выбирается ".акой, чтобы она была больше времени установления шкалы Ш 2, которое определяется временем переключения управляемых генераторов 8 и 9 тока и временем установления выходного напряжения ЦАП 7, Импульс (фиг.20), присутствующий на входе с 3-триггера 11, устанавливает на его выходе уровень логического "0, в результате чего прекра- Зй щается генерация импульсов генераторов 12 (фиг,26), и импульсом, поступающим на вход занесения счетчика 13 с выхода одновкбратора 15, в счетчик 13 вновь заносится код задержки. Кроме того, импульсом (фиг;28) триггер 11 блокируется, т,е. во время действия импульса триггер 11 не реагирует на поступление им-. пульсов (фиг.2) на динамический вход С, и уровень 0 на входе управляемого генератора остается неизменным, Наличие блокировки запуска триггера 11 обеспечивает определение младших разрядов выходного кода только после того, как окончатся переходные процессы установ-" ления шкалы Ш 2.1 Из фиг,2 следует, что при периоде повторения входного сигнала, (фиг,20) меньше длительности импульса (фиг.28) (т,еесли время установления шкалы Ш 2 больше периода следования входного преобразуемого сигнала), очередной импульс входного сигнала пропускается и определение младших разрядов производится в третьем по счету периоде входното сигнала,Я Этим обеспечивается защкта преобразователя от сбоев, которые могу гзозникнуть при высокой частоте повторения входного сигнала и Привести к существеюой ошибке в определении результирующего кода.После окончания импульса (фиг.2) преобразователь снова готов к следующему такту прообраэования, .который проте кает аналогично первому, при этом. производят сравнение напряжения точки А в момент времени Ъ со шкалой Ш 2 и определение младших разрядов выходного кода. В общем случае тактов преобразования может быть несколькэ, их количество определяется разрядностью выходного кода и числом Й,сомпараторов. Роль распределителя 5 ийпульсов при этом сводится к тому, что прн поступлении первого импульса с выхода элемента 14 задержки он формирует управляющие импульсы по первым выходам, при поступлении второго импульса формируются управляющие импульсы по вторым выходам и так лалее. Последним управляОщим импульсОм заносится . код младших разрядов и триггеры младших разрядов регистра 6, которые нв связаны с цифро-аналоговым преобразователем 7 (число разрядов ПАП 7 на И меньше числа разрядов регистра 6), Управляемые генераторы 8 и 9 тока при этом но коммутируются, поскольку п последнем такте нет необходимости формирования слелующей шкалы.Таким образом, благодаря введению дополнительного компаратора, триггера,;. управляемого генератора, счетчика, элемента залержки и олновибратора реализуется стробоскопический режим работы аналоге-цифрового преобразователя, при котором опрос компараторов, т.е. фиксацияединичного кода компараторов, прокзводится всегда в одной и той же точке периодического сигнала (точка А ка фиг.2 я).Изменение состояний 11 АП и генераторовтока производится в теченке времени между двумя импульсами опроса, поэтомувремя установленкя 0 АП и управляемыхгенераторов тока не вносит вклада вдинамическую погрешность преобразования. Оинамическая погрешность преобраэьвания мгновенного значения сигнала практически определяется только апертурнойпогрешностью компараторов. Благодаряналичию блокировки запуска преобразователя импульсом одновкбратора можно использовать менее быстролействующие,зато более простые и более точные цифро-аналоговый преобразователь и управляемые генераторы тока,формула и э о б р е т е н к яПараллельно-последовательный аналого-цкфровой преобразователь по авт, св.7.9402958Ж 573872, о т л и ч а ю щ и й с я управляющему входу счетчика, установочтем, что, с целью снижения динамическойные входы которого соединены с шинами погрешности преобразования и при преоб- кода управления, а выход - с вторыми разовании периодических сигналов, в не- входами компараторов, при этом выход го введены последовательно соединенные В элемента задержки подключен к входу дополнительный компаратор, триггер, уп- распределителя импульсов, а входы дополравляемый генератор, счетчик, элемент нительного компаратора соединенысоотзадержки и одновибратор, выход которого ветственно с шинами входного и опорного подключен к второму входу триггера и напряжений.Фил Составитель В. СолодоваРедактор Л, Лежнина Техред М, ГергельКорректорвВВФЕВиЮЮВе ВВВеВВВае ююВВвЗаказ 4686/77 Тираж 959ПоднисноеВНИИПИ, Государственного комитета СССРпо делам изобретений и открытий113035,.Москва, Ж 35, Раушснан наб., д. 4/5юлаевиал ППП "Патенте, г, Ужгород,.ул. Йроектнанв 4ППП,Патент Эвк. ЗО У А. ференц

СмотретьЗаявка

3220448, 22.12.1980

ПРЕДПРИЯТИЕ ПЯ М-5783

ЧЕПАЛОВ ВЛАДИМИР КОНСТАНТИНОВИЧ

МПК / Метки

МПК: H03K 13/08

Метки: аналого-цифровой, параллельно-последовательный

Опубликовано: 30.06.1982

Код ссылки

<a href="https://patents.su/5-940295-parallelno-posledovatelnyjj-analogo-cifrovojj-preobrazovatel.html" target="_blank" rel="follow" title="База патентов СССР">Параллельно-последовательный аналого-цифровой преобразователь</a>

Предыдущий патент: Способ преобразования кода в постоянный сигнал

Следующий патент: Аналого-цифровой преобразователь с автоматической коррекцией

Случайный патент: Роторный автомат питания