Цифроаналоговый микропроцессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 881760

Автор: Аристов

Текст

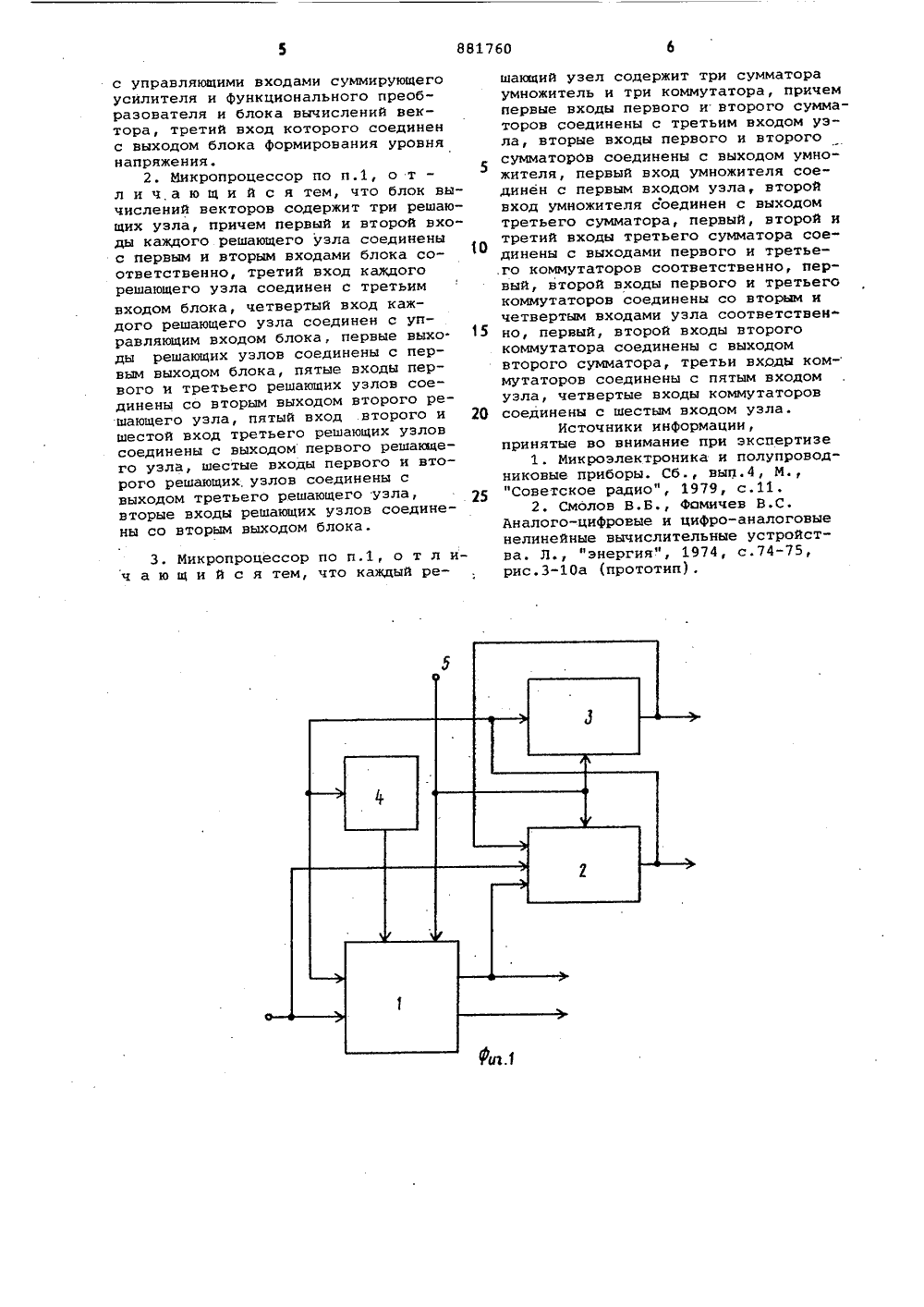

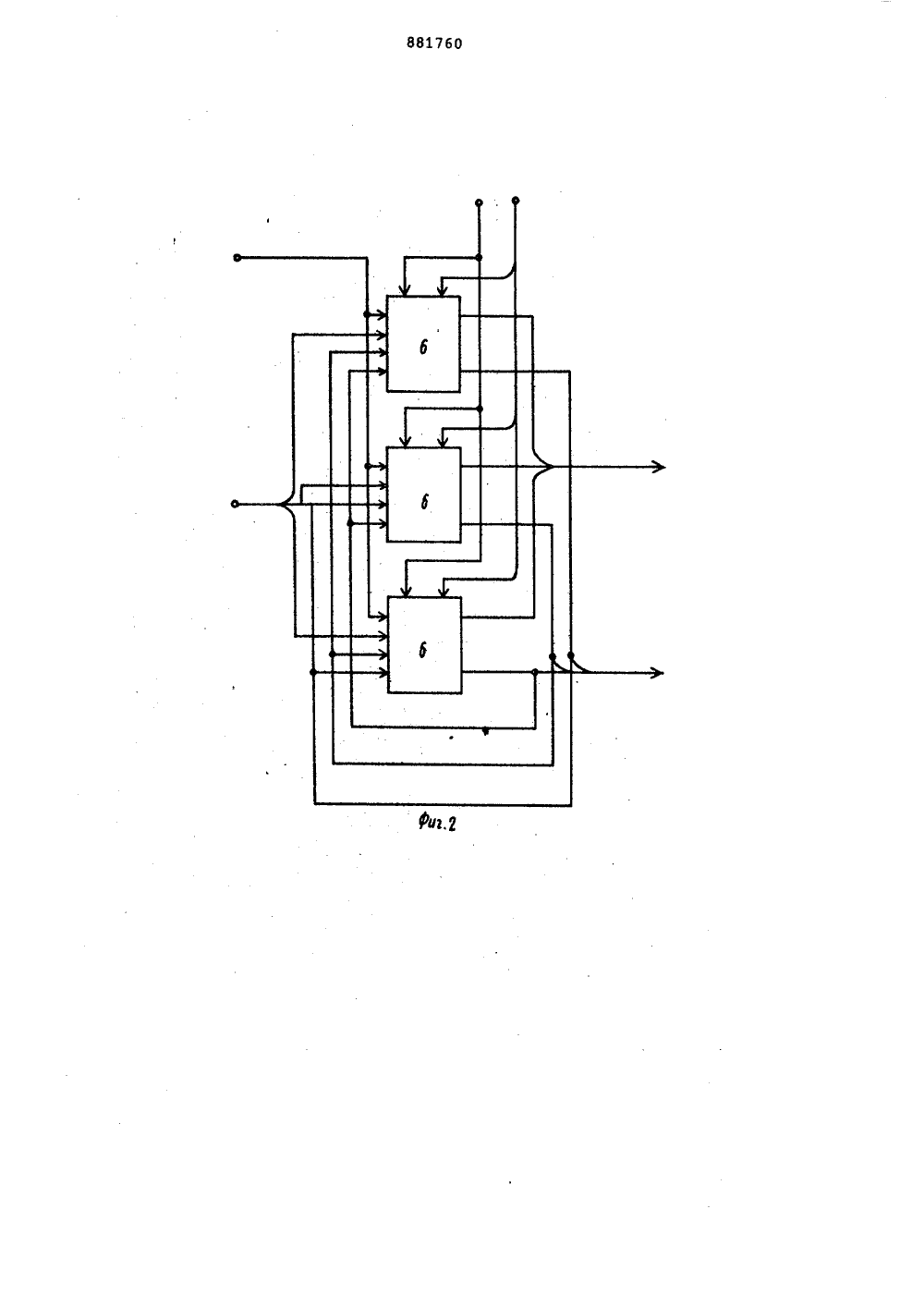

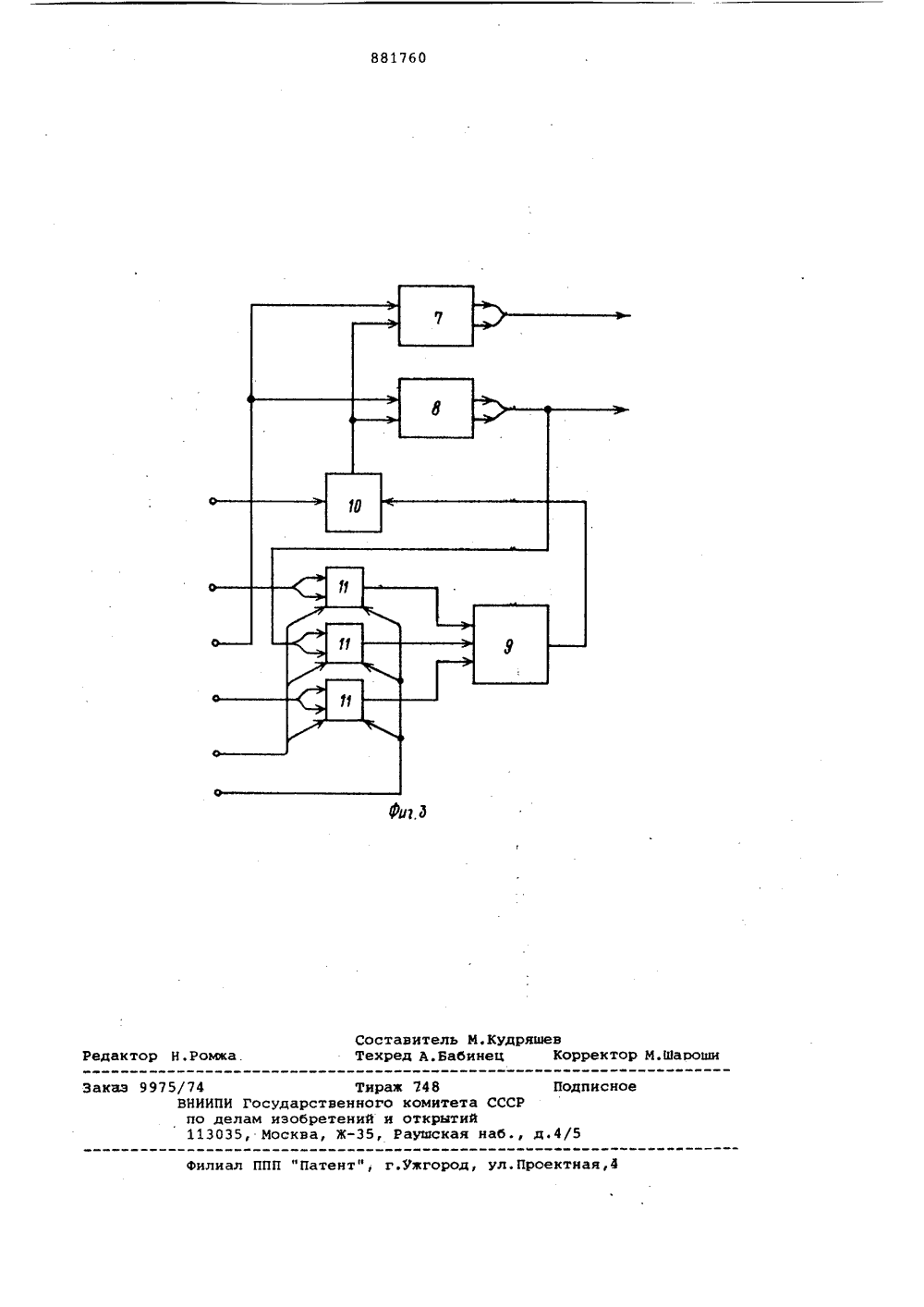

Союз Советских Социалистических РеспубликОПИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 881760(22) Заявлено 250280 (2) 2887481/18-24с присоединением заявки Ио -(51) М. Кл. С 06 Г 15/32 Государственный комитет СССР но делам изобретений и открытий(72) Автор изобретения В.В.Аристов Институт электродинамики АН Украинской СОР(54).ЦИФРОАНАЛОГОВЫЙ МИКРОПРОЦЕССОР Изобретение относится к вычислительной технике и может быть исполь 1зовано в цифроаналоговых вычислительных и моделирующих системах.Известны цифровые микропроцессорысостоящие из цифровых, коммутирующих,запоминающих и арифметикологическихблоков и позволяющие эа счет микропрограммирования формировать широкий 0набор логических и вычислительныхФункций 11,Основным недостатком цифровых микропроцессоров эа счет последовательного принципа Функционирования является малое быстродействие при вычис- Зленни сложных Функций, например отмногих переменных. Наиболее близким по технической сущности и достигаемому результату к иЗобретению является цифроаналоговое устройство, содержащее управляющий регистр, набор вычислительных и функциональных блоков, коммутатор входов, коммутатор выходов и комму татор соединений блоков 12.Однако такому устройству присущ большой объем оборудования.Цель. изобретения - сокращение оборудования. 30 Поставленная цель достигается тем, ;что в цифроаналоговый микропроцессорф, содержащий функциональный преобразователь и блок вычислений вектора, допол" нительно введены суммирующий усилитель и блок формирования уровня напряжения, причем первый вход микропроцессора соединен с первыми входами блока вычислений вектора и суммирующего усилителя, первый и второй выходы блока вычислений вектора являются соответственно первым и вторым выходами микропроцессорач третий выход которого соединен с выходом сум мирующего усилителя, со вторыми входами функционального преобразователя и блока вычислений вектора и с входом блока формирования уровня напряжения первый выход блока вычислений Вектора соединен со вторым входом суммирующего усилителя, третий вход которого соединен с выходом функционального преобразователя и четвертым выходом микропроцессора,. второй вход которого соедйнен с управляющими входами суммирующего усилителя и функционального преобразователя и блока вычислений вектора, третий вход которого соединен с выходом блока формирования уровня напряжения.Кроме того, блок вычислений вектора содержит три решающих узла, причем первый и второй входы каждого решающего узла соединены с первым и вторым входами блока сбответственно, третий вход каждого решающего узла соединен с третьим входом блока,. четвертый вход каждого решающегоузла соединен с управляющим входомблока, первые выходы решающих узловсоединены с первым выходом блока,пятые входы первого и третьего решающих узлов соединены со вторым выходом второго решающего узла, пятыйвход второго и шестой вход третьегорешающих узлов соединены с выходомпервоГо решающего узла, шестые входыпервого и второго решающих узлов соединены с выходом третьего рещающегоузла, вторые выходы решающих узловсоединены со вторым выходом блока,Каждый решающий узел содержит три 20сумматора, умножитель, три коммутатора, причем первые входы первогои второго сумматоров соединены с третьим входом узла, вторые входы первого и второго сумматоров соединены 25с выходом умножителя, первый входумножителя соединен с первым входомузла, второй вход умножителя соединен с выходом третьего сумматора,первый, второй и третий входы третьего сумматора соединены с выходамипервого и третьего коммутаторов соответственно, первый, второй входыпервого и третьего коммутаторов соединены со вторым и четвертым входамиузла соответственно, первый, второйвходы второго коммутатора соединеныс выходом второго сумматора, третьивходы коммутаторов соединены с пятымвходом узла, четвертые входы коммутаторов соединены с шестым входом узла,На фиг.1 изображена блок-схемапредлагаемого цифроаналогового микропроцессора; на фиг.2 - блок-схемавычислений вектора; на фиг.3 - Функциональная схема решающего узла блокавычислений вектора.Устройство содержит блок 1 вычислений вектора, суммирующий усилитель2, функциональный преобразователь 3и блок 4 формирования уровня напряжения, вход 5 микропроцессора.Блок вычислений вектора 1 содержитрешающие блоки б, которые содержаттри сумматора 7-9, узел умножения 10и ти коммутатора 11,Последовательность работы устройства состоит в задании кода операцийв виде комбинаций высоких и низкихуровней напряжения по входу 5, задании в виде напряжений на первый и вто рой входы устройства соответственнозначений переменных, являющихся компонентами вектора, и съем результатов в виде напряжений, формируемыхна всех четырех выходах устройства, 65 Код операций характеризуется значениями а ад, амм д" м 57 к, 9 н бхайгде а; и; - компоненты матриц А и 8 соответственно.Код операций задается на входы узлов б блока 1, блока 2 и функционального преобразователя 3. В зависимости от кода коммутатор 11 решающего узла б запрещает или разрешает прохождение прямого или инверсного сигнала со входа или второго выхода блока 1 на соответствующий вход сумматора 9, Сигнал в виде уровня напряжения, подаваемый с выхода блока 4 на четвертые входы всех коммутаторов 11, одновременно инвертирует напряжение на всех входах сумматоров 9 решающих узлов б.Составляющие кода операций, поступая на входы блока 2, разрешают или блокируют прохождение напряжения через блок 2, обуславливая тем самым наличие или отсутствие информационных связей в блоке 2. Кроме того, часть кода операций поступает на управляющий вход функционального преобразователя 3, поэтому на выходе преобразователя 3 в зависимости от этого кода формируется напряжение, изменяющееся по закону ЬИ.Этот базовый вариант только двух функций от одной переменной позволяет формировать множество, исчисляемое сотнями и более иных нелинейных функций, в том числе и от многих переменных.Применение изобретения позволяет сократить объем оборудования.Формула изобретения1. Лифроаналоговый микропроцессор, содержащий Функциональный преобразователь и блок вычислений вектора, о т л и ч а ю щ и й с я тем, что, с целью сокращения оборудования, он содержит суммирующий усилитель и блок формирования уровня напряжения, причем первый вход микропроцессора соединен с первыми входами блока вычислений вектора и суммирующего усилителя, выходы блока вычислений вектора являются соответственно первым и вторым выходами микропроцессора, третий выход микропроцессора соединен с выходом суммирующего усилителя, со вторыми входами функционального преобразователя и блока вычислений вектора и с входом блока формирования уровня напряжения, первый выход блока вычислений вектора соединен со вторым входом суммирующего усилителя, третий вход которого соединен с выходом функционального преобразователя и четвертым выходом микропроцессора, второй входмикропроцессора соединенс управляющими входами суммирующего усилителя и функционального преобразователя и блока вычислений вектора, третий вход которого соединен с выходом блока формирования уровня напряжения.52. Микропроцессор по п.1, о т л и ч а ю щ и й с я тем, что блок вычислений векторов содержит три решающих узла, причем первый и второй входы каждого решающего узла соединены с первым и вторым входами блока соответственно, третий вход каждого решающего узла соединен с третьим входом блока, четвертый вход каждого решающего узла соединен с управляющим входом блока, первые выхо 15 ды решающих узлов соединены с первым выходом блока, пятые входы первого и третьего решающих узлов соединены со вторым выходом второго решающего узла, пятый вход второго и 20 шестой вход третьего решающих узлов соединены с выходомпервого решающего узла, шестые входы первого и второго решающих узлов соединены свыходом третьего решающего узла, д вторые входы решающих узлов соединены со вторым выходом блока. 3. Микропроцессор по п.1, о т л ич а ю щ и й с я тем, что каждый решающий узел содержит три сумматораумножитель и три коммутатора, причемпервые входы первого и второго сумматоров соединены с третьим входом узла, вторые входы первого и второгосумматоров соединены с выходом умножителя, первый вход умножителя соединен с первым входом узла, второйвход умножителя соединен с выходомтретьего сумматора, первый, второй итретий входы третьего сумматора соединены с выходами первого и третьего коммутаторов соответственно, первый, второй входы первого и третьегокоммутаторов соединены со вторым ичетвертым входами узла соответственно, первый, второй входы второгокоммутатора соединены с выходомвторого сумматора, третьи входы коммутаторов соединены с пятым входомузла, четвертые входы коммутаторовсоединены с шестым входом узла.Источники информации,принятые во внимание при экспертизе1. Микроэлектроника и полупроводниковые приборы. Сб., вып.4, М.,881760 оставитель М.Кудряшевехред А.Бабинец Корректор М.Шаро Редактор Н,Ро Подписно филиал ППП "Патент", г.Узгород, ул.Проектна каэ 9 97 5/74 Тир ВНИИПИ Государственног по делам изобретений 113035, Москва, Ж,748комитета СССРоткрытийаушская наб., д.4/5

СмотретьЗаявка

2887481, 25.02.1980

ИНСТИТУТ ЭЛЕКТРОДИНАМИКИ АН УССР

АРИСТОВ ВАСИЛИЙ ВАСИЛЬЕВИЧ

МПК / Метки

МПК: G06F 17/16

Метки: микропроцессор, цифроаналоговый

Опубликовано: 15.11.1981

Код ссылки

<a href="https://patents.su/5-881760-cifroanalogovyjj-mikroprocessor.html" target="_blank" rel="follow" title="База патентов СССР">Цифроаналоговый микропроцессор</a>

Предыдущий патент: Устройство для статистического моделирования вероятностного графа

Следующий патент: Устройство для вычисления коэффициентов разложения функции в ряд

Случайный патент: Преобразователь угол — фаза — код