Устройство для исправления ошибокв системе остаточных классов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

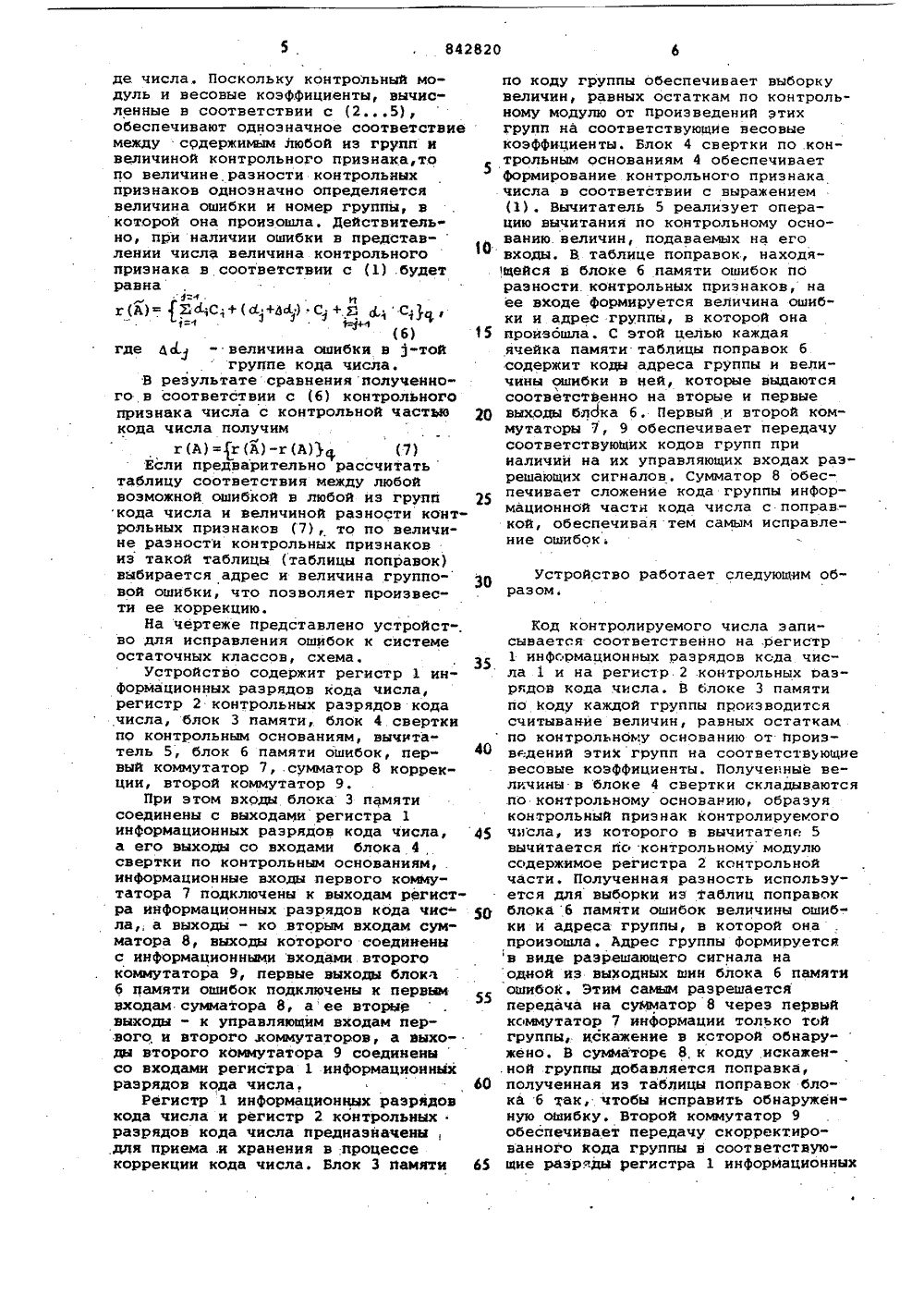

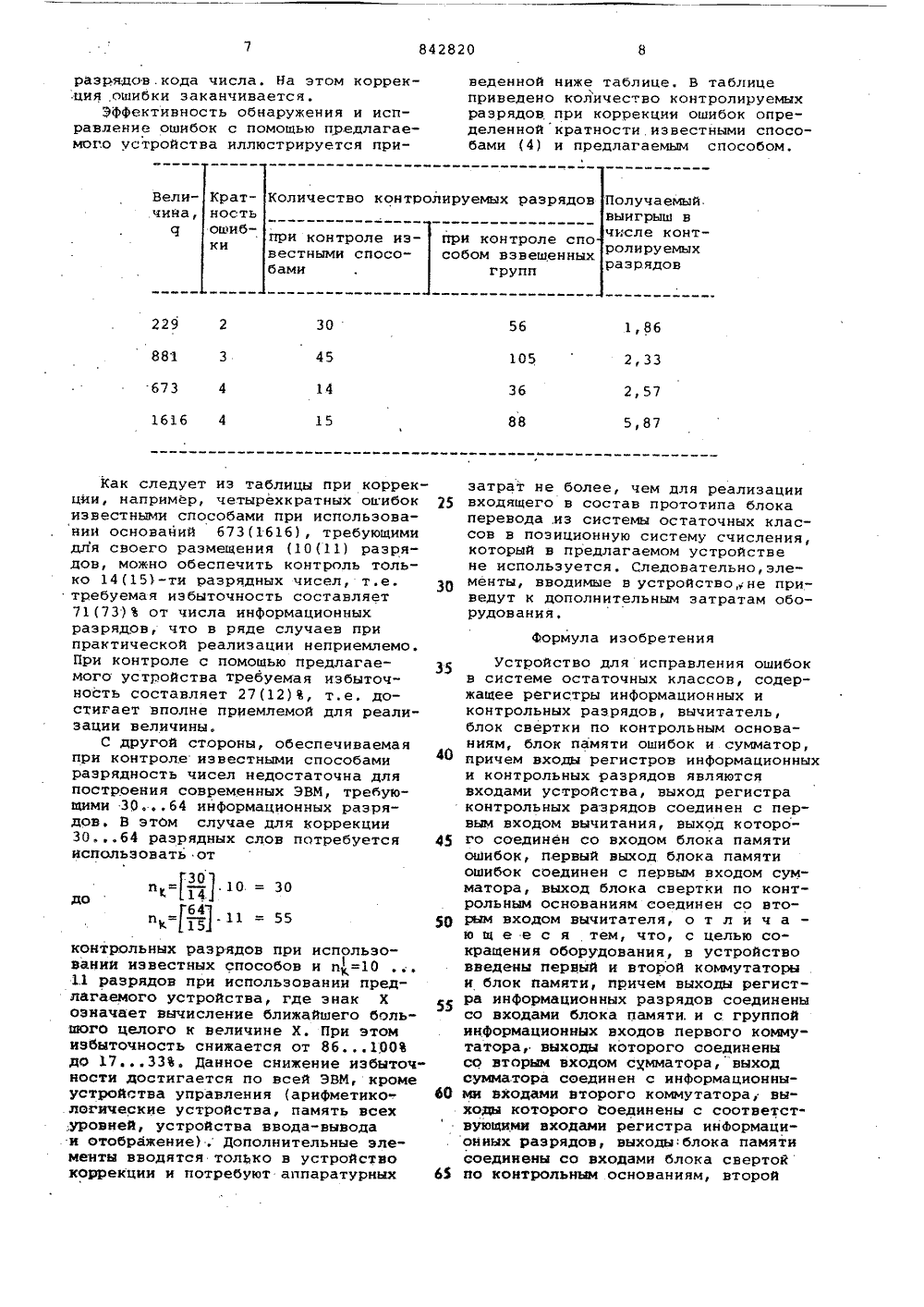

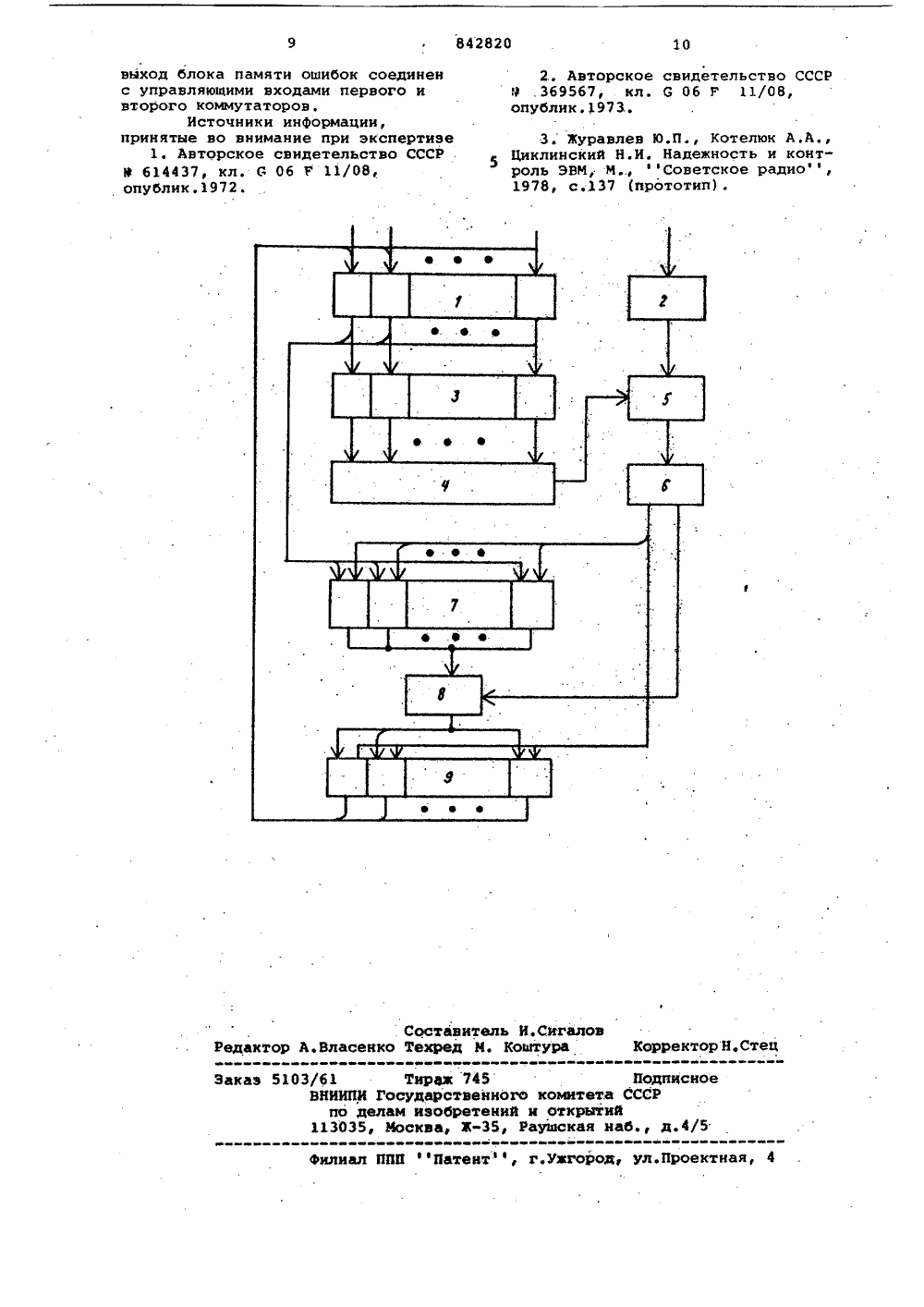

ОП ИСАНИЕИЗОБРЕТЕНИЯК АВТОРСКОМУ СВИДИТИЛЪСТВУ Союз Советских Социалистических Республик(51)М, Кл,з С 06 Р 11/08 с присоединением заявки йо(23) Приоритет Государственный комитет СССР по делам изобретений и открытий(72) Авторы изобретения В.С.Василенко и С.И.Григорьев 1) Заявите 54) УСТРОЙСТВО ДЛЯ ИСПРАВЛЕНИЯ ОШИБОК В СИСТЕМЕ ОСТАТОЧНЫХ КЛАССОВ 5 О Изобретение относится к вычислительной технике и используется в цифровых ЭВМ повышенной информационной надежности.Известно устройство для исправления ошибок, содержащее регистр Приемных элементов, дешифратор, группы элементов И и ИЛИ, элемент фиксации окончания приема кодовых комбинаций, элемент запрета и элемент ИЛИ, В, этом устройстве обеспечивается обнаружение и исправление. одиночных ошибок в коде числа 1).Недостатком этого устройства является невозможность коррекции ошибок кратности большей единицы.Известно устройство для исправления ошибок в системе остаточных . классов, содержащее операционный и запоминающий регистр с и выходами, блоки памяти констант нулевизации, дешифраторы, блоки памяти констант нулевизации и ошибок, сумматор, переключатели и логические элементы (2).Недостатком устройства является низкое быстродействие,и большие за" траты оборудования.Наиболее близким техническим решением к предлагаемому изобретению является устройство, которое содержит регистр инФормационной и регистр контрольной части кода числа, узел свертки по контрольным основаниям, узел перевода СОК -ПСС, вычитатель, таблицу поправок н сумматор, выходы регистра контрольной части числа подсоединены к первым входам вычйтателя, ко вторым входам которого подсоединены выходы узла свертки по контрольным основаниям, выходы вы-читателя подсоединены ко входам таблицы поправок, выходы регистра информационной части числа через узел перевода .СОК".ПСС подсоединены ко входам узла свертки по контрольным основаниям и первым входам сумматора коррекции, ко вторым входам которого подсоединены выходы таблицы поправок .33 .При контроле.и исправлении ошибок на регистрызаписывается информационная и контрольная части кода числа соответственно. В устройстве перевода от системы остаточных классов в позиционную систему счисления осуществляется преобразование информационнбй части кода числа иэ системы остаточных классов в одну йз позиционных систем, что дает возможность сформировать в узле свертки контрольный признак, который в вычитателесравнивается с контрольной частьюкода числа, Наличие между ними разницы свидетельствует об ошибке впредставлении кода числа, величинаи адрес которой определяются в таблице поправок. Полученная поправкав сумматоре складывается с информационной частью кода числа, тем самымвыполняется коррекция искаженногочисла.Недостатком известного устройстваявляются значительные затраты.оборудования в ЭВМ, используемого дляхранения и обработки контрольнойчасти кода числа.Цель изобретения - сокращение 15оборудования в ЭВМ, используемогодля хранения и обработки контрольной части кода числа,Поставленная цель достигаетсятем, что в устройство для исправления ошибок в системе остаточныхклассов, содержащее регистры информационных и контрольных разрядов,вычитатель, блок свертки по контрольным основаниям, блок памяти 25ошибок и сумматор, причем входырегистров информационных и контроль"ных разрядов являются входами устройства, выход регистра контрольныхразрядов соединен с первым входом ЗОвычитателя, выход которого соединенсо входом блока памяти ошибок, первый выход блока памяти ошибок соединен с первым входом сумматора, выходблока свертки по контрольным основаниям соединен со вторым входом вычитателя введены первый и второй коммутаторы и блок памяти, причем выходы регистра информационных разрядовсоединен со входами блока памяти ис группой информационных входов первого коммутатора, выходы которогосоединены со вторым входом сумматора,выход сумматора соединен с информационными входами второго коммутатора,выходы которого соединены с соответствующими входами регистра .информациенных разрядов, выходы блока памятисоединены со входами блока свертокпо контрольным основаниям, второйвыход блока памяти ошибок соединен с ууправляющими входами первого ивторого коммутаторов.Устройство для исправления ошибокв системе остаточных классов реализует способ обнаружения ошибок, которыйзаключается в следующем.ИнФормационная часть кода числасопровождается, как и при известныхспособах контроля по модулю, коитрольным признаком. В отличие от известных способов, контроЛьный признак еОполучается следующим образом, информационная часть кода числа разбивается на Фиксированные группы определеиной разрядности. Разрядностьгрупп определяет кратность обнаружи- И ваемых и исправляемых ошибок. Кодгруппы, рассматриваемый как некоторое число с(, умножается на соответствующий вес С . От суммыполученных произведений вычисляетсяостаток (остатки) по контрольноМумодулю (модулям) в соответствии свыражениемг (И = ЕС, (1)где п - число койтрольных группинформационной части кодачисла;контрольный модуль,х, - знак, обозначающий вычисление остатка величины хпо модулю а,В качестве весовых коэффициентовС берутся числа, удовлетворяющиеприведенному ниже выражению (4).Величина контрольного модуля выбирается из следующих условий. Вопервых, для обеспечения однозначногосоответствия между величиной ошибкипредставления и контрольным признаком операнда (1), необходимо чтобывеличина модуля превышала число всевозможных сбоев, обнаружение и исправление которых возможно для данного способа, т.е. сп 2 (2)где К - разрядность используемыхфиксированных групп.Во-вторых, для обеспечения однозначности необходимо соблюдать условие неравенства между собой контрольных признаков при возникновении сбоев в любой из групп, то естьаС Ф а С 4, (3)где а .(а,) - величийа ошибок в 1.-й(3-той) группе,или в общем видеиФ,л аС.-а С ФО, (4)где знакх; означает вычислениеконъюнкций велйчин х . Выражение(4) малоудобно ввиду сложности реше"ния неравенств.в булевой алгебре,поэтому для практических расчетовиспользовать получаемое из (2), (3)выражениеаС,-аС(5)где Й - любой из натурального рядачисел.При этом при вычислении контрольного признака в соответствии с выражением (1) .обеспечивается независимая (параллельная) обработка информацич по каждой иэ групп, что позволяет получить высокое быстродействие устройств контроля, реализующих прйведенный способ кодированияйнФормации,- /При поиске и исправлении ошибок.в коде числа вновь производится вы-числение контрольного признака всоответствии с выражением (1). Полученный контрольный признак сравнивается с контрольной частью кода числа. Если они отличаются, то это свидетельствует о наличии искажения з коде. числа. Поскольку контрольный модуль и весовые коэффициенты, вычисленные в соответствии с (2,.5),обеспечивают однозначное соответствиемежду содержимым любой из групп ивеличиной контрольного признака,топо величине, разности контрольныхпризнаков однозначно определяетсявеличина ошибки и номер группы, вкоторой она произошла. Действитель"но, при наличии ошибки в представ-лении числа величина контрольногопризнака в соответствии с (1) .будетравнауг (А)Е А С + ( с +4 сЦСу +Я1С 1рЯ,ф(б)где дс(. - величина ошибки в 3-тойгруппе кода числа.В результате сравнения полученно"го в соответствии с (б) контрольногопризнака числа с контрольной частьюкода числа получимг (А) =г (А) -г (АО, (7)Если предварительно рассчитатьтаблицу соответствия между любойвозможной ошибкой в любой иэ группкода числа и величиной разности конт"рольных признаков (7), то по величине разности контрольных признаковиз такой таблицы (таблицы поправок)выбирается адрес и величина группо"вой ошибки, что позволяет произвес"ти ее коррекцию.На чертеже представлено устройст-.во для исправления ошибок к системеостаточных классов, схема.Устройство содержит регистр 1 информационных разрядов кода числа,регистр 2 контрольных разрядов кодачисла, блок 3 памяти, блок 4 сверткипо контрольным основаниям, вычита"тель 5, блок б памяти ошибок, первый коммутатор 7, сумматор 8 коррекции, второй коммутатор 9.При этом входы блока 3 памятисоединены с выходами регистра 1информационных разрядов кода числа,а его выходы со входами блока 4,свертки по контрольным основаниям, .информационные входы первого коммутатора 7 подключены к выходам регистра информационных разрядов кода числаа выходы - ко вторым входам сумматора 8, выходы которого соединеныс информационными входами второгокоммутатора 9, первые выходы блокаб памяти ошибок подключены н первымвходам сумматора 8, аее вторыевыходы - к управляющим входам первого, и второго, коммутаторов, а выходы второго коммутатора 9 соединенысо входами регистра 1 информационныхразрядов кода числа,Регистр 1 информационных разрядовкода числа и регистр 2 контрольныхразрядов кода числа предназначены,для приема .и хранения в;процессекоррекции кода числа. Блок 3 памяти.ной группы добавляется поправка,60 полученная из таблицы поправок бло 65 15 20 25 35 40 45 50 по коду группы обеспечивает выборкувеличин, равных остаткам по контрольному модулю от произведений этихгрупп на соответствующие весовыекоэффициенты. Блок 4 свертки по контрольным основаниям 4 обеспечиваетформирование контрольного признака числа в соответствии с выражением(1), Вычитатель 5 реализует операцию вычитания по контрольному основанию. величин, подаваемых на еговходы. В таблице поправок, находящейся в блоке б памяти ошибок по разности.контрольных признаков, наее входе формируется величина ошибки и адрес группы, в которой онапроизошла. С этой целью каждаяячейка памяти таблицы поправок бсодержит коды адреса группы и величины ошибки в ней, которые выдаютсясоответственно на вторые и первыевыходы блс)ка б. Первый и второй ком"мутаторы 7, 9 обеспечивает передачусоответствующих кодов групп приналичии на их управляющих входах разрешающих сигналовСумматор 8 обеспечивает сложение кода группы информационной часты кода числа с поправкой, обеспечивая тем самым исправление ошибок; Устройство работает следующим образом. Код контролируемого числа .записывается соответственно на .регистр 1 информационных разрядов кода числа 1 и на регистр 2 .контрольных разрядов кода числа. В блоке 3 памяти по коду каждой группы производится считывание величин, равных остаткам по контрольному основанию от произведений этих групп на соответствующие весовые коэффициенты. Полученные величины в блоке 4 свертки складываются по контрольному основанию, образуя контрольный признак контролируемого числа, из которого в вычитатеп 5 вычитается по контрольному модулю содержимое регистра 2 контрольной части. Полученная разность использу" ется для выборки из таблиц поправок блока б памяти ошибок величины ошибки и адреса группы, в которой она произошла. Адрес группы формируется в виде разрешающего сигнала наодной из выходных шин блока б памятиошибок. Этим самым разрешаетсяпередача на сумматор 8 через первыйкоммутатор 7 информации только тойгруппы, искажение в которой обнару жено. В сумматоре 8, к коду искаженка б так, чтобы исправить обнаруженную ошибку, Второй коммутатор 9 обеспечивает передачу скорректированного кода группы в соответствующие разряды регистра 1 информационных842820 Количество контролируемых разрядов Вели- Крат- чина, ностьошиб- ки Получаемый.выигрыш вчисле контролируемыхразрядов при контроле из- при контроле спо вестными спосо" собом взвешенных бами групп 229 2 3056 1,86 881 3 105 2,33 14 673 4 1616 4 2,57 88 15 5,87 25 ЗО п 30 14. 10 = 30 11 = 55 до разрядов. кода числа. На этом коррекция .ошибки заканчивается.ЭфФективность обнаружения и исправление ошибок с помощью предлагаемого устройства иллюстрируется приКак следует из таблицы при коррекции, например, четырехкратных ошибок известными способами при использовании оснований 673(1616), требующими дитя своего размещения (10(11) разрядов, можно обеспечить контроль только 14(15)-ти разрядных чисел, т,е. требуемая избыточность составляет 71(73)% от числа информационных разрядов, что в ряде случаев при практической реализации неприемлемо. При контроле с помощью предлагаемого устройства требуемая избыточность составляет 27(12)%, т.е. достигает вполне приемлемой для реализации величины.С другой стороны, обеспечиваемая при контролеизвестными способами разрядность чисел недостаточна для построения современных ЭВМ, требующими 3064 информационных разрядов, В этом случае для коррекции 3064 разрядных слов потребуется испольэовать от контрольных разрядов при использовании известных способов и пК =101.1 разрядов при использований предлагаемого устройства, где знак Хозначает вычисление ближайшего большого целого к величине Х, При этомизбыточность снижается от 86100до 1733. Данное снижение иэбыточ"ности достигается по всей ЭВИ, кромеустройства управления (арифметико"логические устройства, память всех.уровней, устройства ввода-выводаи отображение), Дополнительные элементы вводятся только в устройствокоррекции и потребуют аппаратурных 35 40 45 50 55 65 веденной ниже таблице. В таблице приведено количество контролируемых разрядов при коррекции ошибок определенной кратности известными способами (4) и предлагаемым способом. затрат не более, чем для реализациивходящего в состав прототипа блокаперевода .из системы остаточных классов в позиционную систему счисления,который в предлагаемом устройствене используется. Следовательно,элементы, вводимые в устройство не приведут к дополнительным затратам оборудования,Формула изобретения Устройство для исправления ошибок в системе остаточных классов, содержащее регистры информационных и контрольных разрядов, вычитатель, блок свертки по контрольным основаниям, блок памяти ошибок и сумматор, причем входы регистров информационных и контрольных разрядов являются входами устройства, выход регистра контрольных разрядов соединен с первым входом вычитания, выход которого соединен со входом блока памяти ошибок, первый выход блока памяти ошибок соединен с первым входом сумматора, выход блока свертки по контрольным основаниям соединен со вторым входом вычитателя, о т л и ч а ю щ е е с я тем, что, с целью сокращения оборудования, в устройство введены первый и второй коммутаторы н блок памяти, причем выходы регистра информационных разрядов соединены со входами блока памяти. и с группой информационных входов первого коммутатора, выходы которого соединены со вторым входом сумматора, выход сумматора соединен с информационныии входами второго коммутатора; выходы которого соединены с соответствующими входами регистра информационных разрядов, выходы:блока памяти соединены со входами блока сверток по контрольным основаниям, второй842820 10 тель И.СигалоИ. Коштура Сос рректор Н,Стец ктор А.Власенко ирвк 745сударстве нногоиэобретенийсква, З,Подписи каэ 5103/61ВНИИПИпо дел113035 комитета СССР открытий ужасная наб., д/5ю ееа Ю вилиал ППП фПатентф, г.ужгород, ул.Проектная,выход блока памяти ошибок соединенс управляющими входами первого ивторого коммутаторов.Источники информации,принятые во внимание при экспертизе1. Авторское свидетельство СССРВ 614437, кл. Г 06 Р 11/08,опублик.1972. 2. Авторское свидетельство СССРМ .369567, кл. С 06 Р 11/08,опублик.1973 3. Журавлев Ю.П., Котелюк А,А Циклинский Н,И. Надежность и конт" роль ЭВИ, М , ффСоветское радиоф,1978, с.137 (прототип).

СмотретьЗаявка

2816370, 17.07.1979

ВОЕННАЯ ИНЖЕНЕРНАЯ РАДИОТЕХНИЧЕСКАЯОРДЕНОВ ОКТЯБРЬСКОЙ РЕВОЛЮЦИИ ИОТЕЧЕСТВЕННОЙ ВОЙНЫ АКАДЕМИЯ ПРОТИВО-ВОЗДУШНОЙ ОБОРОНЫ ИМ. МАРШАЛАСОВЕТСКОГО СОЮЗА ГОВОРОВА Л. A

ВАСИЛЕНКО ВЯЧЕСЛАВ СЕРГЕЕВИЧ, ГРИГОРЬЕВ СЕРГЕЙ ИВАНОВИЧ

МПК / Метки

МПК: G06F 11/08

Метки: исправления, классов, остаточных, ошибокв, системе

Опубликовано: 30.06.1981

Код ссылки

<a href="https://patents.su/5-842820-ustrojjstvo-dlya-ispravleniya-oshibokv-sisteme-ostatochnykh-klassov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для исправления ошибокв системе остаточных классов</a>

Предыдущий патент: Устройство для контроля дискретныхлогических cxem

Следующий патент: Устройство для контроля логическихблоков

Случайный патент: Газовый затвор