Регенератор двоичных символов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 723785

Автор: Платонов

Текст

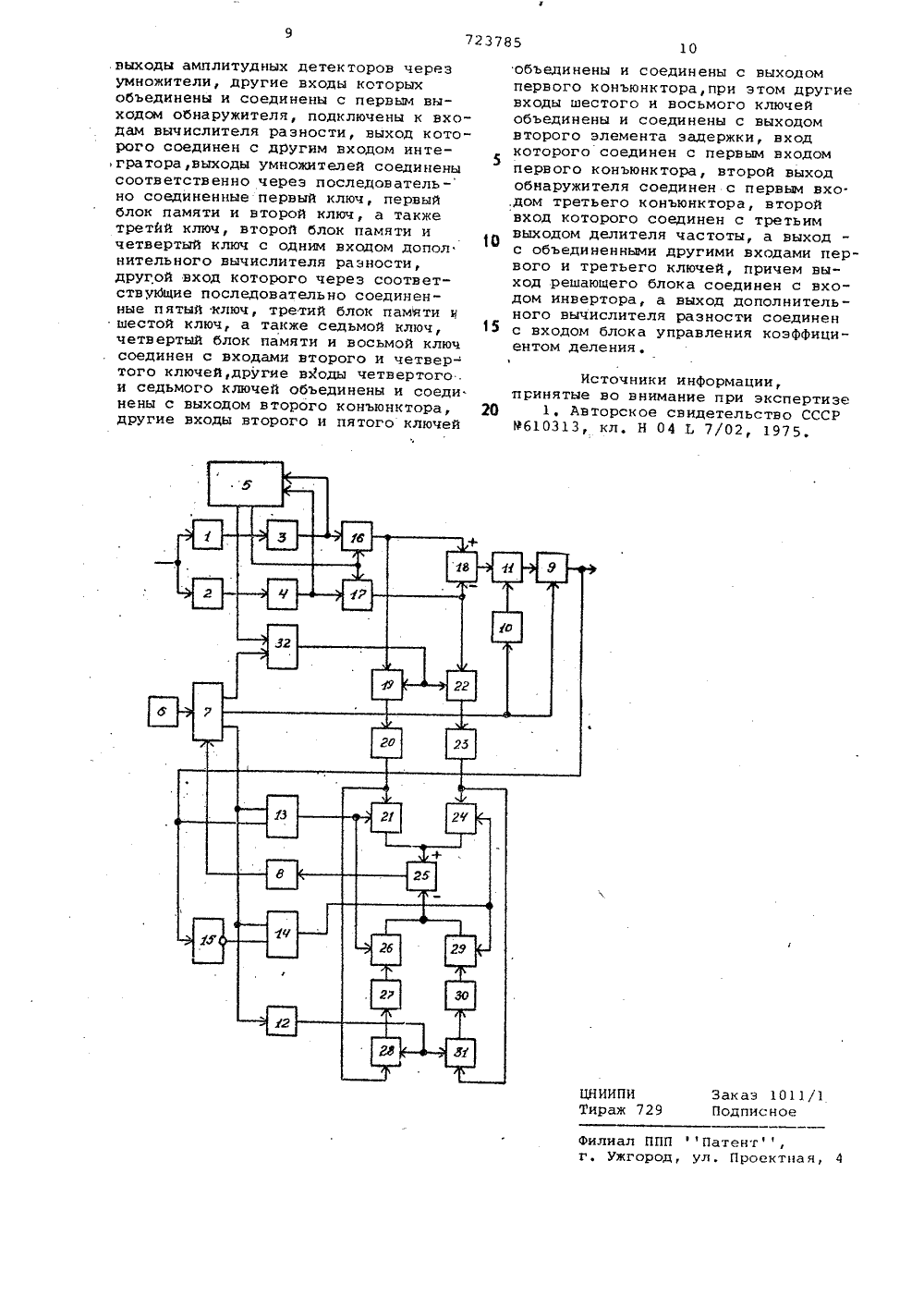

Союз Советских Социалистических Республик(51 М, Кл. Н 04 1 7/02 Государственный комитет СССР по делам изобретений и открытий(72) Автор изобретения В,И.Платонов Ленинградский институт авиационного приборостроения(54) РЕГЕНЕРАТОР ДВОИЧНЫХ СИМВОЛОВ Изобретение относится к радиотехнике и может быть использованов системах передачи дискретной информации широкополосными сигналами 5по каналам с замираниями и рассеянием во времени.Известен регенератор двоичных символов, содержащий соединенные повходу согласованные фильтры, выходы 1 Окоторых через амплитудные детекторысоединены с входами обнаружителя,последовательно соединенные опорныйгенератор и делитель частоты, второйвход которого соединен с выходомблока управления коэффициентом деления, а первый выход соединен содним входом решающего блока непосредственно, а с другим входомчерез последовательно соединенныепервый элемент задержки и интегратор, соответствующие выходы делителя частоты соединены с входом второгоэлемента задержки и первыми входамипервого и второго конъюнкторов,второй 25вход первого конъюнктора соединенчерез инвертор с вторым входом второго конъюнктора, а также вычислитель разности, первъй ключ и третийконъюнктор 1,30 Недостатком этого регенаратора является низкая помехоустойчивость.Цель изобретения - повышение помехоустойчивости.Для этого в регенератор двоичных символов введены умножители, четыре блока памяти, семь ключей и дополнительный вычислитель разности, причем выходы амплитудных детекторов через умножители, другие входы которых объединены и соединены с первым выходом обнаружителя, подключены к входам вычислителя разности, выход которого соединен с другим входом интегратора, выходы умножителей сое.- динены соответственно через последовательно соединенные первый ключ, первый блок памяти и второй ключ, а также третий ключ, второй блок памяти и четвертый ключ с одним входом дополнительного вычислителя разности, другой вход которого через соответствующие последовательно соединенные пятый ключ, третий блок памяти и шестой ключ, а также седьмой ключ, четвертый блок памяти и восьмой ключ соединен с входами второго и четвертого ключей, другие входы четвертого и седьмого ключейобъединены и соединены с выходомвторого конъюнктора, другие входывторого и пятого ключей объединеныи соединены с выходом первого конъюнктора, при этом другие входы шестого,и восьмого ключей объединены и соединены с выходом второго элемента задержки, вход которого соединен спервым входом первого конъюнктора,второй выход обнаружителя соединенс первым входом третьего конъюнктора, второй вход которого соединенс третьим выходом делителя частоты,а выход - с объединенными другимивходами первого и третьего ключей,причем выход решающего. блока соединен с входом инвертора, а выходдополнительного вычислителя разностисоединен с входом блока управлениякоэффициентом деления.Йа чертеже изображена структурнаясхема регенератора.Регенератор содержит соединенныепо входу согласованные фильтры 1, 2,выходы которых через амплитудныедетекторы 3, 4 соединены со входамиобнаружителя 5, последовательносоединенные опорный генератор 6и делитель 7 частоты, второй входкоторого соединен с блоком 8 управления коэффициентом деления, а первый выход соединенс .входом решающего блока 9 непосредственно, а сдругим входом - через последователь.но соединенные первый элемент 10задержки и интегратор 11.Второй выход делителя 7 частотысоединен с входом второго элемента12 задержки и объединенными первымивходами первого и второго конъюнкторов 13, 1 4. Второй вход первогоконъюнктора 13 соединен через инвер.тор 15 .с вторым входом второгоконъюнктора 14,ВыхОды амплитудных детекторов3, 4 через умножители 16, 17, другие входы которых объединены и соединены с первым выходом обнаружителя 5, подключены к входам вычислителя 18 разности, выход которогосоединен с другим входом интегратора11, Выходы умножителей 16, 17 соединены соответственно через последовательно соединенные первый ключ 19,первый блок 20 памяти и второй ключ21, а также третий ключ 22, второйблок; 23 памяти и четвертый ключ 24 содним входом дополнительного вычислителя 25 разности, другой вход которого через соответствующие последовательно соединенные пятый ключ 26,третий блок 27 памяти и шестой ключ28, а также седьмой ключ 29, четвертый блок 30 памяти и восьмой ключ 31соединен с входами второго ключа21 и.четвертого ключа, 24.Другие входы четвертого 24 и седьмого 29 ключей объединены и соединены с выходом второго конъюнктора 14. Другие входы второго 21 и пятого .26ключей объединены и соединены с выходом первого конъюнктора 13, Другиевходы шестого 28 и восьмого 31 ключей объединены и соединены с выхо 5 дом второго элемента 12 задержки.Второй выход обнаружителя 5 соединен с первым входом третьегоконъюнктора 32, второй вход которогосоединен с третьим выходом делителя10 7 частоты, а выход - с объединеннымидругими входами первого 19 и третье -го 22 ключей. Выход решающего блока9 соединен с входом инвертора 15, авыход дополнительного вычислителя25 разности соединен со входом блока8 управления коэффициента деления.Регенератор работает следующимобразом,На вход подается сигнал, принимаемый на фоне. аддитивного флюктуационного шума, причем каждая посылка передается широкополосным сигналом Я (С)или Я (С), Передаваемые сигналыортогональны. Проходя согласованныефильтры 1 и 2,сигнал сжимается во25 времени, происходит разделение лучей.С выходов амплитудных детекторов3 и 4 сигналы поступают на входы обнаружителя 5, а также на первые вхоЗ 0 ды соответствующих умножителей 16,17, В те моменты времени, когда принимается решение о наличии сигнала(луча), на импульсном выходе обнаружителя 5 появляется единичный потенЗ циал, который подается на первыйвход третьего конъюнктора 32,При этом на выходе обнаружителя5 вырабатывается оценка амплитудысоответствующего луча, котораяподается на вторые входы умножителей 16 и 17, Если сигнал (луч) внекоторый момент времени отсутствуетили не обнаруживается, то оценкаамплитуды на выходе обнаружителя 5равна нулю.45 Одновременно обнаружение импульсного сигнала и оценку его амплитудыможно осуществить, например, с помощью дискретных накопителей,В случае флюктуирующих.лучей оцен 50 ку текущей амплитуды с последующимобнаружением можно осуществить вкаждом элементе временной дискрети -зации также с помощью фильтров Калмана.В результате перемножения огибающей процесса на оценку амплитуды сильные лучи, усиливаются больше (подчеркиваются), а слабые - меньше (подавляются)После перемножения на оценку амплитуды сигналы вычитаются и40 на выходе вычислителя 18 разностиполучается биполярный видеосигнал.Мощности обнаруженных лучей суммируются в интеграторе 11. Таким образом, наличие умножителей 16 и 17,а также обнаружителя 5 позволяет от 723785делить сигналы лучей от тех временных интервалов, где присутствуеттолько шум, а также осуществитьвесовое суммирование обнаруженныхлучей, что повышает помехоустойчивость устройства. Решение о значениидискретного информационного параметра 10.)=+-1 принимается в решающемблоке 9 путем опроса один раз затакт состояния интегратора 11. Еслив момент опроса напряжение навыходе интегратора 11 положительно,то принимается решение о том, чтопередан символ 1 , при отрицательном выходном напряжении интегратора 11 принимается решение в пользусимвола О (этому соответствуетнулевой потенциал на выходе решающего блока 9) . Моменты регистрациисимволов (моменты опроса) определяются импульсами, следующими с периодом Т и поступающим на второйвход решающего блока 9 с первогоимпульсного выхода делителя 7 частоты, Эти же импульсы через первыйэлемент 10 задержки поступают навторой вход интегратора 11 для егообнуления, Вероятность ошибочнойрегистрации символов минимальна,если н интервал интегрирования попадают сигналы лучей одной полярности, относящиеся к одному переданному символу. Это возможно, когдаимпульсы,. управляющие работой решающего блока 9 и обнуляющие интегра.тор 11, располагаются между последним лучом предыдущей посылки и перным лучем последующей посылки, Приэтом предполагается, что интерналрассеяния сигнала во времени Тменьше тактового интервала Т нанекоторую защитную величину,При появлении на импульсном выхо-.де обнаружителя 5 очередного импульса обнаружения и отсутствии запрещающего (нуленого) потенциала навтором входе третьего конъюнктора32, замыкаются ключи 19 и 22, а амплитуды процессов, действующих вэти моменты времени на выходахумножителей 16 и 17, запоминаются впервом ЫО и втором 23 блоках памяти.Один раз за такт на втором импульс -ном выходе делителя 7 частоты появ -ляется синхроимпульс, который, пройдя второй элемент 12 задержки, замыкает ключи 28 и 31. В эти моментывремени информации с выхода первого .20 и второго 23 блоков памяти переписывается соответственно н третий27 и четвертый 30 блоки памяти.Таким образом, в моменты появлениясинхроимпульсов на выходах блокон20 и 23 присутствуют напряжения,имевшие место в момент последнегообнаружения луча на текущем К-мтакте, а на выходах блоков 27 и 30присутствуют напряжения, имевшиеместо в момент последнего обнаруже ния луча на предыдущем (К)-мтакте. В качестве блоков памятимогут быть использованы, напримеР,конденсаторы в цепи с малой постоянной времени заряда (меньшей, чемдлительность элемента временнойдискретизации) и большой посравнению с тактом постоянной времениразряда,Опрос. состояния интегратора 11в решающем блоке 9 и обнуление интегратора 11 происходит раньшена величину 3 , чем на второмимпульсном ныходе делителя 7 час 15тоты появляется очередной синхроимпульс временное положение которого и определяет текущую оценку(. (К) задержки первого луча (Кномертакта). Таким образом, к моменту появления синхроимпульса реше 20 ние о значении информационногодискретного параметра 1 (1) ужепринято и на выходе решающего блокал9 к моменту т. (К) устанавливаетсяединичный или нулевой потенциал.Единичный потенциал на выходерешающего блока 9 открывает конъюйктор 13, запирая через инвертор 15конъюнктор 14, Нулевой потенциал навыходе решающего блока 9, наоборот,запирает конъюнктор 13 и открываетконъюнктор 14. Таким образом, синхронизирующий импульс, поступающийлв момент времени с (К) на первыевходы конъюнкторов 13 и 14,появляется в зависимости от потенциала на ныходе решающего блока 9, либо науправляющих входах ключей 21 и 26,либо на управляющих входах ключей24 и 29. В результате на входыдополнительного вычислителя 25разности поступают либо напряженияс выходов первого 20 и третьего 27блоков памяти, либо напряжения с выходов второго 23 и четвертого 30блоков памяти,45 Введем следующие обозначения.Ч (Ю - напряжение на выходе первого(при д = 1) амплитудногодетектора 3 или второго (прид = 2) амплитудного"детек -50 тора 4 в 1-м элементевременной дискретизациина К-м такте;С И,2, Ь,гд(. - количество элементоввремейной дискретизации натактовом интервале;А Ю- оценка амплитуды входного процесса в Й-м элементе временной дискретизации на К-мтакте;Л=Л- номер дискрета, в котором последний раз произошло обнаружение луча на К-м тактеТаким образом, в блоках 20 и 23памяти на текущем К-м такте запоминаются величины Ц (К). Ч 0(К), а в65 блоках 27 и 30 памяти на К-м такте.выходы амплитудных детекторов через умножители, другие входы которых объединены и соединены с первым выходом обнаружителя, подключены к входам вычислителя разноси, выход которого соединен с другим входом инте,гратора,выходы умножителей соединены5 соответственно через последователь - но соединенные первый ключ, первый блок памяти и второй ключ, а также третий ключ, второй блок памяти и четвертый ключ с одним входом дапол нительного вычислителя разности, другой вход которого через соответствующие последовательно соединенные пятый ключ, третий блок памйти ц шестой ключ, а также седьмой ключ, 15 четвертый блок памяти и восьмой ключ соединен с входами второго и четвер- того ключей, другие входы четвертого . и седьмого ключей объединены и соеди. иены с выходом второго конъюнктора, 33 другие входы второго и пятого ключей объединены и соединены с выходомпервого конъюнктора, при этом другиевходы шестого и восьмого ключейобъединены и соединены с выходомвторого элемента задержки, входкоторого соединен с первым входомпервого конъюнктора, второй выходобнаружителя соединен с первым вхо,дом третьего конъюнктора, второйэход которого соединен с третьимвыходом делителя частоты, а выходс объединенными другими входами первого и третьего ключей, причем выход решающего блока соединен с входом инвертора, а выход дополнительного вычислителя разности соединенс входом блока управления коэффициентом деления,3 Источники информации,принятые во внимание при экспертизе 1. Авторское свидетельство СССР 9610313, кл. Н 04 1 7/02, 1975, ЦНИИПИ Заказ 1011/1Тираж 729 Подписное илиал ППП Патент, Ужгород, ул, Проектная,

СмотретьЗаявка

2568829, 10.01.1978

ЛЕНИНГРАДСКИЙ ИНСТИТУТ АВИАЦИОННОГО ПРИБОРОСТРОЕНИЯ

ПЛАТОНОВ ВЯЧЕСЛАВ ИВАНОВИЧ

МПК / Метки

МПК: H04L 7/02

Метки: двоичных, регенератор, символов

Опубликовано: 25.03.1980

Код ссылки

<a href="https://patents.su/5-723785-regenerator-dvoichnykh-simvolov.html" target="_blank" rel="follow" title="База патентов СССР">Регенератор двоичных символов</a>

Предыдущий патент: Формирователь коде морзе

Следующий патент: Телеграфное реле

Случайный патент: Способ переключения регулировочных обмоток реактора и устройство для его осуществления