Запоминающее устройство системы 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 693438

Авторы: Бурковский, Сташков, Цогоев

Текст

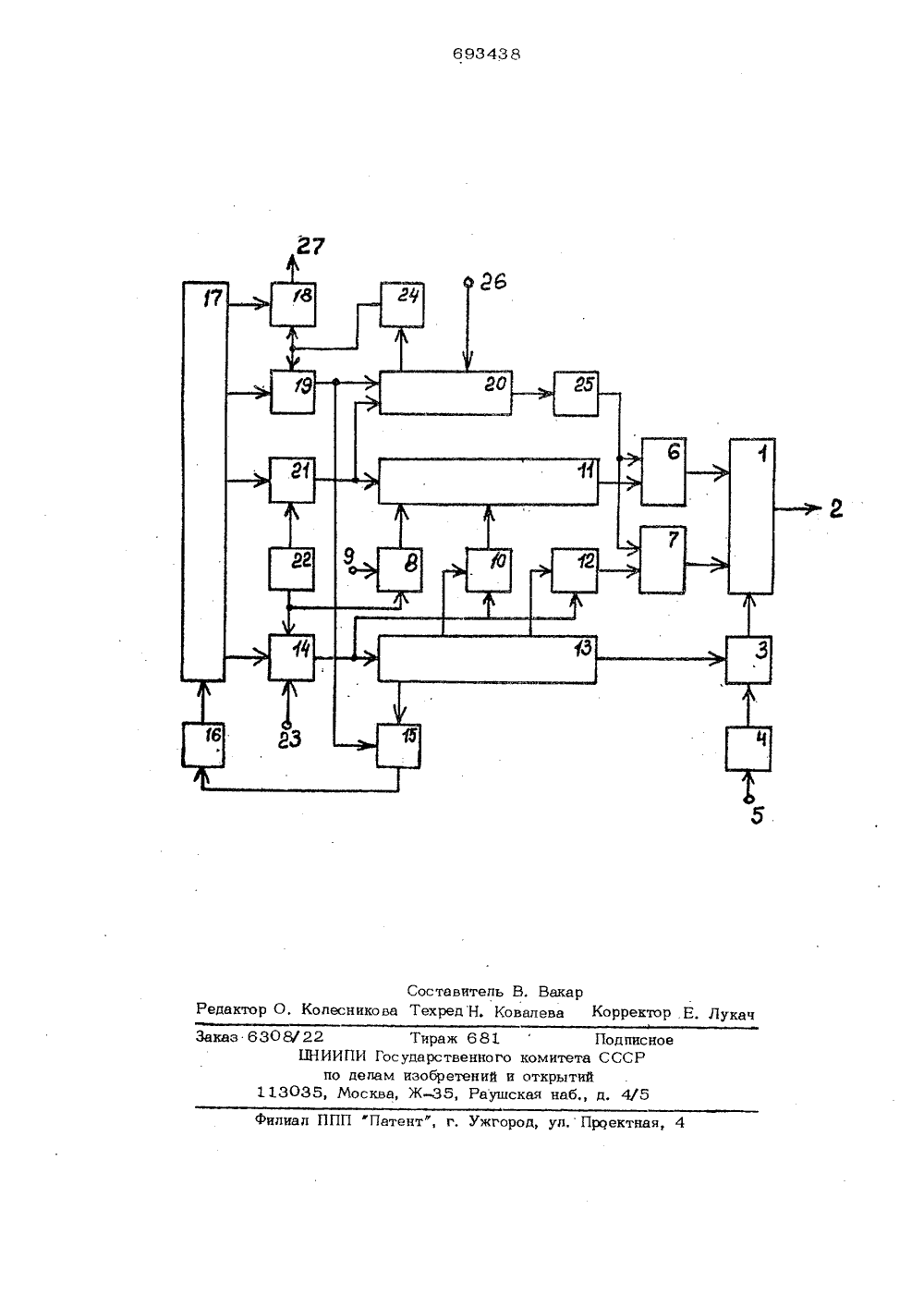

)Заявлено 20,0 77(21) 2497585/18-2 исоедицением заявки РЙ арстееннын но СССР3) Приоритет Опубликовано тенин па делам изо и атнрюЗ)УДК 68 .66 (088. 8 7 ата опубликования описания 28, 10,Авторыобретени В. 1, Сташков Бур ский, Т, К. 11 огоев( 54) ЗАПОМИНАЮЩЕЕ УС НЕРАЗРУША 10 ШИМ НА МНО 1 ООТВЕРСТ ходамп а дтыванця соединен тьей У является акопителя имеют д м е Изобретение относится к области вычислительной техники и может быть использовано в запоминаюших устройствах(ЗУ) системы 2 Д с неразрушаюшим считыванием информации на многоотверстных ферритовых элементах,Известны ЗУ системы 2 Д с неразрушаюшим считыванием информации намногоотверстных ферритовых элементах12 1,Одно из известных ЗУ системы,2 Дс неразрушаюшим считыванием информации на ферритовых элементах содержит накдпитель, один из входов которого через формирователи разрядных токов записи связан с регистром числа, адругие входы - с формирователями адресных токов считывания и адресныхтоков записи, первую и вторую схему И,соединенные через схему И 1 И со входомадресных формирователей токов считывания 1 . Третья схема И подключенако входу адресных формирователей токовзаписи. Регистр адреса связан через д.10.79 Бюллетень Рй 39 ТРОИСТВО СИСТЕМЫ 2 ДСЧИТЫВАНИЕМ ИНФОРМА 11 И 11 Х ФЕРРИТОВЫХ ЭЛЕМЕНТАХ дцфратор адреса со вторымпресных формирователей токови записи. Генератор цмпульсосе входамц первой, второй цсхем И,Недостатком указанного 3то, что выходные сигналы с нми при считывании информаццнестабильные параметры. оНаиболее близким техническим решением к данному изобретению является ЗУ системы 2 Д с неразрушаюшим считыванием информации на многоосверстных ферритовых элементах, содержащеенакопитель, первый вход которого соединен с выходом формирователя разрядных токов запцс и, второй вхо с выходом формирователя адресных токов записи, а третий - с выходом формирователя адресных токов считывания, первый вход которого соединен с выходом дешифратора адреса, а второй - с выходом первого элемента И 111первый и второй входы котарога соответственно соединены с выходами первого и второго элементов И, регистр адреса, выход каторога соединен со входом дешифратора адреса, регистр числа, выход которого соединен с первым входам формирователя разрядных токов записи, третий элемент И, выход которого соединен со вторым входом формирователя адресных токов записи, первый вход которога подключен к выходу дешифратора адреса и генератор импульсовНедостатком известного ЗУ является нестабильность параметров выходного сигнала с накопителя при считывании информации, что снижает надежность раба"ы ЗУ 5 Иель изобретения - повышение надежности устройства путем ка 1 лпенса 20 цип частичных разрушений .нформации.Для достижения поставленной цели устройство содержит второй элемент ИЛИ, четвертый, пятый, шестой и седьмой элементы И, счетчик циклов, дешифра- тор циклов, блок анализа адреса, счетчик тактов, при этом соответствуюшие выходы дешифратора циклов саединень( с первыми входами четвертого, пятого, шестого к седьмого элементов И, аВход с Выходам счетчика циклов, Вход 2530 которого соединен с выходом второго элементе ИЛИ, первый вход которого соединен с первым выходом счетцике тактов, а второй - с первым выходом шестого элемента И, второй выход счетчика тактов соединен са вторымвходом формирователя разрядных токов записи, третий и четвертый соответственно с первыми входами второго и третьего 40 элементов И, вторые входы которых соединены с выходом четвертого элемента И, соединенного со входом счетчике тактов, первый выход генератора импульсов соединен со вторым входом седь- (5 мого элемента И, а второй выход - со вторым входом четвертого элемента И и входом первого элемента И, выход седьмого элемента И подключен к третьему входу первого элемента ИЛИ, а первый 50 выход ш: - ,стога элемента И соединен с первым входом регистра адреса, второй вход которого соединен с выходомседьмого элемента И, вход блока анализа соединен со вторым выходам ре ,гистра адреса, а выход подключен ка вторым входам пятого и шестого элементов И. На чертеже представлена блок-схема предлагаемого устройстве, Занаминаюшее устройства садерж т накопитель 1 выходные числовые пины 2, формирователь 3 разрядных токов записи и ре гисгр 4 числа со входными чили ши)лами 5, фарьлираватель 6 адрескьгл токов считывания ц формирователь 7 адресных токов записипервый элемент И 8, шина "чтение" 9, второй элемент И 10, первый элемент ИЛИ 11, третий элемент И 12, счетчик 13 тактав,четвертый элемент И 14, второй элемент ИЛИ 15, счетчик 16 циклов, дешифратор 17 циклов, пятый элемент И 18, шестой элемент И 19, регистр 20 адреса, седьмой элемент И 21, генератор импульсов 22, шина 23 записи, блок 24 анализа адреса, децлифретар 25 адреса, адье"н).е и"лн э 6Синхропмпульс с генератора импульсов 22 через первый элемент И 8 при наличии на шине учтен лл" 9 разрешающего потенциала и первый элемент ИЛИ 11 поступает на вход ыбраннаго формирователя 6 адресного тока считывания, В результате по избранной координате накопителя 1 протекает так считывания и на выходных ч).славых шинах 2 вырабатывается кад считанного числа.В режиме записи информации па: адресным шипам 26 в регистр 20 адреса поступает кад адресаа по входпым числоиьгм шип(ам 5 в регистр 4 числа:- кад цпсла. На управляющей шине "запись" 23 в этсм режиме имеется разрешающий потенциал, Сцетчик 16 циклов находится в исходном состоянии, поэта)лу на выходе дешпфретара 17 сушествуют потенциалы, открываошие четвертый 14 и шестой 19 элементы И, и закрыве)ошие пятый 18 и седьмой 21 элементы И. Синхраимпульсы с генератора 22 через четвертый элемент И 14 поступают на входы счетчика 13 тактов, второй элемент И 10 и третий элемент И 12, Е)тарые входы второго и третьего элементов И 10 и 12 управляются/ счетчиком 13 таким образом, что в течение определенного времени поочеред- но синхроимпульс проходит через один из этих элементов И. В результате этого поочередно срабатывакт формирователи адресных токов записи и формирователи 6 адресных токов считывания, т.е, в из-. бранной координатной шине накопителя цередуются импульсы тока поотивополож ь 6 9343 ной полярности, При этом от счет тика 13 на формирователи 3 разрядных токов записи поступает разрешаюший потенциал, в реЬультате чего по разрядным тцинам накопителя 1 протекают токи, направлеНИе каждого на которых соответствует значению соответствуюшего разряда регистра 4 числа. Указанные процессы обеспечиватот необходимые изменения магнитных состояний запомииаюштех эле- еО ментов, т.е. запись етнформации в течение некоторого промежутка времени, величина которого зависит от физических свойств запоминатоших элементов. Заданное время отсчитывается счетчиком 13 тактов, Е 5 который при достижении определенной кодовой комбинации запрещает рабогу разрядных формирователеет 3 токов записи и запрешает прохождение синхроимпульсов через третий элемент И 12 на запуск формирователей 7 адресных токов записи, Последующий промежуток времени, который также. ограничивается достижением оп 25 ределенной кодовой комбинации в счетчике 13 тактов характеризуется протеканием по избранной координате нескольких токов считывания. Эго необходимо для устранения известного явЗО ления, заключаюшегося в том, что при нескольких обрашениях за информацией сразу же после записи сигналов на выходе накопителя амплитуда сигнала на порядок больше и с более пологим фронЭ 35 том по сравнению с нормализованным сигналом, который образуется после воздействия на избранную координату нескольких токов считывания, Вследствие этого несмотря на значительную ампли 40 туд из-за полого фронта при жесткоме. положении строба, ненормализованные выходные и сигналы с накопителя могут быть неправильно восприняты усилителями считывания.45По окончании процесса нормализации счетчик 13 вырабатывает запрешаюший потенциал на второй элемент И 10 и разовый сигнал, поступающий через второй элемент ИЛИ 15 на вход счетчика50 16 циклов, При изменении состояния счетчика 16 с помошью дешифратора 17 вырабатывается запрешаюший потенциал на вход четвертого элемента И 14 и разрешающие потенциалы на входы пято 55 го и шестого элементов И 18 и 19. В результате синхроимпульсы от генератора 22 через седьмой элемент И 21 поступают на счетный вход регистра 2 С 8 6адреса и через первый элемент ИЛИ 1 тна запуск формирователей 6 адресныхтоков считывания, Таким образом обеспетивается режим, при котором ток считьтваттетя последовательно протекает покоординатным шинам накопителя 1 всоответститтт с перебороьл кодов на реГистре 20 адреса, работаюшем в счетном режиме. При выходе из зотты массива адресов накопителя 1, охваченныхОдиной разрядной шиной записи, блок 24анализа адреса вырабатывает сигнал,осушествляютций через шсстой элементИ 19 сброс стартттттх разрядов регистр 20 адреса с це;ыо возврата к начал ; ра ОочеГО масс ит 3 а адресо В, Эгимже сиГналОм увеличиваетс я на единицучерез второй элемент ИЛИ 15 содержимое счегчика 6 ттетклов, В сттедюцтетлцикле все адг-.са массива буд 5 г подвергнуты воздеттстви:; токов счтттьтванетя,После вьтпотшения заданного количествациклов с дешифратора 17 поступаютзапрешаюшие потенциалы иа шестой иседьмой элементы И 19 и 21. Пятыйэлемент И 18 будет открыт и через неГО сиГнал с Олока 24 анализа адресапоступит в управляютцую шину "конецзаписи 27, произойдет сооос оажетмазаписи. К этому моменту времени всенеизбранные адреса, имеющие с избранным единую разряднуто обмотку записибудут подвергттуты ттеоднократтгому возДЕЙСТВЕИО ТОКОВ СЧЕЕТЫВанттЯ л ЧТО ЧНСТИЧно компенсирует разрутиееттть, произведенные в них разрядными токатлел в процессе записи,Предлагаемое запоминающее устроство без разрушения информации отничаегся от известных устройств типа 2 П многоотврестных ферритовых элементах стабильностью параметров выходных сигналов с накопителя в режиме считывания информации, Это дает возможность применить более простые и надежные схе могехнические решения, например, стабильность временных параметров выходного сигнала позволяет обеспечить надежную работу устройства при фиксированном во времени положении сигнала стробирования усилителей считывания,Стабилизация амплитуды выходного сигнала исключает забивание усилителей большим сигналом Ограничивающее быстродействие устройства, и, вместе с этим, повышаетнижний уровень амплитуды выходного сигнала, что приводит к повышению отношения полезного сигна 6 9343 (Эля к помехе, Тякцы Оооаэом испОльзо- вание предлагаемого изобретения обесцтт:.: чивает более ттаденчто ттаботт:тат отттгт тто,цтего устройства.Формуп изобретет:.ИяЗапоминающтее устройство системы 2 Я с неразрушяющцм считыванием ицфоръ;а=- пни на многоотверстных ферритовых зле ментах, содеркащее цакопнтель, первыц Вход которого соединен с выходом формирователя разрядных токов записи, второй вход -. с Выходом формирователя ддрРсных токОВ записи а третей " с выходом тЬОвмцрователя Ядпеснттх ОХОВ считывяцтщ первый вход котопогст сое- динен с ВИХОГОм цеДифратора адреса, я втОРОЙ - с Выходом первогс элемента ИЛИ, первый и второй входы которого . соответствечцо соединены с выходами пеРВОГ 0 и РтОРОГО злом ецтстВ Ит Рет цстР а Гтр ее а, выход которого соединен со входом цешифратора адреса, регистр чиа ла, выход которого соеццнец с первым ВХОДОМ фоРМИРОВатЕЛЯ РЯЗРЯДтГЫХ ТОКОВ - .,япттст 1 третий зттетчеттт И вт Гхоц Гг Оторр:,: ГО СОЕДИНЕН Со ВТОРЫМ ВХОДОМ фОРМНРОВД" тЕЛЯ ЯДРЕСНЫХ ТОКОВ ЗЯГПГСЦт ПЕРВЫЙ ВХОД которого подклточен к Выход", децти;рттято:., ра. адреса ц генератор цмпульсовт о т Л И Ч г Ю Щ Е Е С Я тЕЧт ЧТОт С ЦЕЛЬГО повышения 11 аде:кттост 11 устройства путем КОМПЕНСЯЦИЦ ЧЯС ТЦЧНЬг тъаттОУГДЕЦИЙ Гтн-: фоРМЯЦИИ 01 ГО СОДЕРЖИТ ВТОРОЙ Зт 1 ЕтгтЕЦ- ИЛИчетвертый, пятый. шестой ц сецт - мой элементы И, счетчик циклов цо" И:ЦАРЯТОГт тттгПСЛОВт бдеть: Гнцттщэа ЯПРЕСД. г еттчк тактов. грц этом соотвегсГвтче:- шце выходы децтвфрятооа ттцклов соеГПГ:те;: гтЫ С 11 Ер 3 ЬГМ 11 ВХОДЯМИ ЧЕТВЕРТОГО, Пя - того, тцестого и Г;едьмого элементов И,а ВХОД .- С Вт.тХОГСЧ СЧЕТЧИКЯ ЦИКЛОВ, вход которогс 1 соедццеГ, с выходом вто;гтт "0 згемента 11 Г.И, пярвый ВхОП котОООГо СОЕдИЦЕЦ С ПЕРВЫМ ВЫХОДОМ СЧЕТЧИ- ка тактов, а второй - с первым выходом ,:-=стого зле,тента Ивторой выход счет чика тактов соеГ 11 тен с:о вторым вхоцом формирователя разрядных токов записит третий и четвертый соответственна с первыми входами второго и третьего элементов И, вторые входы которых соединены с выходом четвертого элемента И, соединенного со гтходом счетчцка тактов, первый выход генератора импульсов соедттнсц со вторым входом седьмого элемента И, а второй выход - со вторым входом четвертого элемента И ц входом первого элемента И, ВГГход, седьмого элемента И годключеп к третьему входу первого элемента ИЛИ, а первый выход шестогтз элемецта И соединен с первым входом регистра адреса, второй вход которого соединен с выходом седьмого элемента И, вход блока анализа адреса соединен со вторым вьГходом регистра адреса,. я выход подключен ко вторым вхоГ 1 гм пятого и Гдестогз элементов И,Источники инфОрмапии,принятые во вничапие цри экспертизе1, Климов И, И, и др, Полупостоян:тое запоминаютдее устройство на тороцдальных магнитных сердечниках с цца.тетральтц,тмц отверстиями, Вопросы рацис- злектроцнцкц, сер, ЗВТ, 1970, вып, 5-6.2, Гецкиц В, Л, Започццающее устройство па трансфлтокссрах с записьюСоставитель В, ВакарРепектор О. Копеоиикоее Техреп Н. Ковепеве Корректор Е. ЛукачЗаказ 6308/22 Тираж 681 Подписное БНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, Ж, Раушская наб., д. 4/5 филиал ППП Патент", г. Ужгород, ул. Проектная, 4

СмотретьЗаявка

2497585, 20.06.1977

ПРЕДПРИЯТИЕ ПЯ Г-4152

БУРКОВСКИЙ ИГОРЬ ВЛАДИМИРОВИЧ, ЦОГОЕВ ТАЙМУРАЗ КАСПОЛАТОВИЧ, СТАШКОВ ВАЛЕРИЙ ГЛЕБОВИЧ

МПК / Метки

МПК: G11C 17/02

Метки: запоминающее, информации, многоотверстных, неразрушающим, системы, считыванием, ферритовых, элементах

Опубликовано: 25.10.1979

Код ссылки

<a href="https://patents.su/5-693438-zapominayushhee-ustrojjstvo-sistemy-2d-s-nerazrushayushhim-schityvaniem-informacii-na-mnogootverstnykh-ferritovykh-ehlementakh.html" target="_blank" rel="follow" title="База патентов СССР">Запоминающее устройство системы 2д с неразрушающим считыванием информации на многоотверстных ферритовых элементах</a>

Предыдущий патент: Ячейка памяти

Следующий патент: Резервированный сдвигающий регистр

Случайный патент: Феррорезонансный стабилизатор напряжения