Устройство статистического контроля аналого-цифрового преобразователя сигналов изображения

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

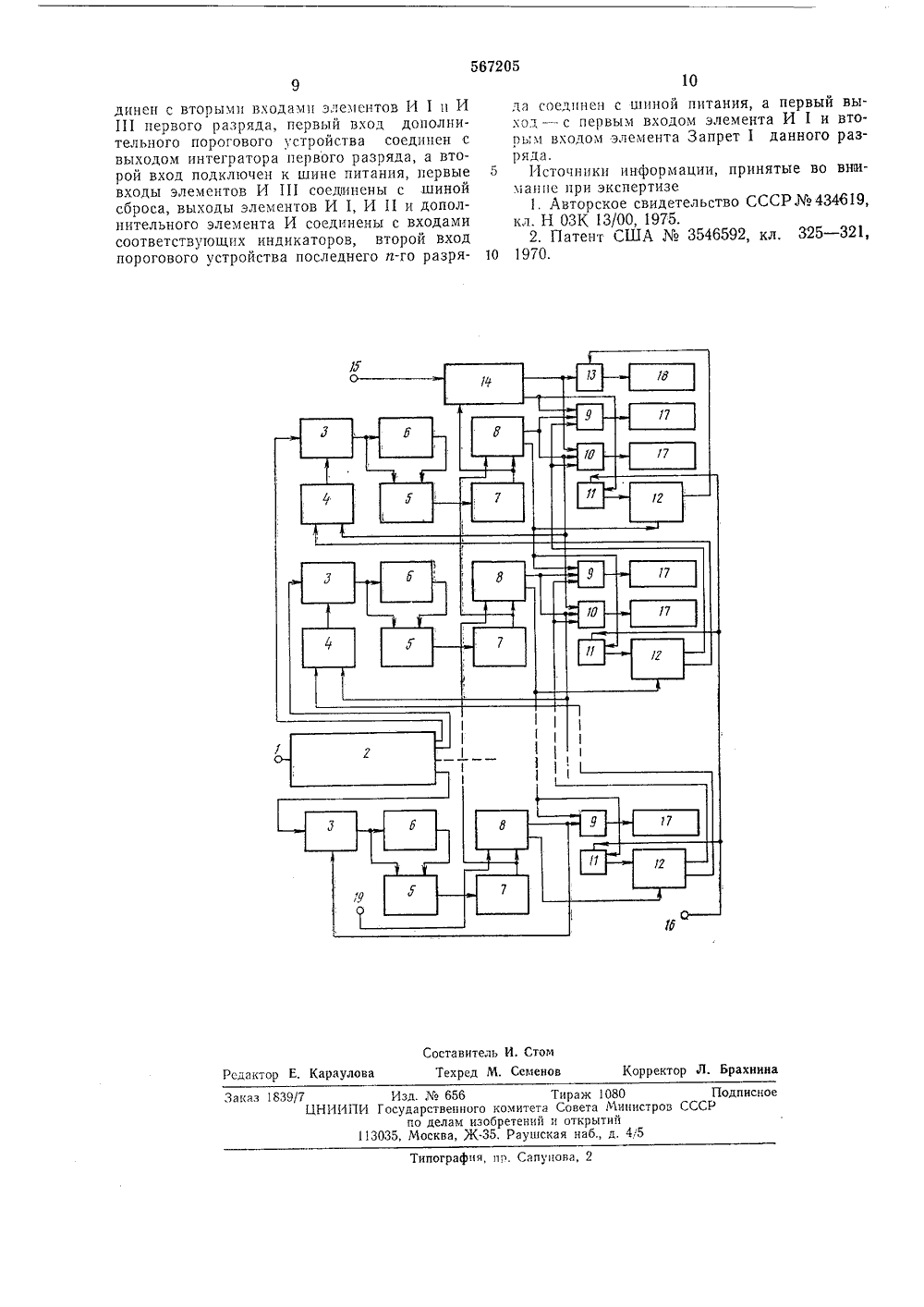

чтн"- ": ичч="нФ Я "Е5672 О 5 ОП ИСА 1 ИЗОБРЕТЕНИЯ Союз Советских Социалистических Республик(51) М, Кл.- Н 1) 213062 злено 28.04.7 аявки Ме присоединением Госуаарственньи комитет Совета Министров СССР лоделам изобретенийи открытий 23) Приоритет публиковано 30,07.77. ата опубликования опи ллетец ко 2ния 25.08.77 53) УДК 681.325(088 72) Авторы изобретения Цевчу н и 71) Заявитель(54) УСТРОЙСТВО СТАТИСТИЧЕ ЦИФРОВОГО ПРЕОБРАЗОВАТЕЛ Изобретение относится к областям техники, связанным с импульсно-кодовой модуляцией и цифровой вычислительной техникой.Внедрение систем связи, предназначенных для передачи телевизионного сигнала мето дом импульсно-кодовой модуляции, совершенствование методов обработки изображений на ЭЦВМ обусловливают высокие требования к точности аналого-цифрового преобразователя (АЦП) и стабильности его работы в процес се длительной эксплуатации. Поэтому возникает задача контроля точности аналого-цифрового преобразования.Известно устройство контроля ЛЦП сигналов изображения, в котором на вход контро лируемого АЦП подается пилообразное напряжение. Выходы разрядов АЦП поочередно подаются на вход видеоконтрольного устройства, на экране которого возникает изображение кодовой таблицы того кода, с которым 20 работает проверяемый преобразователь 11.Недостатком такого контроля является нарушение функционирования АЦП в системе. Кроме того, контроль осуществляется визуально и поэтому точность его невысокая. 2Наиболее близким по технической сущноспи к предлагаемому является устройство, осуществляющее контроль частоты появления нулей в каждой паре соседних разрядов внутри кодовой группы при реальном информа:1 ГО КОНТРОЛЯ АНАЛОГО- И ГНАЛОВ ИЗОБРАЖЕН ИЯ ционном сигнале на входе АЦП, в котором выход аналого-цифрового преобразователя через преобразователь параллельного кода в последовательный и линию связи соединен с входом преобразователя последовательного кода в параллельный, выходы которого соединены с цифро-аналоговым преобразователем. Вход преобразователя последовательного кода в параллельный через элемент И, устройство задержки, второй элемент И соединен с входом интегратора. Вход преобразователя через элемент И - НЕ соединен с вторым входом второго элемента 1 Л. Выход интегратора через пороговое устройство и мультивибратор соединен с входом третьего элемента И, второй вход которого через выделитель тактовой частоты соединен с входом преобразователя последовательного кода в параллельный. Выход третьего элемента И соединен с входом цифрового счетчика. Выходы второй и третьей ячеек цифрового счетчика соединены с вторыми входами первого элемента И и элемента И - НЕ соответственно. Выходы всех ячеек цифрового счетчика соединены с управляющими входами преобразователя последовательного кода в параллельный 12.Однако в рассмотренном устройстве: - не контролируется функциоц каждого разряда в отдельности;- контроль производится лишь прп нормальном законе распределения значений сигнала, подвергаемого аналого-цифровому преобразованию;- контроль производятся только при кодировании сигнала кодом Грея;- контроль производится путем последовательного опроса разрядов АЦП, что приводит к большим временным затратам.Цель изобретения - расширение функцио,нальных возможностей статистического контроля аналого-цифрового преобразователя сигналов изображения.Это достигается тем, что в устройство, содержащее аналого-цифровой преобразователь, вход которого соединен с шиной входного сигнала, устройство задержки, интегратор, выход которого соединен с первым входом порогового устройства, введены л элементов Запрет 1 (л - 1) эломентов Запрет П, (и - 1) устройств задержки, и сумматоров, (п - 1) интеграторов, (и - 1) пороговых устройств, и элементов И 1, (п - 1) элементов И 11, и элементов И 111, и триггеров, дополнительное пороговое устройство, дополнительный элемент И, 2 а индикаторов, причем выход каждого разряда аналого-цифрового преобразователя саединеи с первым входом соответствующего элемента Запрет 1, второй вход которого подключен к выходу элемента Запрет 11, а выход соединен с первым входом сумматора данного разряда и через устройство задержки данного разряда с вторым входом сумматора данного разряда, через интегратор данного разряда соединен с первым входом порогового устройства данного разряда и вторым входом порогового устройства предыдущего разряда, первый выход порогового устройства соединен с первыми входами элементов И 1 и И 11 данного разряда, первым входом элемента Запрет 11 данного разряда и вторым входом элемента И 11 последующего разряда, второй выход порогового устройства соединен с вторыми входами элементов И 1 и И 111 последующего разряда ы первым входом триггера данного разряда, второй вход которого подключен к выходу элемента И П 1 данного разряда, первый выход триггера соединен с вторым входом элемента Запрет 11 предыдущего разряда, второй выход триггера соединен с третьими входами элементов И 1 и И 11 предыдущего разряда, причем выход триггера первого разряда соединен с первым входом дополнительного элемента И, второй вход которого соединен с вторым входом элемента И 11 первого разряда и первым выходом дополнительного порогового устройства, второй выход которого соединен с вторыми входами элементов И 1 и И 111 первого разряда, первый вход дополнительного порогового устройства соединен с выходом интегратора первого разряда, а второй вход подключен к шине питания, первые входы элементов И 111 соединены с шиной сброса, выходы элементов И 1, И 11 и дополнительного элемента И соединены с входами 5 Ю 15 20 25 30 35 40 45 50 55 60 б 5 соответствующих индикаторов, второй вход порогового устройства последнего и-го разряда соединен с шиной почитания, а первый выход - . с первым входом элемента И 1 и вторым входом элемента Запрет 1 данного разряда.На чертеже показана структурная электричеслая схема предлагаемого устройства статистического контроля аналого-цифрового преобразователя сигналов изображения,Шина 1 входного сигнала через АЦП 2 соединена с входом каждого из и элементов Запрет 1 3, Второй вход каждого элемента Запрет 1 3 подключен к выходу элемента Запрет 11 4, а выход соединен с первым входом сумматора 5 данного разряда и через устройство 6 задержки данного разряда с вторым входом сумматора 5 данного разряда. Выход сумматора 5 через интегратор 7 данного разряда соединен с первым входом порогового устройства 8 данного разряда и вторым входом порогового устройства 8 предыдущего разряда, Первый выход порогового устройства 8 соединен с первыми входами элементов И 1 9 и И П 10 данного разряда, первым входом элемента Запрег 11 4 данного разряда и вторым входом элемента И 11 10 последующего разряда, Второй выход порогового устройства 8 соединен с вторыми входами элементов И 1 9 и И 111 11 последующего разряда и первым входом триггера 12 данного разряда, Второй вход триггера 12 подключен к выходу элемента И 111 11 данного разряда, Первый выход триггера 12 соединен с вторым входом элемента Запрет 11 4 предыдущего разряда, а второй выход триггера 12 соединен с третьими входами элементов И 1 9 и И 11 10 предыдущего разряда. Первый выход триггера 12 первого разряда соединен с первым входом дополнительного элемента И 13, Второй вход дополнительного элемента И 13 соединен с вторым входом элемента И 11 10 первого разряда и первым выходом дополнительного поротовото устройства 14. Второй выход дополнительного порогового устройства 14 соединен с вторыми входами элементов И 1 9 и И 111 11 первого разряда, первый вход соединен с выходом интегратора 7 первого разряда, а второй вход аодключен к шине 15 питания. Первые входы элементов И 111 11 соединены с шиной 16 сброса, Выходы элементов И 1 9 и И 11 10 и дополнительного элемента И 13 соединены с входами соответствующих индикаторов 17 и 18. Второй вход порогового устройства 8 последнего и-го разряда соединен с шиной 19 питания, а первый выход - с первым входом элемента И 1 9 и вторым входом элемента Запрет 1 3 данного разряда.Устройство работает следующим образом.Телевизионный вещательный сигнал по шине 1 входного сигнала поступает на вход АЦП 2. Кодовые импульсы с выхода 1, 2 и-го разряда АЦП 2 поступают соответственно на вход 1, 2 п-го элемента Запрет 1 3. При наличии разрешающего потенциала на(5) 5 10 15 20 Е,(У,(У,;Ус (У,)% д Ут (У) Е,. 25 60 65 втором входе элемента Запрет 1 3 данного разряда кодовые импульсы через элемент Запрет 1 3 поступают на первый вход сумматора 5 ло модулю два данного разряда и через устройство 6 задержки данного разряда на второй вход сумматора 5. Устройство 6 задержки осуществляет задержку кодовых импульсов на один такт, т. е. на период временной дискретизации вещательного телевизионного сигнала, производимой в АЦП 2. На выходе сумматора:5 возникает логическая 1,при несовпадении двоичных сигналов на его входах, Таким образом, частота появления 1 на выходе сумматора 5 пропорциональна частоте изменения посылок 0 в 1 или 1 в 0 в цепи данного разряда АЦП 2. С выхода сумматора 5 сигнал поступает на интегратор 7, напряжение У; на выходе которого пропорционально вероятности появления 1 на выходе сумматора 5. С выхода интегратора 7 сигнал поступает на первый вход порогового устройства 8 данного разряда и второй вход порогового устройства 8 предыдущего разряда, На второй вход порогового устройства 8 данного разряда подается сигнал с выхода интегратора 7 лоследующето разряда. При нормальной работе а-разрядното АЦП 2 для напряжений на выходе интеграторов 7 должно выполняться соотношениеЕ,(У,(Уз ((У(У - (У, (1) поскольку аналогичное соотношение можно записать для вероятностей изменения посылок Р, в цепях соответствующих разрядов АЦП 2:О(" ( а(" ( (5"( и - ( л( (2) Соотношения (1) и (2) связаны со статистическими свойствами сигналов изображе,ния, подвергаемых аналого-цифровому преобразованию, отличительной особенностью которых является сильная корреляционная связь между соседними значениями сигнала. Таким образом, вероятность скачка в сигнале с ростом величины скачка падает практически по экспоненте, Для переключения старшего разряда (например, 1-го) АЦП с меньшей частотой, чем у младщего (например, 2-го), надо, чтобы скачки большой величины происходили реже, чем скачки малой величины. Это выполняется для сигнала изображения и приводит к возникновению соотношенийи (2).В зависимости от соотношения напряжений на интеграторах 7 можно рассмотреть три режима работы устройства.. Первый разряд функционирует нормально: Е (У,(У (з) где Е - напряжение на шине 15 питания; 1-ый разряд функционирует нормально;где Ег - напряжение на шине 9 питания.В этом случае с первого выхода порогового устройства 8 данного разряда логический 0 поступает на первые входы элементов И 1 9 и И 11 1 О данного разряда, второй вход элемента И 11 10 последующего разряда и на первый вход элемента Запрет 11 4 данного разряда. С выхода элемента Запрет 11 4 логический 0 поступает на второй вход элемента Запрет 1 3 данного разряда. Таким образом, кодовые импульсы данного разряда беспрепятственно проходят через элемент Запрет 1 3, а соответствующие индикаторы 17 и 8, в качестве которых можно использовать светодиоды, не горят.2. На выходах АЦП 2 возникают дополнительные переходы 1 - 0 или 0 1: В. этом случае пороговое устройство 8 данного разряда срабатывает, и логическая 1 с его первого выхода поступает на первые входы соответствующих элементов И 1 9 и И 11 О, На вторые входы элементов И 1 9 и И 11 1 О поступают соответственно логические 1 и 0 с первого и второго выходов порогового устройства 8 предыдущего разряда. Таким образом, через элемент И 1 9 логическая 1 поступает на индикатор 17, который загорается, указывая на возникновение дополнительных переходов 1 - 0 или 0 -в данном разряде. Одновременно логическая 1 с первого выхода порогового устройства 8 данного разряда через элемент Запрет 11 4 поступает на второй вход элемента Запрет 1 3 данного разряда. Кодовые импульсы перестают проходить через элемент Запрет 1 З,элемент Запрет 11 4 или сумматор 5. Пороговое устройство 8 данного разряда переключается в исходное состояние, индикатор 17 гаснет, кодовые импульсы снова беспрепятственно проходят через элемент Запрет 1 3, Напряжение на интеграторе 7 снова начинает возрастать, что приводит к срабатыванию порогового устройства 8 и индикатора 17, и т. д. Таким образом, индикатор 17, мигая, указывает на дополнительные переходы в -м разряде, а напряжение У; на выходе интегратора 7 данного разряда автоматически поддерживается в соответствии с соотношениемУ (У,=%+. Колебательный процесс продолжается доустранения неисправности в цепи данногоразряда и восстановления соотношенияЫ (У,(Ы+т.3, На выходах АЦП 2 происходит недопу5 10 15 стимое уменьшение числа перехода 1 - 0 или0 - 1: Е,)У,(У,;Ы - 1 г Ы+Ь 1(Ы - 2. - ) п(Ез п(п -В этом случае пороговое устройство 8 данного разряда остается в исходном положении, а срабатывает пороговое устройство 8 предыдущего ( - 1)-го разряда, так как для него нарушается соотношение У;) У; ь При этом в цепи предыдущего разряда возникает колебательный процесс, аналогичный описанному выше для цепки данного разряда, и автоматически поддерживается соотношение У; -Сг(г - 2. Соотношение Уг - 1(Ут - 2 приводит к срабатыванию порогового устройства 8 в цепи ( - 2)-го разряда. При этом логические 1 и О соответтсвенно с первото и второго выходов порогового устройства 8 ( - 2)-го разряда поступают на вторые входы элементов И 1 9 и И 11 10 в цепи ( - 1) -го разряда, и сигнал с первого выхода порогового устройства 8 в цепи ( - 1) - ,го разряда поступает через элемент И 11 10 в цепи ( - 1)-го разряда на индикатор 18, который указывает на недопустимое уменьшение числа переходов 1 - 0 или 0 - 1 в данном -ом разряде,Срабатывание порогового устройства 8 в цепи ( - 1)-го разряда устанавливает соответствующий триггер 12 в такое состояние, что логический 0 с его второго выхода подается на третьи входы элементов И 1 9 и И 11 10 в цепи ( - 2)-го разряда, препятствуя тем самым срабатыванию индикатора 17 в цепи ( - 2)-го разряда от логической 1 на первом выходе порогового устройства 8 в ( - 2)-м разряде, Логическая 1 с первого выхода триггера 12 в цепи ( - 1) -го разряда поступает на второй вход схемы Запрет 11 4 в цепи ( - 2) -го разряда, тем самым разрывая петлю обратной связи в цепи ( - 2) -го разряда. Таким образом, пороговое устройство 8 в цепи ( - 2)-го разряда после срабатывания остается в этом состояниями до восстановления исходных соотношений напряжений на выходах интеграторов 7 и обеспечивает устойчивую индикацию недопустимого уменьшения числа переходов 1 0 или 0 1 в -м разряде.После устранения неисправности соответствующая индикация прекращается. Однако для восстановления функциональных возможностей устройства необходимо установить триггер 12 в цепи (г - 1) -го и ( - 2) -го разрядов в исходное состояние. Для этого на их вторые входы через соответствующие элементы И 111 11 поступают импульсы сброса с шины 16. Элементы И 111 11 управляются сигналом с второго выхода порогового устройства 8 в цепи предыдущего разряда. Это необходимо для того, чтобы не произошло восстановления цепи обратной связи в цепи 20 25 30 35 40 45 50 55 60 65 8( - 2)-го разряда при сработавшем соответствующем пороговом устройстве 8, что может привести к ложной индикации.Индикация недопустимого уменьшения числа переходов 0 - 1 или 1 - 0 в первом разряде У(Е производится при логической 1 на первом выходе дополнительного порогового устройства 14 индикатором 18 прои отсутствии логического 0 на втором входе дополнительного элемента И 13,Таким образом, индикация недопустимого увеличения числа переходов 0 - 1 или 1 О производится индикаторами 17, а уменьшения - индикаторами 18. Формула изобретения Устройство статистического контроля аналогоцифрового преобразователя сигналов изображения, содержащее аналого-цифровой преобразователь, вход которого соединен с шиной входного сигнала, устройства задержки, интегратор, выход которого соединен с первым входом порогового устройства, отлич а ющ е ес я тем, что, с целью расширения функциональных возможностей, в него введены и элементов Запрет 1, (и - 1) элементов Запрет 11, (и - 1) устройств задержки, и сумматоров, (и - 1) интеграторов, (и - 1) пороговых устройств, и элементов И 1, (и - 1) элементов И 11, и элементов И 111, и триггеров, дополнительное пороговое устройство, дополнительный элемент И, 2 и индикаторов, причем выход каждого разряда аналого-цифрового преобразователя соединен с первым входом соответствующего элемента Запрет 1, второй вход которого подключен к выходу элемента Запрет 11, а выход соединен с первым входом сумматора данного разряда и через устройство задержки данного разряда с вторым входом сумматора данного разряда, через интегратор данного разряда соединен с первым входом порогового устройства данного разряда и вторым входом порогового устройства предыдущего разряда, первый выход порогового устройства соединен с первыми входами элементов И 1 и И 11 данного разряда, первым входом элемента Запрет 11 данного разряда и вторым входом элемента И 11 последующего разряда, второй выход порогового устройства соединен с вторыми входами элементов И 1 и И П 1 последующего разряда и первым входом триггера данного разряда, второй вход которого подключен к выходу элемента И 111 данного разряда, первый выход триггера соединен с вторым входом элемента Запрет 11 предыдущего разряда, второй выход триггера соединен с третьими входами элементов И 1 и И 11 предыдущего разряда, причем выход триггера первого разряда соединен с первым входом дополнительного элемента И, второй вход которого соединен с вторым входом элемента И 11 первого разряда и первым выходом дополнительного порогового устройства, второй выход которого сое567205 Составитель И, Стом Техред М. Семенов Корректор Л. Брахнина Редактор Е. Караулова Заказ 1839/7 Изд656 Тираж 1080 Подписное ЦНИИПИ Государственного комитета Совета Министров СССР по делам изобретений и открытий 113035, Москва, Ж.35, Раушская наб., д. 4/5Типография, пп. Сапунова, 2 9динен с вторыми входамп элементов И 1 и И 111 первого разряда, первый вход дополнительного порогового устройства соединен с выходом интегратора первого разряда, а второй вход подключен к шине питания, первые входы элементов И 111 соединены с шиной сброса, выходы элементов И 1, И 11 и дополнительного элемента И соединены с входами соответствующих индикаторов, второй вход порогового устройства последнего а-го разря 10да соединен с шиной питания, а первый выход - с первым входом элемента И 1 и вторым входом элемента Запрет 1 данного разряда.5 Источники информации, принятые во вн 1 имание при экспертизе1, Авторское свидетельство СССР Юв 434619,кл. Н ОЗК 13/00, 1975.2. Патент США Мо 3546592, кл. 325 в 3, 10 1970.

СмотретьЗаявка

2130628, 28.04.1975

ПРЕДПРИЯТИЕ ПЯ М-5619

КОГАН СЕМЕН САМУИЛОВИЧ, ШЕВЧУК АНАТОЛИЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: H03K 13/17

Метки: аналого-цифрового, изображения, преобразователя, сигналов, статистического

Опубликовано: 30.07.1977

Код ссылки

<a href="https://patents.su/5-567205-ustrojjstvo-statisticheskogo-kontrolya-analogo-cifrovogo-preobrazovatelya-signalov-izobrazheniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство статистического контроля аналого-цифрового преобразователя сигналов изображения</a>

Предыдущий патент: Преобразователь двоичного кода во временной интервал

Следующий патент: Аналого-цифровой преобразователь

Случайный патент: Устройство для записи информации на светочувствительный носитель