Самонастраивающаяся система регулирования

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 530657

Автор: Винфрид

Текст

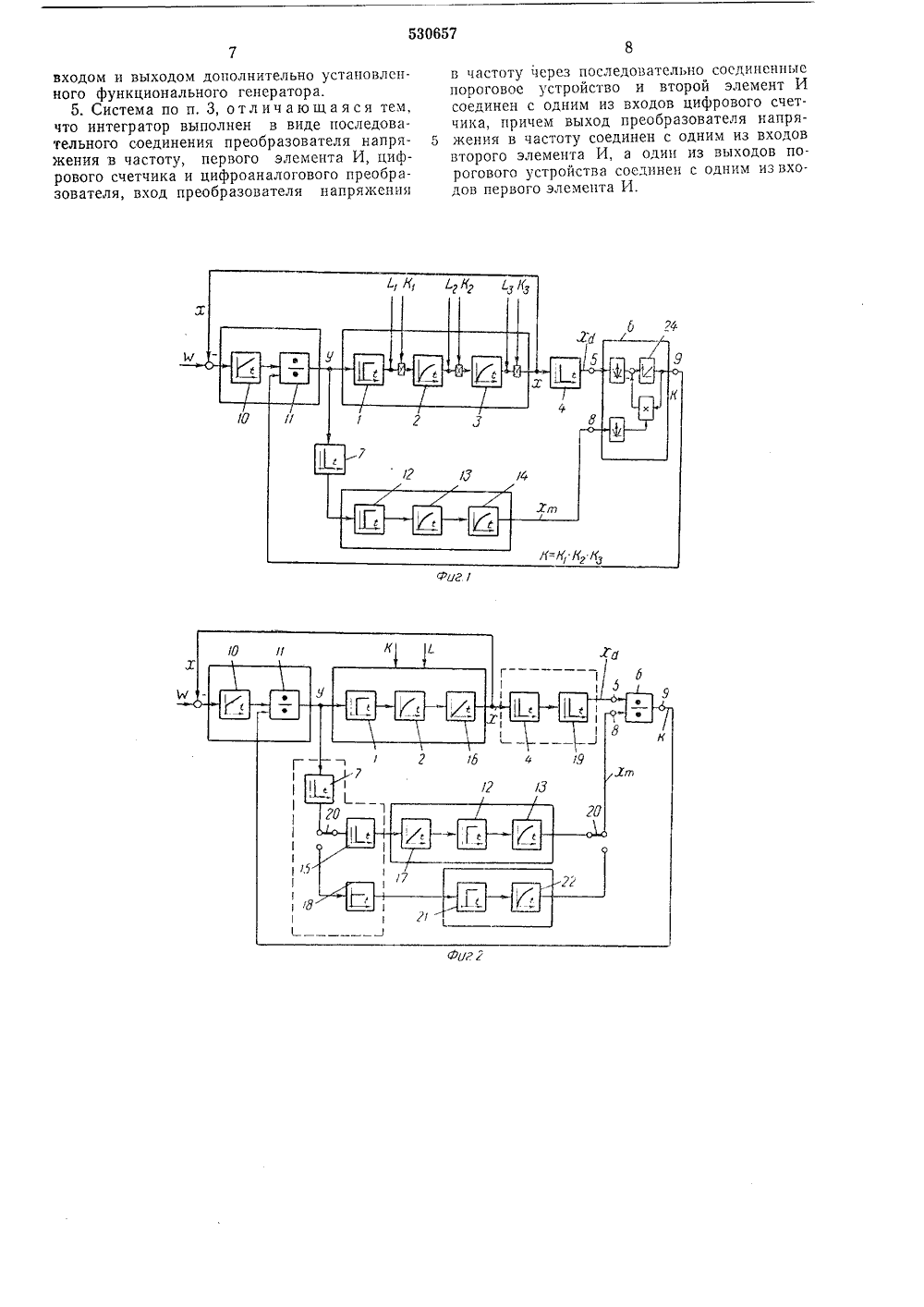

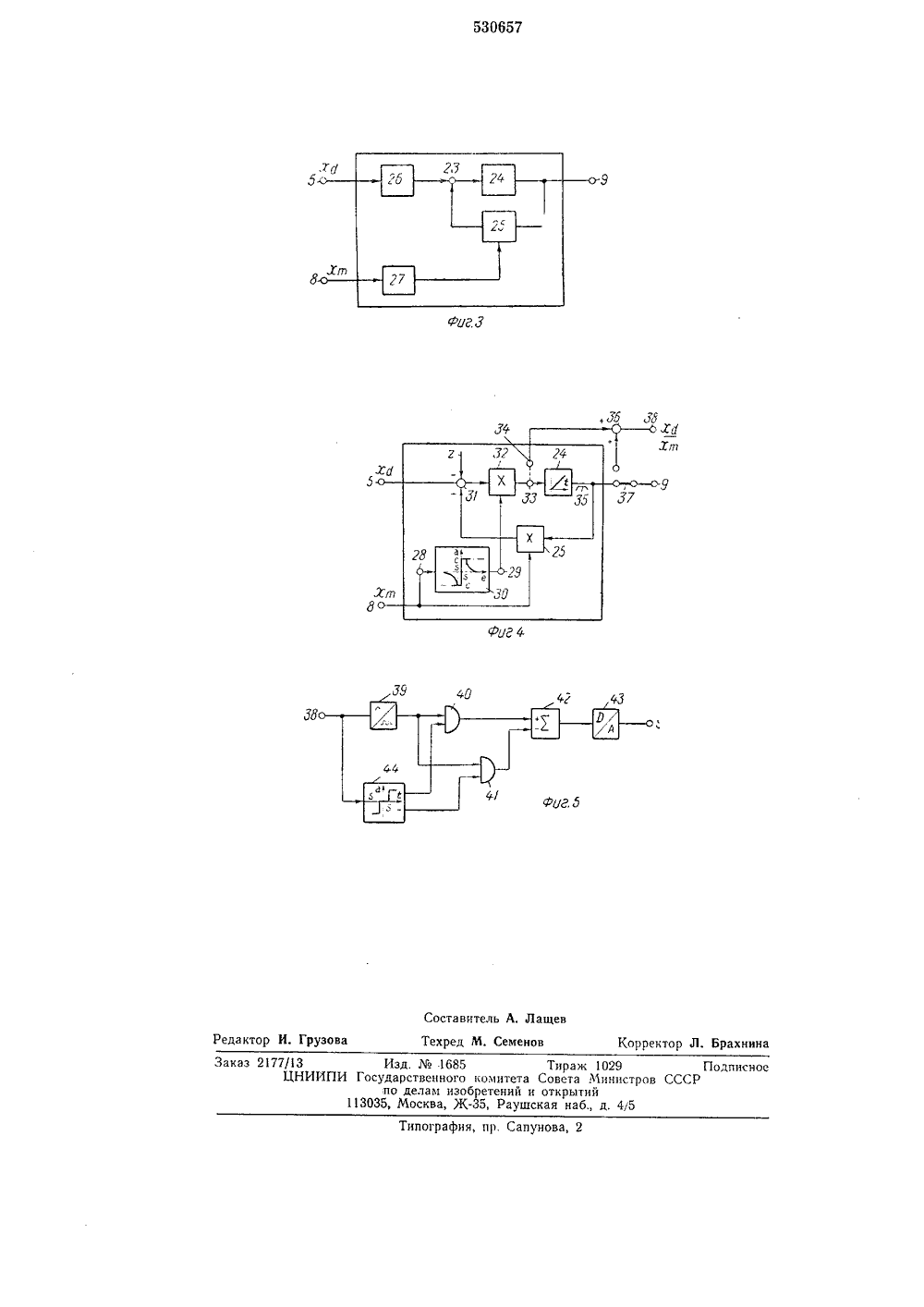

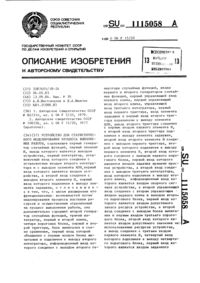

ОПИСАНИЕ ИЗОБРЕТЕНИЯ р 530657 Союз Советских Социалистических Республик.12.6РГ сударствеииын комитет вета Министров СССР о делам изобретенийи открытий УДК 62 - 50(088.8 тень М 36 та опубликования описания 20.10.7 72) Автор изобретени Иностранец Винфрид Шпет(ФРГ) ностранная фирь Сименс АГ1) Заявител Блок деления выполнен в виде последовательно соединенных первого определителя модуля, сравнивающего элемента и интегратора,выход которого соединен с одним из входов5 сравнивающего элемента через умножитель, ак одному из входов умножителя подключенвторой определитель модуля. Между сравнивающим элементом и интегратором установленвторой умножитель, один из входов первого и1 О второго умножителей связан соответственно свходом и выходом введенного дополнительнофункционального генератора.Интегратор изготовлен в виде последовательного соединения преобразователя напря 15 жения в частоту, первого элемента И, цифрового счетчика и цифроаналогового преобразователя. Вход преобразователя напряженияв частоту через последовательно соединенныепороговое устройство и второй элемент И20 связан с одним из входов цифрового счетчика. Выход преобразователя напряжения вчастоту подключен к одному из входов второгоэлемента И, а один из выходов пороговогоустройства - к одному из входов первого эле 25 мента И,Такое построение функциональной схемысамонастраивающейся системы повышает(54) САМОНАСТРАИВАЮЩАЯ Изобретение относится к области автоматики, в частности к самонастраивающимся системам регулирования с эталонной моделью.Известна самонастраивающаяся система регулирования, содержащая эталонную модель, первый блок деления и последовательно соединенные сумматор, усилитель и второй блок деления, выход которого соединен с входом объекта регулирования.Недостатком известной системы является низкая точность работы при мультипликативных помехах, воздействующих на объект регулирования.Предлагаемая самонастраивающаяся система регулирования отличается тем, что в ней установлены два блока упреждения, выход первого из которых через эталонную модель подключен к одному из входов первого блока деления, выход второго - к другому входу первого блока деления, выход которого соединен с одним из входов второго блока деления, а входы первого и второго блоков упреждения - соответственно к входу и выходу объекта регулирования.Блок упреждения представляет собой два последовательно соединенных дифференцирующих звена. ТЕМА РЕГУЛ ИРОВАНИпри воздействии на мультипликативных точность регулированияобъект регулированияпомех,На фиг. 1 и 2 изображена функциональная схема системы регулирования; на фиг. 3, 4 - блок деления; на фиг. 5 - функциональная схема интегратора.На схемах приняты следующие обозначения: о - сигнал регулирования; у - выходной сигнал регулятора; ха - сигнал с выхода объекта регулирования; х - сигнал с выхода эталонной модели; К - коэффициент усиления системы; К, Кь Кз - мультипликативные помехи; Е Ь Е, - аддитивные помехи; Л - постоянный дополнительный сигнал на входе блока деления. Система содержит следующие элементы, показанные на фиг, 1 - 5, где 1 - звено запаздывания объекта регулирования; 2, 3 - апериодические звенья объекта регулирования; 4 - блок упреждения; 5 - вход блока деления; 6 - блок деления; 7 - блок упреждения; 8 и 9 в вх и выход блока 6 деления; 10 - усилитель; 11 - блок деления; 12 - блок запаздывания эталонной модели; 13, 14 - апериодическис звенья эталонной модели; 15 - блок упреждения; 16, 17 - интеграторы; 18 - пропорциональное звено; 19 - блок упреждения; 20 - переключающий элемент; 21 - звено запаздывания эталонной модели; 22 - апериодический блок эталонной модели; 23 в элеме сравнения; 24 - интегратор; 25 - умножитель; 26 - первый определитель модуля; 27 - второй определитель модуля; 28 и 29 в вх и выход функционального генератора 30; 31 в элеме сравнения; 32 - умножитель; 33, 34 - перемычка;35 - пороговое напряжение на выходе интегратора; 36 в элеме сравнения; 37 в переключающий элемент; 38 - вход интегратора;39 - преобразователь напряжения в частоту;40, 41 - элементы И; 42 - цифровой счетчик импульсов; 43 - цифроаналоговый преобразователь; 44 - пороговое устройство,Самонастраивающая система работает следующим образом.На вход регулятора подается сигнал регулирования, который сравнивается с сигналом х с выхода объекта регулирования, а на вход его поступает сигнал с выхода регулятора х. Кроме того, на объект регулирования непосредственно воздействуют аддитивно наложенные помехи Е Ь Ез и мультипликативно наложенные помехи Кь К и Кз, причемтолько последние изменяют усиление в прямой цепи регулирования, Представим объект регулирования последовательно соединенными звеном 1 запаздывания и двумя апериодическими звеньями 2 и 3 (фиг. 1), Блок 4 упреждения не пропускает аддитивные помехи , Ьь 1.з Установка упреждающего блока 7 позволяет обеспечить одинаковые фазовые сдвиги сигналов х, и х, отношение которых хд/х пропорционально произведению К=К К Кз, которое необходимо скомпенсировать пу тем подачи на блок 11 делениях,/х,отношения На фиг. 2 представлен вариант выполненияфункциональной схемы системы регулирова 5 ния, когда объект регулирования вместо одного апериодического звена 3 содержит интегратор 16, и соответствующее этому случаю выполнение блоков 4 и 7 упреждения, состоящих из последовательно соединенных дифференци рующих звеньев.На фиг. 3 представлена схема блока 6 (11)деления. Сигналы х и ха проходят соответственно через первый 26 и второй 27 определители модуля, умножитель 25. Интегратор 24 15 позволяет запомнить значение сигнала на выходе блока деления при исчезновении сигналов х и хт.На фиг. 4 изображена другая функциональная схема выполнения блока деления. Работа 20 его осуществляется следующим образом: сигнал с выхода объекта регулирования поступает в элемент 31 сравнения, затем через умно- житель 32 подается в интегратор 24, а с выхода интегратора 24 через умножитель 25 по ступает на элемент 31 сравнения, где сравнивается с дополнительным постоянным сигналом г и с выходным сигналом ха.На вход умножителя 25 поступает сигналх с эталонной модели, а на вход умножителя 30 32 подается также сигнал х, но пропущенный через функциональный генератор 30. Наличие интегратора 24 в данной схеме, как и в схеме, изображенной и на фиг. 3, позволяет запомнить значение сигналов на выходе бло ка деления при исчезновении сигналов хих. В отличие от предыдущей схемы блока деления, изображенной на фиг. 3, здесь на входной контур и на контур отрицательной обратной связи действуют не действительные 40 значения величин ха и х а алгебраические величины +ха и +х с учетом знака.Поэтому в данном случае имеющаяся во входном сигнале высокочастотная составляющая шумовых помех подавляется интеграто ром 24, поскольку обратное значение времениинтегрирования Т, достаточно мало по отношению к имеющимся высокочастотным шумам, хотя последние, как правило, всегда имеют место. Так как сигналы х и х могут 50 иметь разные знаки, то при изменении знакасигнала х, которое происходит одновременно с изменением полярного сигнала ха (оба эти сигнала синфазны), изменяется и знак входного сигнала интегратора 24. Знак на правления регулирования системы, состоящейиз интегратора 24, умножителей 32 и 25, не меняется. Смена знака входного сигнала интегратора осуществляется с помощью функционального генератора 30.60 Для обеспечения правильного направлениярегулирования функциональный генератор 30 должен был бы выполнять только функцию смены знака входного сигнала хи его характеристика могла бы быть линейной, на пример, как у инвертирующего усиления.530657 5 1 О 15 20 25 35 40 45 50 55 бО 65 5В данном случае функциональный генераторимеет гиперболическую характеристику, чтообеспечивает постоянное время идентификации сигнала.Если во время процесса регулирования величина сигнала с выхода регулятора у остается продолжительное время неизменной, товеличины сигналов ха и х стремятся к нулю,Если интегратор 24 реализован посредствоманалоговых устройств (например, электронного усилителя с емкостной отрицательнойобратной связью), то наблюдается дрейфего выходного напряжения, Для избежаниядрейфа выходного сигнала на элемент 31сравнения подается постоянный дополнительный сигнал г, который позволяет на выходеинтегратора 24 иметь всегда какое-то небольшое опорное напряжение (35).Это опорное напряжение может быть реализовано известными способами, например спомощью ограничивающих диодов на выходеинтегратора 24. Сигнал г идентифицируетдействительное значение коэффициента усиления цепи регулирования, уменьшая приэтом усиление регулятора до определенногозначения, которое необходимо для оптимального процесса регулирования так, что в этомслучае предотвращается нестабильность контура регулирования. Тем самым достигаетсяболее быстрое регулирование при отклонениях сигналов от заданных значений, чем прирегуляторе, коэффициент усиления которогоподогнан к цели регулирования.Если неооходимо, чтобы отношение ха/х,имелось в цепи регулирования постоянно, ане дискретно, то можно использовать другойвариант исполнения делителя, изображенногона фиг. 4.Поставим перемычку ЗЗ и 34, а переключающий элемент 37 установим в вертикальноеположение, Тогда сигнал с выхода интегратора 24 поступает на элемент 36 сравнения.Принимая во внимание гиперболическое преобразование в функциональном генераторе30, появляющийся на сравнивающемся элементе 36 сигнал равен х/х - К, где К - выходной сигнал интегратора 24 на данный момент.Если, следовательно, к этому сигналу прибавить выходной сигнал интегратора 24, тона выходе делителя напряжения в любой момент имеется напряжение х/хСледовательно, в этом случае достигаетсякак идентификация выходного сигнала, так исохранение его при исчезновении сигналовха и х.На фиг. 5 изображена схема интегратора сприменением цифровых элементов.Она состоит из преобразователя 39, преобразующего синусоидальное напряжение в импульсное, частота которого пропорциональнасинусоидальному. Сигналы с преобразователячастоты подаются на одни входы элементовИ, на другие входы которых приложены выходные сигналы порогового устройства 44.Задача этого порогового устройства состоит в запирапии элементов И 40 и 41, если амплитуда напряжения, приложенного к входу 38 интегратора лежит ниже порога срабатывания. Когда входное напряжение выше порога срабатывания, то импульсы с элементов И 40 и 41 проходят в цифровой счетчик 42. Выход элемента И 40 подведен к считающему входу счетчика 42, действующего в обоих направлениях, и выход элемента И 41 - к его же входу. считающему в обратном направлении, и питает его при отрицательных амплитудах приложенного к входу 38 входного напряжения. Считающий в обоих направлениях счетчик 42 действует как цифровое запоминающее устройство, и его выходная величина преобразуется в цифроаналоговом преобразователе в напряжение сигнала, которое появляется затем на выходе 9.Таким образом, изобретение позволяет самостоятельно противодействовать отклонению усиления цепи от заданного значения. Кроме того, можно с самого начала предварительно установить коэффициент усиления системы на какую-то величину, не зная реального коэффициента усиления. При этом целесообразно выбирать коэффициент усиления в ожидаемых пределах усиления. Формула изобретения 1. Самонастраивающаяся система регулирования, содержащая эталонную модель, первый блок деления и последовательно соединенные сумматор, усилитель и второй блок деления, выход которого соединен с входом объекта регулирования, о т л и ч а ю щ а я с я тем, что, с целью увеличения точности регулирования при воздействии на объект регулирования мультипликативных помех, в ней установлены два блока упреждения, выход первого на которых через эталонную модель соединен с одним из входов первого блока деления, а выход второго - с другим входом псрвого блока деления, выход которого соединен с одним из входов второго блока деления, а входы первого и второго блоков упреждения соединены соответственно с входом и выходом объекта регулирования,2. Система по п. 1, о т л и ч а ю щ а я с я тем, что блок упреждения выполнен в виде последовательно соединенных двух дифференцирующих звеньев.3, Система по пп. 1 и 2, отличающаяся тем, что блок деления выполнен в виде последовательно соединенных первого определителя модуля, сравнивающего элемента и интегратора, выход которого соединен с одним из входов сравнивающего элемента через умно- житель, а к одному из входов умножителя подключен второй определитель модуля.4, Система по и. 3, отл и ч а юща яся тем, что в блоке деления между сравнивающим элементом и интегратором установлен второй умножитель, один из входов первого и второго умножителей соединен соответственно свходом и выходом дополнительно установленного функционального генератора.5. Система по п, 3, отличающаяся тем, что интегратор выполнен в виде последовательного соединения преобразователя напряжения в частоту, первого элемента И, цифрового счетчика и цифроаналогового преобразователя, вход преобразователя напряжения в частоту через последовательно соединенные пороговое устройство и второй элемент И соединен с одним из входов цифрового счетчика, причем выход преобразователя напря жения в частоту соединен с одним из входоввторого элемента И, а один из выходов по- Р огового устройства соединен с одним из входов первого элемента И.

СмотретьЗаявка

1368165, 16.10.1969

ВИНФРИД ШПЕТ

МПК / Метки

МПК: G05B 13/02

Метки: самонастраивающаяся

Опубликовано: 30.09.1976

Код ссылки

<a href="https://patents.su/5-530657-samonastraivayushhayasya-sistema-regulirovaniya.html" target="_blank" rel="follow" title="База патентов СССР">Самонастраивающаяся система регулирования</a>

Предыдущий патент: Шлакоудалитель

Следующий патент: Аппарат для обучения методам оживления

Случайный патент: Способ удаления покрытий с титановых электродов