Генератор векторов для системы отображения графической информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 525980

Автор: Лыков

Текст

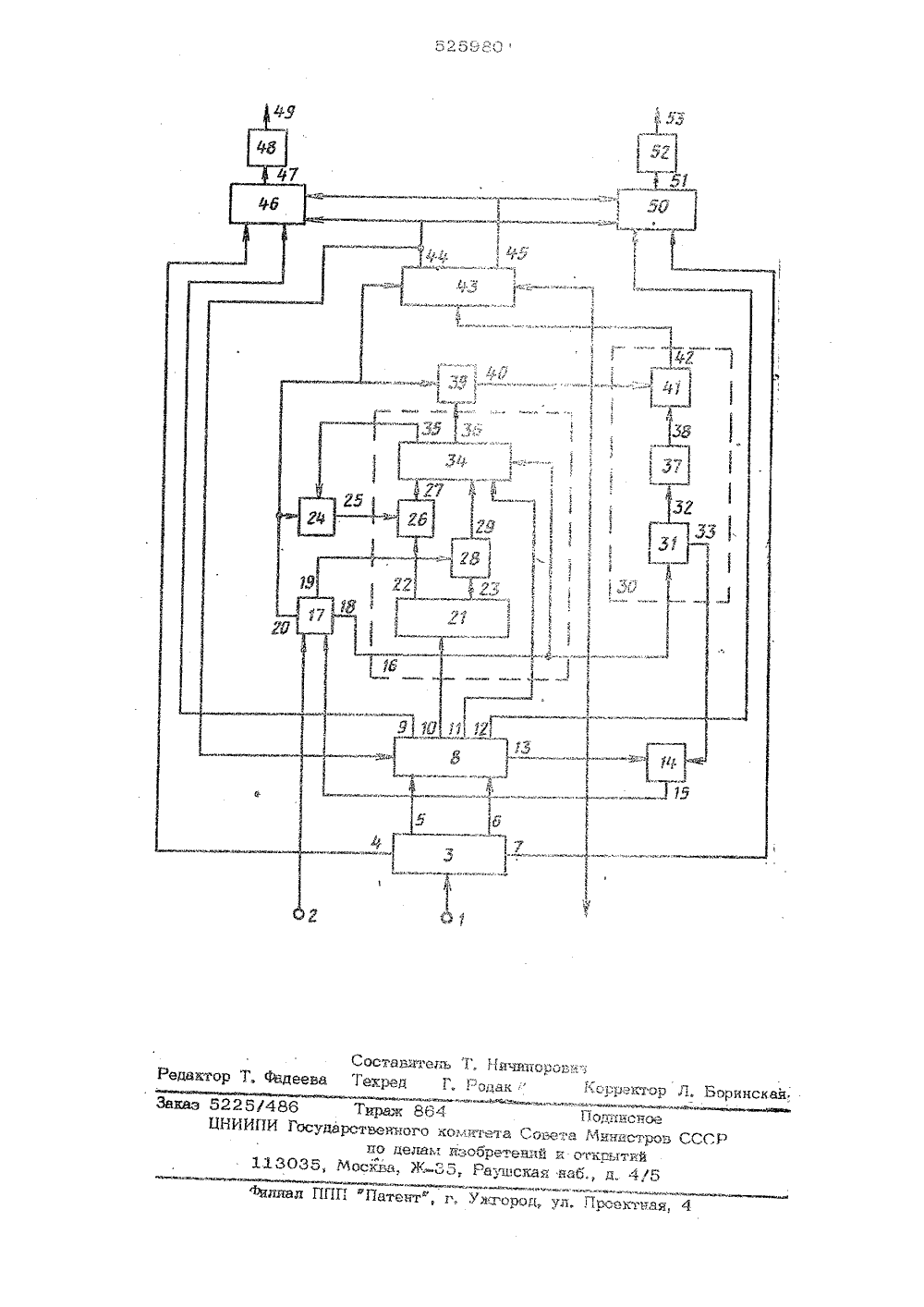

Союз Советских Социвлистическин Республик(51) М, 1 л. Ь 06 К 15/2 Гасударственный номи Саветв Министрав СС па делам изобретении н открытий(45) Дата опубликования писания 19,11,76(72) Ав Лыко зобретения 71) Заявитель Объединенный институт ядерных исследован(54 ЕРАТОР ВЕКТОРОВ ДЛЯ СИСТЕМЫ ОТОБРАЖЕНИЯ ГРАФИЧЕСКОЙ ИНФОРМАЦИИ н 5 Изобретение относится к вычислительной технике и может быть использовано в информационно-вычислительных системах и автоматизированных системах управления.Известны генераторы векторов для системы отображения графической информации содержащие приемный регистр, выходы приращений координат которого подключены ко входам коммутатора, в выходы знаков приращений - ко входам управления реверсом 101счетчиков координат, выходы которых соединены с цифро-аналоговыми преобразователями, счетные входы - с выходами цифрово го интерполятора, в входы блокировки счетами соответственно с первым и вторым выходами коммутатора, третий выход которого подключен к управляющему входу цифрового интерполяторв и через элемент ИЛИ - ко вхо-ду генератора тактовых импульсов, первйй выход которого соединен через распредели тель импульсов со входами цифрового интерполяторв, груптьт вентилей и элементы И,Генератор векторов содержит также по. стоянное звпоминатощеь устрюйство, преднв внвченное для записи и хранения ходов та 2генсов углов воспроизводимых линий, Наличие постоянного запоминающего устройства не соответствует требованию единой элемент ной базы, усложняет ,устройство в целом, повышает его стоимость. При этом построение длинных векторов из нескольких коротких, соединяемых последовательно, требует большей памяти ЭВМ, увеличивает число об ращений к ЭВМ и усложняет программирование, Поэтому необходимо иметь воэможность вычерчивать длинные векторы по одному зна чению координаты приращения, а не сумме приращений коротких векторов. Увеличение же разрядности адресов ( Ь Х,аУ ) постоянного запоминающего устройства увеличивает емкость постоянного запоминающего устройства и количество оборудования, применяемо го для его возбуждения. Так, например, йри тт разрядных адресах постоянного запоминающего устройства число возможных углов а значит и значений тангенса только для углов с фиксированной одной стороной, эртелей максимальному приращению, составит откуда емкость постоянного запоминающего .устройства для этих значений - и Рбит.525 Зто только Некоторая часть требуемой емкОсти постояББОГО запОминаюшеГО стройства.1.18 Л 1 ИЗОбрЕтення. уПроСТИТЬ ГЕНератор и сократить изоыто 1 ность информ 1 дии при 06- МОНО С ВБСБББМИ СТРОЙ 1 СТВЙМИ.Это достигается тем, что генератор содержит цифровой блок делениясостоящий из регистра делимого и регистра делителя, выходы прямОГО и Обратного кода кОторОГО подключены через соответству 1 ошие группы 1 О вентилей ко входам регистра делимого, знаКОВЫ 8 ВЫХОДЫ КОТОРОГО СО 8 ДИБ 8 БЫ С ОДНИМИ из входов элементов И, причем второй вы- ХОД ГЕБСраТОрй ТЙКгОВЫХ БЛП 1 уЛЬСОВ ПОДКЛКЪ ЧЕЧ КО ВХОДЙМ ОДНОЙ ИЗ 1 Ртттппт ВЕНТИЛЕЙ а ТРЕТИН - К И 1 ПУЛт 1 СБОЛ 1 У ВХОДУ ЦИЩГОВОГО ИН ТЕрцоляготта т 1 др,гГИМ Вт ОДЙМ ЗЛЕМет 1 ТСгв И ВЬГХОД ОДНОГО ИЗ КОТОРЫХ СОЕДИБен СО ВХС- ДЙМИ ДРУГОЙ ГРУЛтПЫ Вентнлейг а ВЫХОД ДЯ ГОГО ЭЛОМецта И - С допотт 1 жтелвн 1.1 Л 1 ВХОЛОМрр РЙС 1 Ц 81 Кд 11 ите 11 Я ИМПУЛЬСОВ,т тПЙ ЧергеЖЕ Дана б;101 т.-СХек;Й ПрРДЛЙ 1 лае- мого Генератора векторов, Где 1 - вход координат 11 рирйшеций Вектора; 2 - Вход з- пУскаюшего ил 4 БУ 1 цса; 3 - БРисмгпий Р 81 г",СТРДЬ 4 щщ Выход знака прирац;ения А х; 5- Выщф ходы,разрядон при 1 аше 1 Н 1 Я 1 х; 6 - Выходы разрядов 11 рира 1 тения . 1, з7 - Выход знака прирашеиия ь; 8 - 110 л 1 муг Йг Ор щ 11- РаЩЕНИй КООРДИНат. 9 - ВЬ:ХОД КОММУтатОРаг 4 О УПРав 11 КОШИЙ ПРИЕМОМ В КООРД 11 тнатЬ 1 Й Сх 181- ЧИК Х Ч 11 СЛО, ИМПУЛЬСБгГО КОДЙ .1 Х С ВЫ . хОдОВ цифроВ 010 1 птеопОлятовй 1 т 1 Выходы бол 1 ШОГО Пр 1 раШЕБия; 13. -ВЫХОДЫ М 8 БЬШ 8 ГО приранпдция 1 9 гт,тхгогг ,огьттч 11 сра лтг 1 т -тц Я ЛЯЮЩИЙ ПРИЕМОВ КООРДГ 111 ЙТН 1 Й СЧ 81 ЧИК У П 1 СЛО И ГНУЛ ОНОГО К 01 та, т г Выхг;тгов цифроВ 010 11 ИТтзртп;1 Б 4 г отргат,"1 3 "- ВЫХОД П 1 ИЗНЗ". КЙ конца Веетова" 1 4 СООИ 1 ссглелт- Рая г"ХЕМВ ИЛИ 15 " ВыхОд собирсчтел 1 Б 011 Скемь 16 ы 4 О цифровОЙ бт 0 к 118 летн 1 Я, 17 - . Гецегаатор тйк" ТОвых импульсОВ; = 8 ВыхОд первого так ТОВОГО ИМПуЛЬСЙ Ген 8 РЙТОРЙ ттКТОВЫХ ИМБУтц СОВ; 19 т- ВЫХОД ВТОРОГО ТЙКТОВОГО ИМПУЛЬСЙ ГЕцератора Тг 1;ТОВЫХ г 1 М 1 тггьсоВ 20, В 11 Ход В ТР 8 ТЬЕГО Тактевгт 1 СИМПУЧг Са Г 81 тРЙттглтта лц ТОВЫХ; Итг 1 птл 1 ОВ" , 1 сл 1)81 ИСТР Д 81 И 1 теЛЯу 22 - , выхгздьт 1 пртгмогст кода делителя:Выходы обратного кода делителя; 24 - элемент И; 25 - Выход злемента"А 26 - гргуп-ф Па ВВБТИЛЕЙ Пряг Лг 1 т,тО ЕОДЙ ДЕЛИТ 8 ЛЯ; 2 тгтВЫ- ходы вентилей поял 1 ОГО кода Делите 1 т 1; 2 8 ГРУППЙ ВВБТБЛЕЙ ОбЙТНОГ кона ДЕЛИТ 8 ЛЯ;29 - выходы вентилей обоатпого кода делиТЕЛя" 30 - расптыедЕтятел 1 НМП,ЛСОВ 110 СЛВ"-"ф довательного кода частного; 31 - счетчик;32 - выходЫ Всех разрядов с 18 тч 11 ка 33- выход Счетчика, соог вгетству 10 ший получению всех РазРЯДОВ 1 атсГ 1 того Д 4 . РтгистР дллп мого- сумматор; 35 - единичный выход зна8804 кового разряда сумматора; 36 - нулевой выход знакового разряда сумматора; 37 - де-ь Ш 1 гфрйтОр раСПрЕд 8 ЛИТЕЛЯ ИМПУЛЬСОВ Частного; 38 - выходы дешифратора; 39 - элемент И; 40 - выход злемента И; 41 - группа вентилей для выходов деши атора распрйделителя ИМПУЛЬСОВ ЧаотНОГО; - ВЫХОД .г ВЕНтИЛЕй дешифратора; 43 - цифровой интерполятор; 44 выход всс ттПульсого одв садыке Бого кода меньшего прирашения; 46 - ре-Версивный счетчик координаты х; 47 - выходы реверсивного счетчика координаты х; х 8 - 11 Й.;о-.аналОГОвый 1 преобразователь координаты х, 48 - выход цифре аналогового преобразовате 11 Я координаты х - 50- реверсйвный счетчик координаты э; 51- Вт Подт г Р 818 Рг 1 ВБОУ 0 С 18 тт 1 ИКЙ КООРДИНЙТЫз 52 - цифрго-анаптоговый преобраэоваТЕЛЬ КОордингты 153 ВЫХ д цнфр ЙНЙ, ЛОГОВОГО ПрЕОбраЗОВЙТЕЛЯ КООрдИНатЫ т.ПРием 11 ытй 1 егистР 3 пРедназнйчен длЯ хранения прирашений координат вектора и их з 11 аков Ба Время построения Вектора, Выхо-, ды 4 и 7 приемного регистра 3 управляют, реверсом координатных счетчиков 46 и 50 соответственно, Выходы 5 и 6 приемногоРЕГИСтРа 111 даКгтпЧРаллеЛЬНЫЙ ДВОИЧНЫЙ код приращений в х, л у Коммутатор 8 прира 1:,ений 1 координат сравнивает коды при ращений координат и по Выходу 10 выдает код боцьш 810 приращения в регистр делите-ля 23. цифооиого блока 16 деления, а по выходу 11 выдает код меньшего приращения в 1 егистр делнмо 10-сумматор 34 цифрового блОка 16 допения. Выходы 9 и 12 кОммутатора приращений 8 управляют приемом реверсивнь м с ет Вкол 46 координаты х И 1 ге 181 с 11111 ц 111 1 18 т 11 ком 5 0 кооттдинаты г Рхь р ст число -импульсньгх кодов приращений именно своей к 001 эдоинаты, Выход 13 к 01 о 1 мутаторй 8 выдает импульс по Окончании построения Векторасобират 81 пная схема ИЛИ 14 предназначена для выдачи Ба своем выходе 15 импульса, по которому заканчивается процесс деления В цифровом блоке 16 деления. Цифровой блок 1 с делдния предназначен для деления мхзньшедгог прирашения на большее и получения последовательного кода частного,Генератор 17 тактовых импульсов прейчазначен для получения импульсов, управляли;их процессом деления, Еегистр 21 делителя предназначен для хранения значения большего прнрашения, Выходы 22 регистра 21 предназначены для выдачи прямого кода боль 1 пего приращения, Выходь 1 23 регистра , 1 преднанйчены для выдачи обратного ко 0 т да большего поира 11 ения. Элелхент И 24 и группа вентилей 26 предназначена для подаП 1 В РЕГИСТР ДЕЛИМОГО-СУММатОР ПРЯМОГО Коесли результат В суммагОсе 1 ьосле О- "-"Веднсго Вычитании де 11 ителя из сдвиачто. О наРаЗРЯД ВЛЕВО ЗНгЧЕ и ДГМ Опо О" д ЗаСОТРИЦатЕЛЬНЫМ, 1 ОУ 1 П 1 а ВЕ 11 п 1 пей 2 8 Пр:,Д;.а,значена для подачи ВО втором такте цик;1 аделения обратного кода делителя ВВг.ств.- сумматор 34 делимого.Регистр-сумматор 34 делимого предназначен для сложения значе 1 ьия делимого с рпрямым или обратным кодом делителя В за=висимости,от выходов 35 и 36 знаковогоразряда, Злемент И 39 предназначен дляполучения на его выходе 40 последоватип -ного кода частного. Распределитель импульсов последовательного кода частного 30 состоит из счетчика 31, дешицратора 37, группы вентилей 41 и предназначен для подачиимпульсов кода частного, следуюших начи=ная со старшего разряда, В соответствующие Кразряды регистра цифрового интерполятора43. Цифровой интерполятор 43 выдает на Выходе 44 число-импутп;Оный код большего пр;. -ращения постоянной частоты, не завис 1 шгейот величины приращения, и на выходе 45число-импульсный код меньшего приращения,равномерно распределенный на отрезке времени, необходимом ДляПреобразования кодабольшего прирашенпя. Реверсивные счетчикикоординат 46 и 50 и цифро-аналоговые пре-ЗОобразователи 48 и 52 цредназ 11 ачень дляпреобразования число-импульсных кодов приращений координат с выходов 44 и 45 вступенчатое линейно изменяющееся напррл;е ние на выходах 49 и 53. ЗОУстройство работает следующим Образом,По входу 1 В приемный регистр 3 запи=сыва 10 тся коды прирашени,4 координат Векго:ра и их знаки, Зна 1 ещ 1 Я приращений с Выхс=.дов 3 и 6 приемного регпстра,э В парад.- 4 Одельном коде Выдаются на коммутатор 8приращений. Коммутатор 8 пр 1 рашен 111 сравнивают коды прЩ)аше 111 Й и ПО выходам 1 0Всегда выдает код большего приращения апо выходам 11 код меньшего прираше 1 ия, 4 бВыходы 9 и 12 коммутатора 8 приращенийопределя 1 от какое именпо из приращенийменьшее, а какое большее. Код большего прира 1 цения с выходов 10 записываегся В ре=гистр 21 1 тегдгтеля а ко меньше 1 р 1 трива Ющения с выходов 11 запись 1 вается Врэг 11 стргделимого сумматор 4. С прихОДОЬ за 1 ускащ1 ошего импульса по входу 2 запускаетсяГенератор 1 7 та 1 товь 1 х импльсов,ПерВьЕИ тактовый импульс с Вь".Да 1 8генератора 17 тактОВ 1 х импу 1 Ьсов сдвиьр, - .ет дели 1 ое г с а.-о 1 34 ча р:1:-,л,-; - дВлево и записывает единицу В с 1 етчпк 31распределигеля 30 11 п"п,сов Г;Оой та 1;,.говый импульс с ВьХода .9 ГенератсОО ;.; л к,;:. ы,1 1 аот об тный кодчителя че"е г11 П вентилей в;23 сумматор 3-" Г сли .ри этом окажется, чтосдвинутое значение делимого В сумматоребольше делителя, то в знаковом разрядесумматора будет записан Оф, что соответствует еаниц- ь старшем разряде частного.На элемент И 39 по нулевому выхсду 36 знакового разряда сумматора 34 будет выдано разрешение, а по единичному выходу 35 знакового разряда сумматора 34 на эле мент И 24 будег действовать запрет. Поэтому третий тактовый иытульс с выхода 20 через элемент И 39 поступит на входы группы вентилей 41, и через тот венгиль, который вторым своим входом подсоединен. к единичному выходу дешифратора, а своим Выходом ко входу старшего разряда регистра цифрового интерполятора, запишет едищмцу в этот разряд, Если же окажется что после Второго такта сдвинутое делимое меньше делителя, то в знаковом разряде сумматора будет записана "1 ф и на элемент Л 39 и по выходу 36 будет выдан запрет и единица в соответствующий разряд регистра цифрового интерпопятора 43 не запишется. По выходу 35 будет действовать разрешение и третий тактовый импульс с выхода 20 генератора 17 тактовых импульсов через эль-, мент И 24 и группу вентилей 26 выдаст прямой код делителя в сумматор 37, что вызовет Восстановление остатка в нем, Далее цикл получения очередного разряда частного повторяется. Таким образом, частноепоследовательным кодом, начиная со старшего разряда подается в соответствующие разряды регистра цифрового,интерполятора,Работа цифрового блока 16 деления 16 и цифрового интерполятора 43 происходит одновременно. Это осуществляется запуском ; нервтора цифрового интерполятора уже в первом цикле третим тактовым импульсом с Выхода 20 генератора 17 тактовых импульсов одновременно с записью в регистр циф рового интерполятора старшего разряда часг ного. С Выхода 44 цифрового интерполятора 43 серия импульсов с частотой 1 енератора цифрового интерполятора 43 будет поступать в один из реверсивных счетчиков 46 или 50 В зависимости От состояниЯ Выходов 9 и 12 коммутатора приращений 8, опредоля 1 оших, какое из приращений больше. С вы-хода 45 цифрового интерполятора 43 число- импульсный код будет поступать в другой с 1 етчик. Реверсом счетчиков 46 и 50 управля 1 ст выходь 1 4 и 7 приемного регистра 3. При этом на выходах 49 и 53 цифро-аналоговых преобразователей получается линейно8 О8ды - с выходами цифрового интерполятора, авходы блокировки счета - соответственно спервым и вторым выходами коммутатора,третий выход которого подключен к управляюшему входу цифрового интерполятора и черезэлемент ИЛИ - ко входу генератора. тактовыхимпульсов, первый выход которо соединенчерез распределитель импульсов со входамицифрового интерполятора, группы вентилей иэлементы И, отличающийся тем,что, с целью упрощения генератора и сокращения избыточности информации при обменес внешними устройствами, он содержит циф-.ровой блок деления, состоящий из регистра нзмевщацееся ступенчатое напряжение. Им пульсы с выхода 44 цифрового интерполято,ра 43 поступают в коммутатор 8 приращений, где каждый импульс уменьшает на единицу значение большего приращения. После того, как оно станет равным нулю, коммутатор приращений 8 импульсом с выхода 13 возвращает в исходное состояниецифровой интерполятор 43, посылает запрос на координаты следующего вектора и через собира тельную схему ИЛИ 14 возвращает в исходное состояние цифровой блок 16 деления, еоли до этого через второй вход собирательной схемы 14 цифровой блок 16 деления не вер нул в исходное состояние импульс с выхода 15 33 счетчика 31, соответствующий записи кода младшего разряда частного в регистр цифрового интерполятора 43,Формула изобретения20Генератор векторов для системы отображения графической информации, содержащий приемный регистр, выходы приращейий координат которого подключены ко входам коммутатора, а выходы знаков приращений - ко входам управления реверсом счетчиков коор ;динат, выходы которых соединены с цифроаналоговыми преобразователями, счетные входелимого и регистра делителя, выходы прямого и обратного кода которого подключены черезсоответствующие группы вентилей ко входамрегистра делимого, знаковые выходы которогосоединены с одними из входов элементов И,йричем второй выход генератора тактовыхимпульсов подключен ко входам одной изгрупп вентилей, а третий - к импульсномувходу цифрового интерполятора и к другимвходам элементов И, выход одного из которых соединен со входами другой группывентилей, а выход другого элемента И - сдополнительным входом распределителя гм-,пульсов.

СмотретьЗаявка

2025620, 17.05.1974

ОБЪЕДИНЕННЫЙ ИНСТИТУТ ЯДЕРНЫХ ИССЛЕДОВАНИЙ

ЛЫКОВ ЮРИЙ ИВАНОВИЧ

МПК / Метки

МПК: G06K 15/20

Метки: векторов, генератор, графической, информации, отображения, системы

Опубликовано: 25.08.1976

Код ссылки

<a href="https://patents.su/5-525980-generator-vektorov-dlya-sistemy-otobrazheniya-graficheskojj-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Генератор векторов для системы отображения графической информации</a>

Предыдущий патент: Устройство индикации фокального пятна

Следующий патент: Устройство для регистрации рабочих режимов транспортных средств

Случайный патент: Устройство для расщипывания кип табака