Устройство для сравнения и сортировки чисел

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

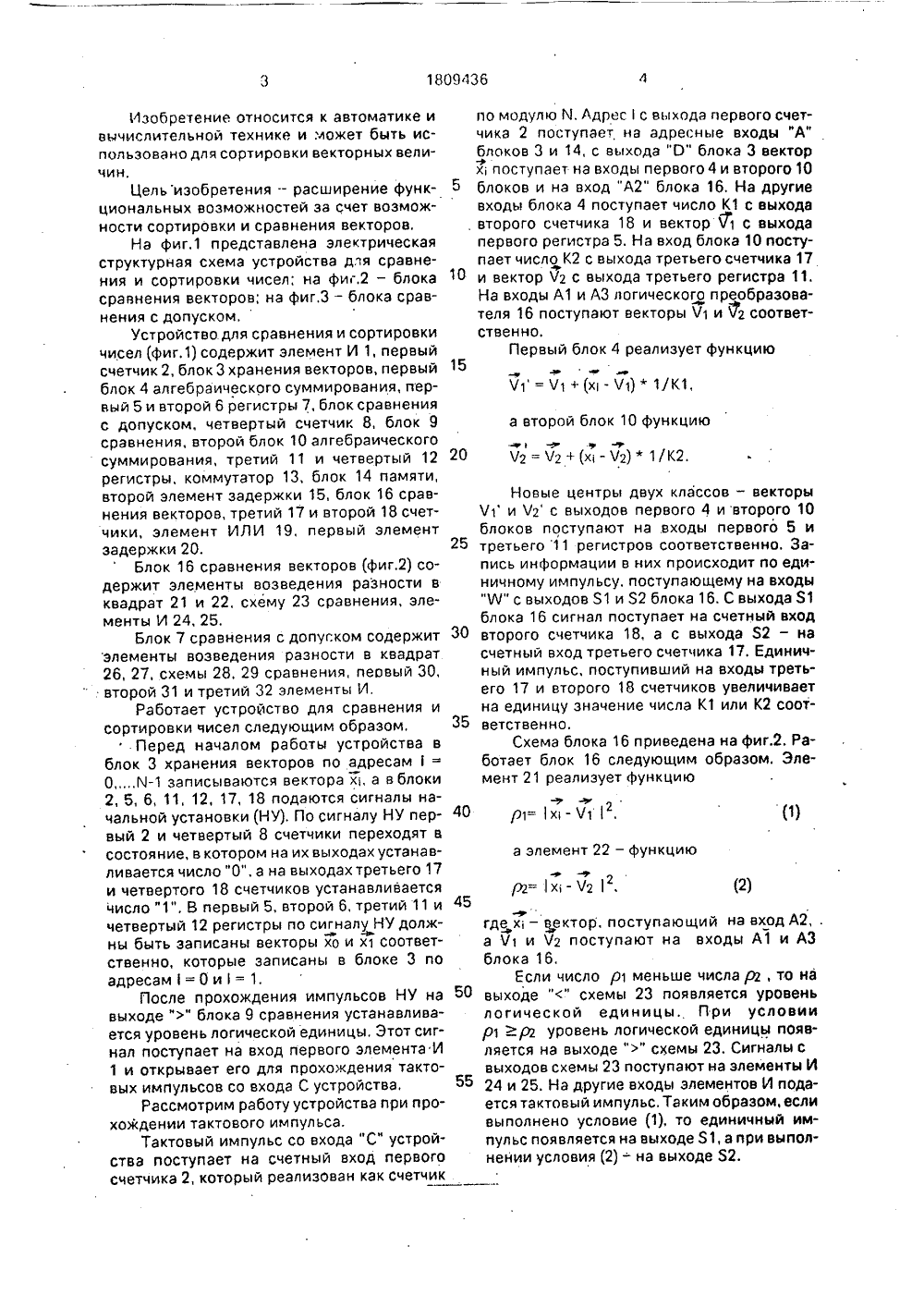

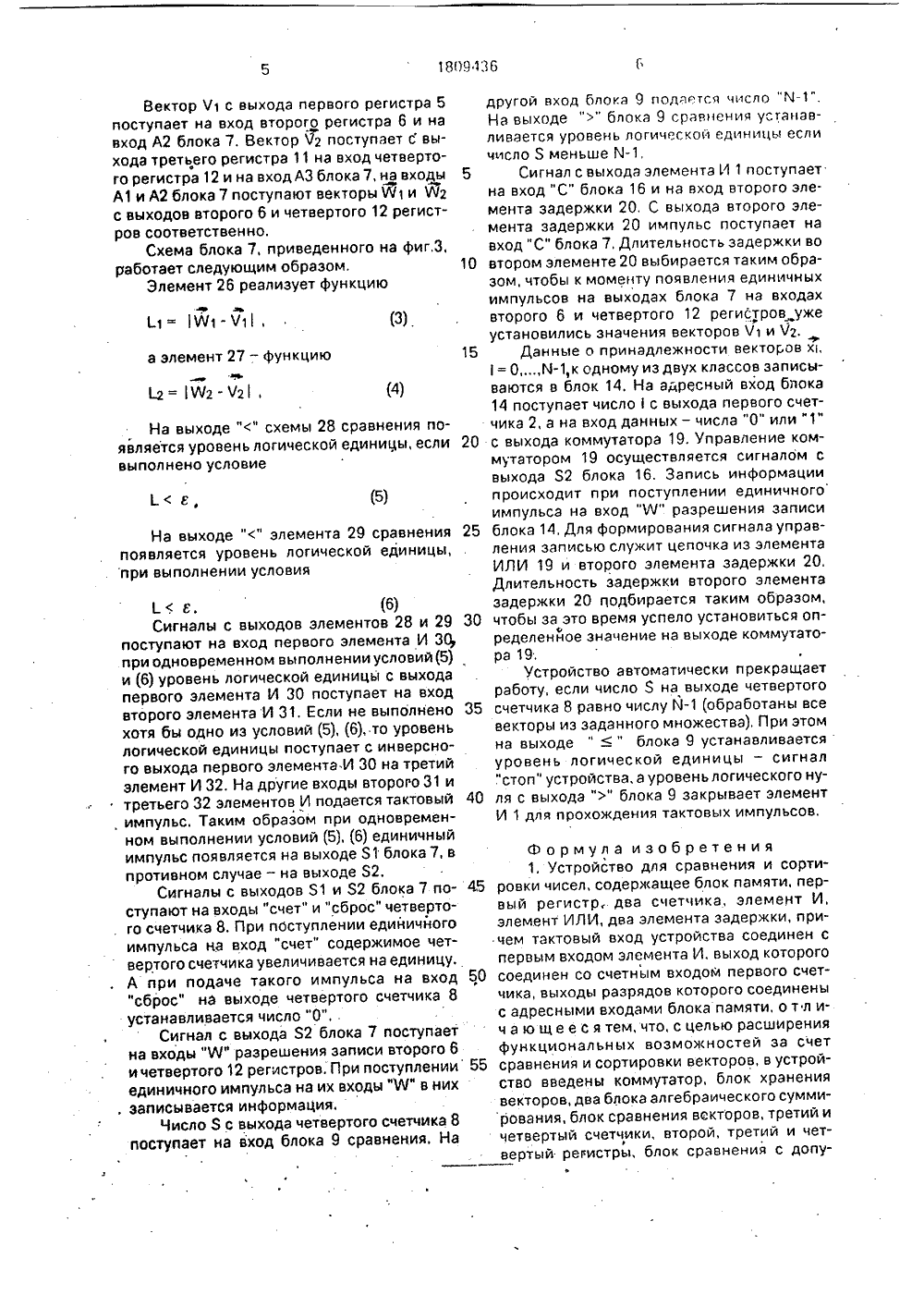

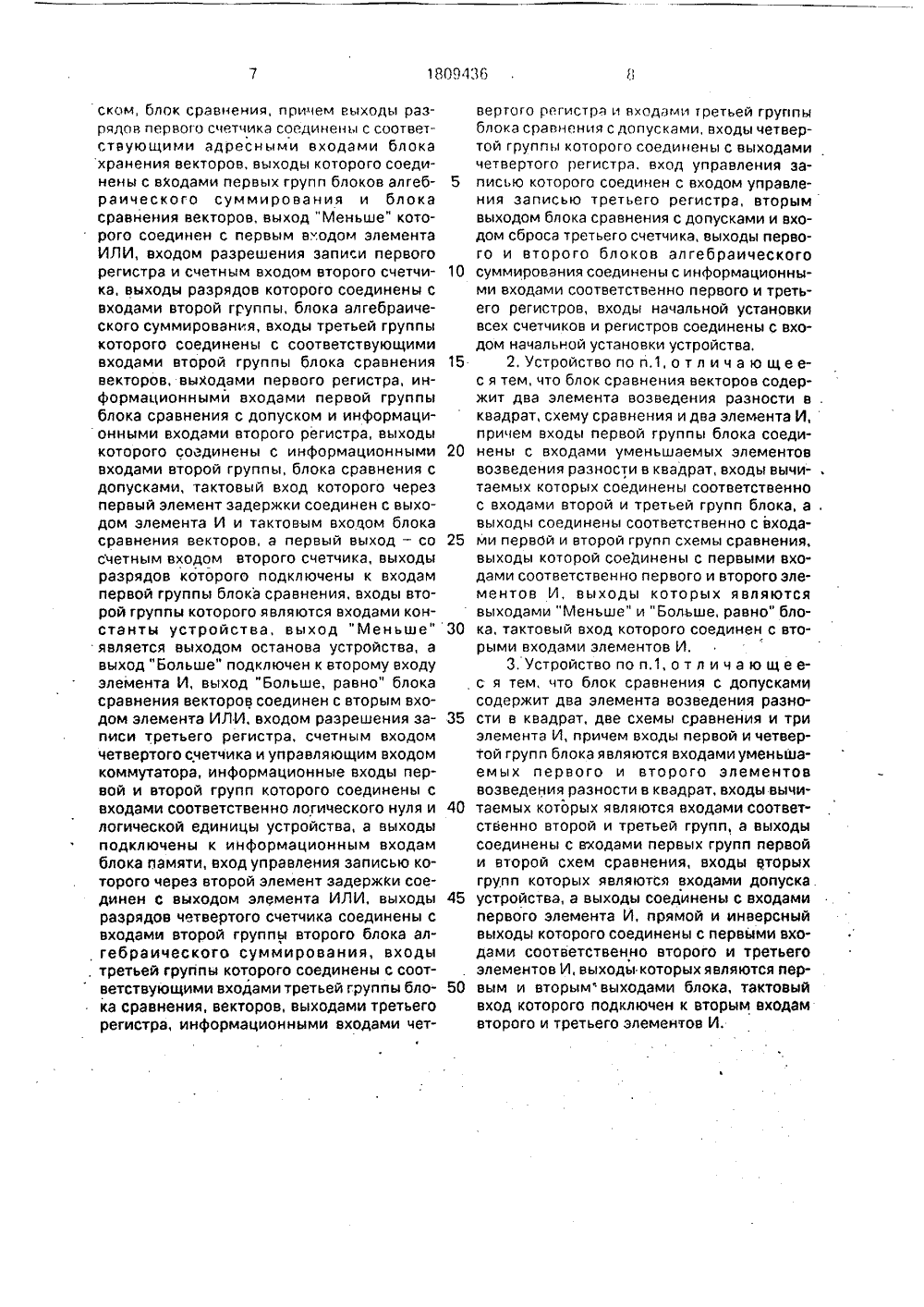

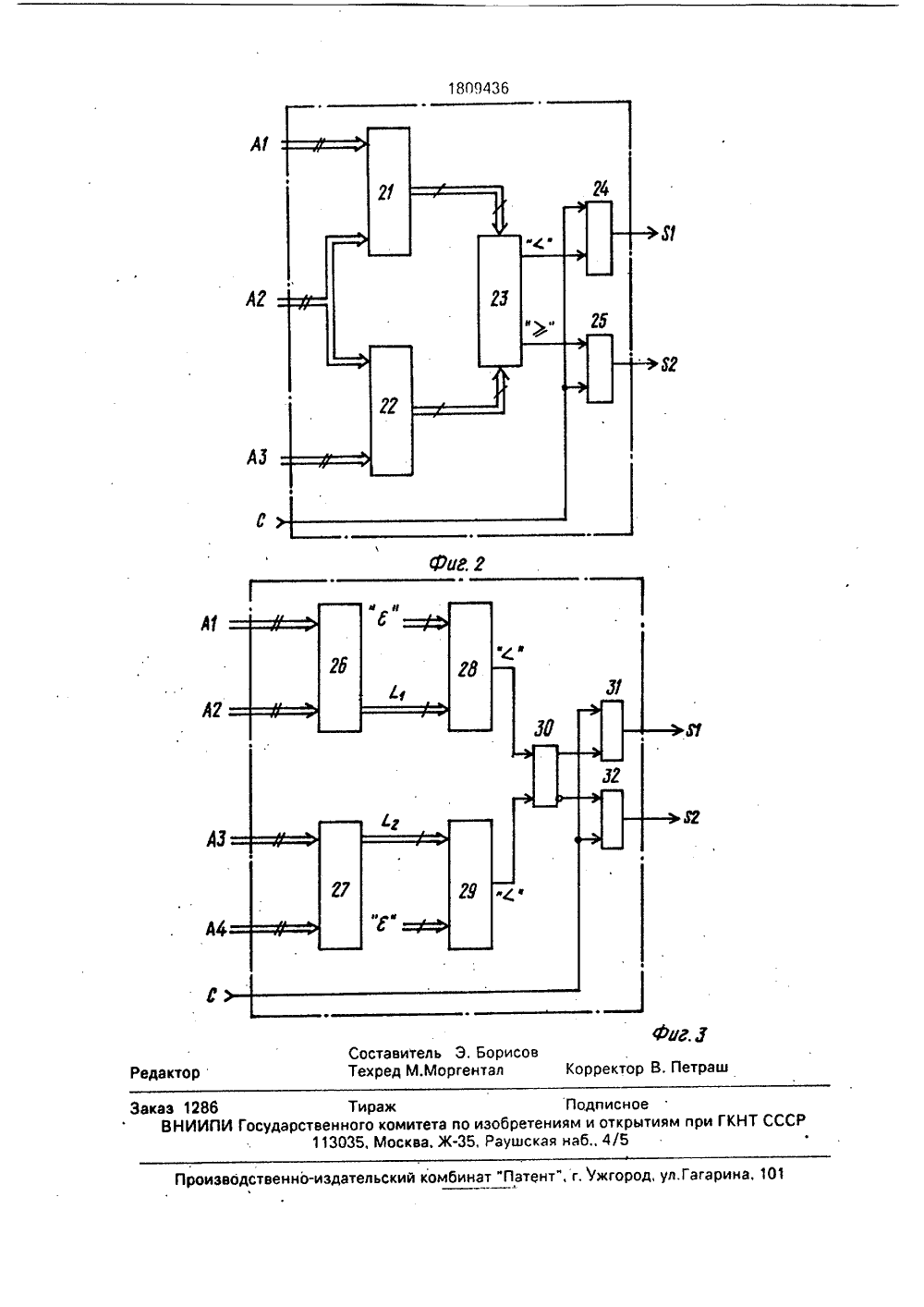

9436 А 1 СОЮЗ СОВЕТСКИСОЦИАЛ ИСТИЧЕ СРЕСПУБЛИК(57) Изобретение относится к автоматике вычислительной технике и может быть и польэовано для сортировки чисел путем сравнения с нечетким числом. Цель изобр тенйя - расширение функциональных во можностей, Устройство содержит элемент 1, счетчики 2, 17, 18, 8, блок хранения вект ров 3, блок 14 памяти, коммутатор 19, бло алгебраического суммирования 4 и 10, блок сравнения с допуском 7 и блок сравнения векторов 16, элемент ИЛИ 19, элементы задержки 20 и 16, регистры 5, 6, 11, 12 и бл сравнения 9, 3 ил.Изобретение относится к автоматике ивычислительной технике и может быть использовано для сортировки векторных величин.Цель изобретения - расширение функциональных возможностей за счет возможности сортировки и сравнения векторов,На фиг.1 представлена электрическаяструктурная схема устройства для сравнения и сортировки чисел; на фиг,2 - блокасравнения векторов; на фиг.З - блока сравнения с допуском,Устройство для сравнения и сортировкичисел (фиг.1) содержит элемент И 1, первыйсчетчик 2, блок 3 хранения векторов, первыйблок 4 алгебраического суммирования, первый 5 и второй 6 регистры 7, блок сравненияс допуском, четвертый счетчик 8, блок 9сравнения, второй блок 10 алгебраическогосуммирования, третий 11 и четвертый 12регистры, коммутатор 13, блок 14 памяти,второй элемент задержки 15, блок 16 сравнения векторов, третий 17 и второй 18 счетчики, элемент ИЛИ 19, первый элементзадержки 20.Блок 16 сравнения векторов (фиг,2) содержит элементы возведения разности вквадрат 21 и 22, схему 23 сравнения, элементы И 24, 25,Блок 7 сравнения с допугком содержитэлементы возведения разности в квадрат26, 27, схемы 28. 29 сравнения, пеовый 30,: второй 31 и третий 32 элементы И,Работает устройство для сравнения исортировки чисел следующим образом.Перед началом рабаты устройства вблок 3 хранения векторов по адресам=О,Мзаписываются вектора хь а в блоки2, 5, 6, 11, 12, 17, 18 подаются сигналы начальной установки (НУ). По сигналу НУ первый 2 и четвертый 8 счетчики переходят асостояние, в котором на их выходах устанавливается число "0". а на выходах третьего 17и четвертого 18 счетчиков устанавливаетсячисло "1". В первый 5, второй 6, третий 11 ичетвертый 12 регистры по сигналу НУ должны быть записаны векторы хо и х 1 соответственно, которые записаны в блоке 3 поадресам 1= 0 и 1= 1.После прохождения импульсов НУ навыходе блока 9 сравнения устанавливается уровень логической единицы. Этот сигнал поступает на вход первого элемента И1 и открывает его для прохождения тактовых импульсов со входа С устройства,Рассмотрим работу устройства при прохождении тактового импульса.Тактовый импульс со входа "С" устройства поступает на счетный вход первогосчетчика 2, который реализован как счетчик по модулю К, Адрес с выхода первого счетчика 2 поступает на адресные входы "А"блоков 3 и 14, с выхода "0" блока 3 векторх поступает на входы первого 4 и второго 105 блоков и нэ вход "А 2" блока 16, На другиевходы блока 4 поступает число К 1 с выхода, второго счетчика 18 и вектор (7 с выходапервого регистра 5. На вход блока 10 поступает число К 2 с выхода третьего счетчика 1710 и вектор Ч 2 с выхода третьего регистра 11.На входы А 1 и ЛЗ логического преобразователя 16 поступают векторы Ч 1 и А соответственно,Первый блок 4 реализует функцию15Ч 1 = Ч 1+ (х - Ч 1)1/К 1,а второй блок 10 функцию4 ф 1,9 ф20 Ч 2 = Ч 2 + (х - Ч 2)1/К 2.Новые центры двух классов - векторыЧ 1 и Ч 2 с выходов первого 4 и второго 10 блоков поступают на .входы первого 5 и 25 третьего 11 регистров соответственно, Запись информации в них происходит по единичному импульсу, поступающему на входы "Ю" с выходов 31 и 32 блока 16. С выхода 31 блока 16 сигнал поступает на счетный вход ЗО второго счетчика 18, а с выхода 32 - насчетный вход третьего счетчика 17, Единичный импульс, поступивший на входы третьего 17 и второго 18 счетчиков увеличивает на единицу значение числа К 1 или К 2 соот ветственно.Схема блока 16 приведена на фиг.2. Работает блок 16 следующим образом. Элемент 21 реализует функцию40 р 1=х - Ч 1 1,а элемент 22 - функцию2р 2= 1 х -Ч 2 1, (2)45где х, - вектор, поступающий на вход А 2, .а Ч 1 и Ч 2 поступают на входы А 1 и АЗ блока 16,Если число р 1 меньше числа рг, то навыходе схемы 23 появляется уровень логической единицы. При условии р 1 р 2 уровень логической единицы появляется нэ выходе схемы 23. Сигналы с выходов схемы 23 поступают на элементы И 55 24 и 25. На другие входы элементов И подается тактовый импульс. Таким образом, если выполнено условие (1), то единичный импульс появляется на выходе 51, а при выполнении условия (2) - на выходе 52.Вектор Ч 1 с выхода первого регистра 5 поступает на вход второго регистра 6 и на вход А 2 блока 7. Вектор 2 поступает с выхода третьего регистра 11 на вход четвертого регистра 12 и на вход АЗ блока 7, на входы 5 А 1 и А 2 блока 7 поступают векторы Л 1 и ЧЧ 2 с выходов второго 6 и четвертого 12 регистров соответственно.Схема блока 7, приведенного на фиг,З, работает следующим образом, 10Элемент 26 реализует функцию 1 1 =В/1 - Ч 11,(3) 15 а элемент 27 - функцию(2 = 1162- Ч 21,(4) На выходе схемы 28 сравнения появляется уровень логической единицы, если 20 выполнено условие(5) 1 я,На выходе элемента 29 сравнения 25появляется уровень логической единицы,при выполнении условия 1е. (6)Сигналы с выходов элементов 28 и 29 30поступают на вход первого элемента И 30при одновременном выполнении условий(5)и (6) уровень логической единицы с выходапервого элемента И ЗО поступает на входвторого элемента И 31, Если не выполнено 35хотя бы одно из условий (5), (6), то уровеньлогической единицы поступает с инверсного выхода первого элемента И 30 на третийэлемент И 32. На другие входы второго 31 итретьего 32 элементов И подается тактовый 40, импульс. Таким образом при одновременном выполнении условий (5), (6) единичныйимпульс появляется на выходе 31 блока 7, впротивном случае - на выходе 52,Сигналы с выходов 81 и 52 блока 7 поступают на входы "счет" и "сброс" четверто. го счетчика 8, При поступлении единичйогоимпульса на вход "счет" содержимое четвертого счетчика увеличивается на единицу.А при подаче такого импульса на вход 50"сброс" на выходе четвертого счетчика 8устанавливается число "0",Сигнал с выхода 32 блока 7 поступаетна входы "И/" разрешения записи второго 6и четвертого 12 регистров. При поступлении 55единичного импульса на их входы "М/" в них. записывается информация.Число 8 с выхода четвертого счетчика 8поступает на вход блока 9 сравнения. На другой вход блока 9 подается число "М". На выходе блока 9 сравнения устанавливается уровень логической единицы если число 5 меньше М,Сигнал с выхода элемента И 1 поступает на вход "С" блока 16 и на вход второго элемента задержки 20, С выхода второго элемента задержки 20 импульс поступает на вход "С" блока 7, Длительность задержки во втором элементе 20 выбирается таким образом, чтобы к моменту появления единичных импульсов на выходах блока 7 на входах второго 6 и четвертого 12 регистров уже установились значения векторов Ч 1 и Ч 2.Данные о принадлежности векторов хь= О,. М,к одному из двух классов записываются в блок 14, На адресный вход блока 14 поступает число с выхода первого счетчика 2, а на вход данных - числа "0" или "1" с выхода коммутатора 19. Управление коммутатором 19 осуществляется сигналом с выхода 82 блока 16, Запись информации происходит при поступлении единичного импульса на вход "Ю разрешения записи блока 14, Для формирования сигнала управления записью служит цепочка из элемента ИЛИ 19 и второго элемента задержки 20, Длительность задержки второго элемента задержки 20 подбирается таким образом, чтобы за это время успело установиться определен йое значение на выходе коммутатора 19.Устройство автоматически прекращает работу, если число Я на выходе четвертого счетчика 8 равно числу Й(обработаны все векторы из заданного множества), При этом на выходе " " блока 9 устанавливается уровень логической единицы - сигнал ."стоп" устройства, а уровень логического нуля с выхода блока 9 закрывает элемент И 1 для прохождения тактовых импульсов,Формула изобретения 1. Устройство для сравнения и сортировки чисел, содержащее блок памяти, первый регистр. два счетчика, элемент И, элемент ИЛИ, два элемента задержки, причем тактовый вход устройства соединен с первым входом элемента И, выход которого соединен со счетным входом первого счетчика, выходы разрядов которого соединены с адресными входами блока памяти, о т л ич а ю щ е е с я тем, что, с целью расширения функциональных возможностей за счет сравнения и сортировки векторов, в устрой- ствО введены коммутатор, блок хранения векторов, два блока алгебраического суммирования, блок сравнения векторов, третий и четвертый счетчики, второй, третий и четвертый регистры, блок сравнения с допу- ь5 10 15 20 25 30 35 40 45 50 ском, блок сравнения, причем выходы разрядов первого счетчика соединены с соответствующими адресными входами блока хранения векторов, выходы которого соединены с входами первых групп блоков алгебраического суммирования и блока сравнения векторов, выход "Меньше" которого соединен с первым входом элемента ИЛИ, входом разрешения запи.и первого регистра и счетным входом второго счетчика, выходы разрядов которого соединены с входами второй группы, блока алгебраического суммирования, входы третьей группы которого соединены с соответствующими входами второй группы блока сравнения векторов, выходами первого регистра, информационными входами первой группы блока сравнения с допуском и информационными входами второго регистра, выходы которого соединены с информационными входами второй группы, блока сравнения с допусками, тактовый вход которого через первый элемент задержки соединен с выходом элемента И и тактовым входом блока сравнения векторов, а первый выход - со сЧетным входом второго счетчика, выходы разрядов которого подключены к входам первой группы блока сравнения, входы второй группы которого являются входами константы устройства, выход "Меньше" является выходом останова устройства, а выход "Больше" подключен к второму входу элемента И, выход "Больше, равно" блока сравнения векторов соединен с вторым входом элемента ИЛИ, входом разрешения записи третьего регистра, счетным входом четвертого счетчика и управляющим входом коммутатора, информационные входы первой и второй групп которого соединены с входами соответственно логического нуля и логической единицы устройства, а выходы подключены к информационным входам блока памяти, вход управления записью которого через второй элемент задержки соединен с выходом элемента ИЛИ, выходы разрядов четвертого счетчика соединены с входами второй группы второго блока алгебраического суммирования, входы , третьей группы которого соединены с соответствующими входами третьей группы блока сравнения, векторов, выходами третьего регистра, информационными входами четвергого регистра и входами третьей группы блока сравнения с допусками, входы четвертой группы которого соединены с выходами четвертого регистра, вход управления записью которого соединен с входом управления записью третьего регистра, вторым выходом блока сравнения с допусками и входом сброса третьего счетчика, выходы первого и второго блоков алгебраического суммирования соединены с информационными входами соответственно первого и третьего регистров, входы начальной установки всех счетчиков и регистров соединены с входом начальной установки устройства,2, Устройство по п.1, о т л и ч а ю щ е ес я тем, что блок сравнения векторов содержит два элемента возведения разности в квадрат, схему сравнения и два элемента И, причем входы первой группы блока соединены с входами уменьшаемых элементов возведения разности в квадрат, входы вычитаемых которых соединены соответственно с входами второй и третьей групп блока, а выходы соединены соответственно с входами первой и второй групп схемы сравнения, выходы которой соединены с первыми входами соответственно первого и второго элементов И, выходы которых являются выходами "Меньше" и "Больше, равно" блока, тактовый вход которого соединен с вторыми входами элементов И.3. Устройство по п.1, о т л и ч а ю щеес я тем, что блок сравнения с допусками содержит два элемента возведения разности в квадрат, две схемы сравнения и три элемента И, причем входы первой и четвертой групп блока являются входамиуменьшаемых первого и второго элементов возведения разности в квадрат, входы вычитаемых которых являются входами соответственно второй и третьей групп, а выходы соединены с входами первых групп первой и второй схем сравнения, входы вторых групп которых являются входами допуска устройства, а выходы соединены с входами первого элемента И, прямой и инверсный выходы которого соединены с первыми входами соответственно второго и третьего элементов И, выходы которых являются первым и вторымвыходами блока, тактовый вход которого подключен к вторым входам второго и третьего элементов И.18 й 9436 4 Г А 2 Фиг, уСоставитель Э. Борисовехред М.Моргентал Корректор В. Петра дакт ельский комбинат "Патент", г. ужгород, ул.Гагарина, 101 изводственно Заказ 1286 Тираж ПодписноеВНИИПИ Государственного комитета по изобретениям и открытиям при ГКНТ СССР113035, Москва, Ж, Раушская наб 4/5

СмотретьЗаявка

4902485, 14.01.1991

ВОЕННАЯ АКАДЕМИЯ ИМ. Ф. Э. ДЗЕРЖИНСКОГО

БОРИСОВ ЭДУАРД ВАСИЛЬЕВИЧ, КВАС ОЛЕГ МИХАЙЛОВИЧ, КОРАБЛИН ВАДИМ АНАТОЛЬЕВИЧ, СЕРОВ РОМАН ЕВГЕНЬЕВИЧ

МПК / Метки

МПК: G06F 7/04

Метки: сортировки, сравнения, чисел

Опубликовано: 15.04.1993

Код ссылки

<a href="https://patents.su/5-1809436-ustrojjstvo-dlya-sravneniya-i-sortirovki-chisel.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для сравнения и сортировки чисел</a>

Предыдущий патент: Устройство для сравнения нечетких величин

Следующий патент: Арифметическое устройство по модулю

Случайный патент: Способ производства крепкого напитка