Устройство для кодирования и декодирования сигналов цифрового модема

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1783625

Автор: Лада

Текст

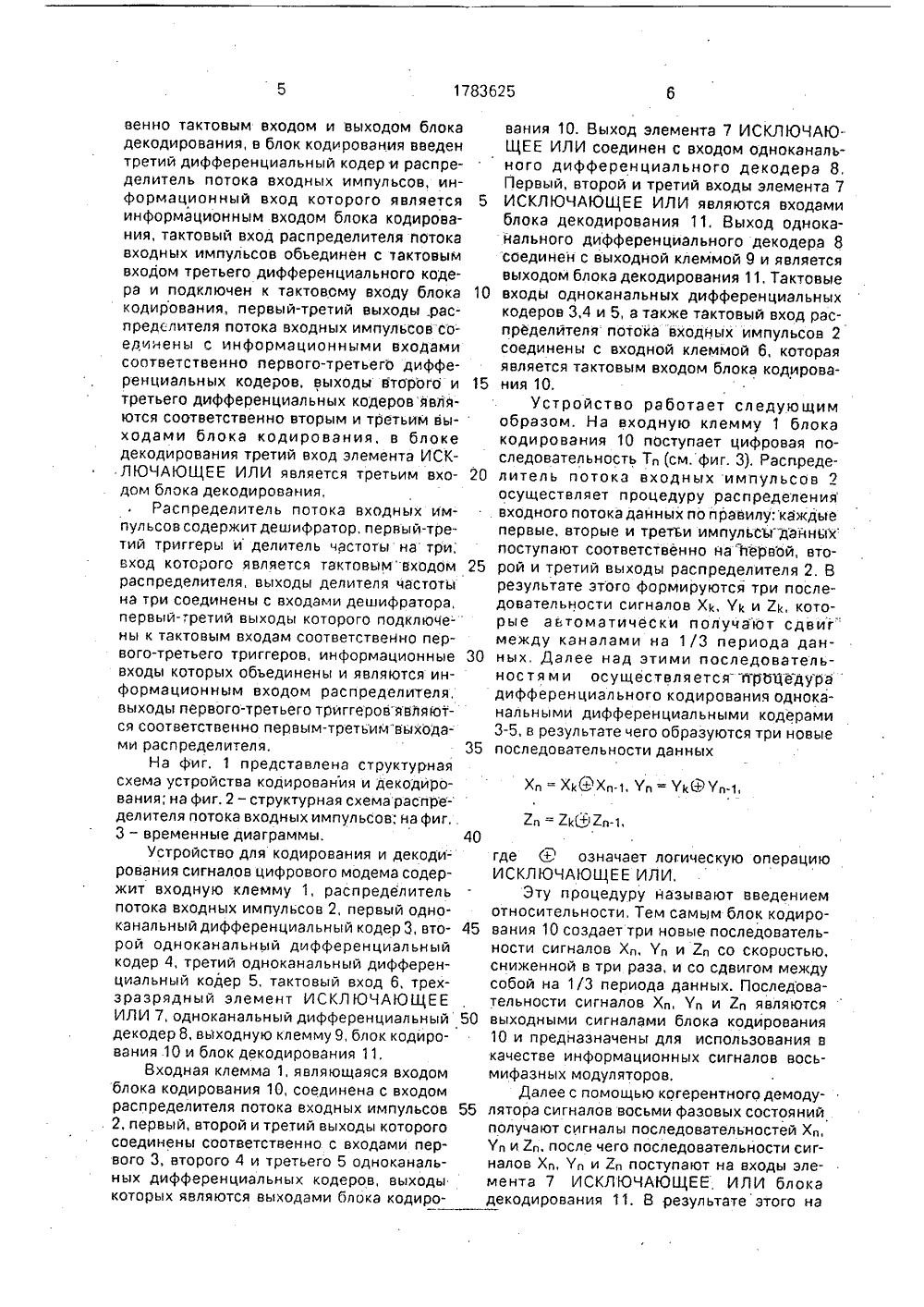

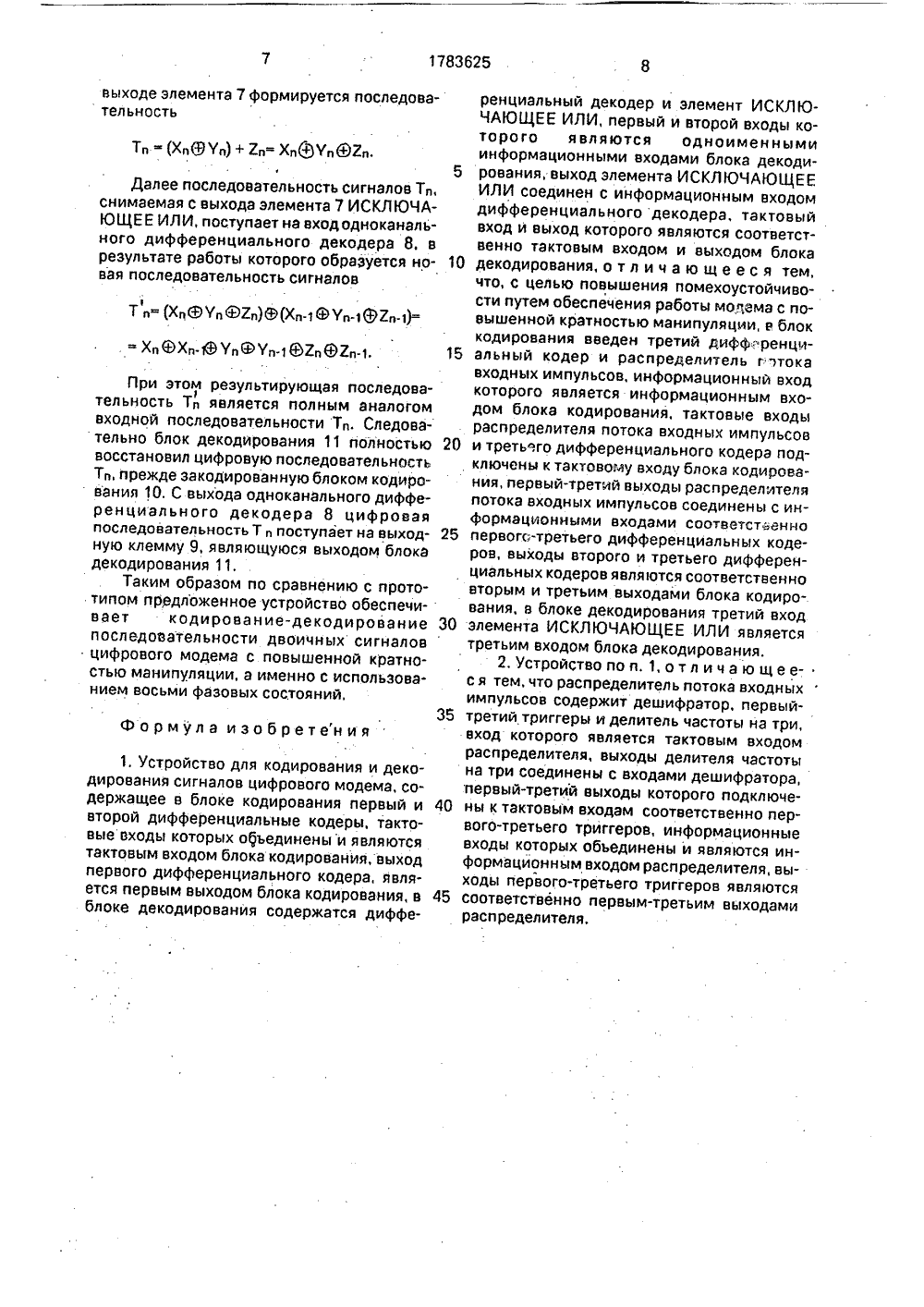

СОК)3 СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУВЛИК 9) 62 1)5 ГОСУДАРСТВЕННОЕ ПАТЕНТНОЕВЕДОМСТВО СССРГОСПАТЕНТ СССР) ПИСАНИЕ ИЗОБ АВОРСКОМУ СВИДЕТЕЛЬСТВ НИ использование в системах передачи высокоскоростных сигналов позволяет повысить помехоустойчивость за счет обеспечения работы модема с повышенной кратностью манипуляции. Устройство содержит в блоке 10 кодирования дифференциальные кодеры 3,4, а в блоке 11 декодирования - элемент 7 ИСКЛЮЧАЮЩЕЕ ИЛИ и дифференциальныйдекодер 8. Благоцаря введению в блок 10 кодирования распределителя 2 потока входных импульсов и дифференциального кодера 5 в устройстве обеспечивается кодирование и декодирование сигналов для передачи в цифровом модеме с восьмифазной манипуляцией, 1 з.п. ф-лы, 3 ил. 559006 ции М 1985.М 02062О ДЛЯ ОЗ, кл. Н 04 1 27 18, КОДИРОВАНИЯ И ГНАЛОВ ЦИФРО- сится к вычислихнике связи. Его ео е и(57) Изобретенительной техник отделение Научно-исс ститута радио М 13/00, Н 04 1. 2718- Т + Х + Х -1+ У -1. Изобретение относится к вычислительной технике и технике связи и может быть использовано в радиорелейных и спутниковых системах связи для передачи высокоскоростных цифровых сигналов данных и сигналов цифрового телевидения. Известно устройство для кодирования и декодирования, содержащее блок кодирования для преобразования цифровой последовательности Тп двоичных сигналов в две цифровые последовательности Х, и У и блок декодирования для восстановления цифровой последовательности Тл с помощью последовательностей Хп и Ул, подаваемых на его вход.Блок кодирования содержит входную клемму для подачи цифровой последовательности Тп, преобразователь последовательной формы сигналов в двухканальную параллельную информацию со сдвигом между каналами на 1/2 периода данных, два одноканальных дифференциальных кодера.Блок декодирования содержит два одноканальных дифференциальных декодера и преобразователь двухканальной параллельной информации со сдвигом между каналами на 1/2 периода данных в сигналы последовательной формы, а также выходную клеьЪу, являющуюся выходом блока декодирования, входом которого являются входы первого и второго одноканальных дифференциальных декодеров,Известно устройство для кодирования и декодирования, содержащее блок кодирования для преобразования цифровой последовательности Т двоичных сигналов в две цифровые поСледовательности Х, и У и блок декодирования для восстановления цифровой последовательности Тп с помощью последовательностей Хп и Ул, подаваемых на его вход.Блок кодирования содержит первую логическую цепь для присвоения каждому биту последовательности Хп одинакового двоичного значения "1" (или "0"), когда выполняется,логическое соотношение где Нлд - импульсы фазовой синхронизации с битами Тп,и вторую логическую цепь для присвое.ния каждому биту последовательности Уп одинакового значения "1" (или "О"), когда выполняется логического соотношение 20 25 30 35 40 45 50 55 Первая логическая цепь состоит из одноканального дифференциального кодера, построенного на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ, и элемента памяти на один бит и второго элемента ИСКЛ ЮЧАЮ ЩЕ Е ИЛИ, а вторая логическая цепь состоит из элемента НЕ, элемента 2 И-НЕ и второго дифференциального кодера, построенного на элементе ИСКЛЮЧАЮЩЕЕ ИЛИ и элемента памяти на один бит.Блок декодирования содержит логическую цепь для присвоения каждому биту последовательности Тп одинакового двоичного значения, когда выполняется логическое соотношение Тп = Хл + Хп.1+ Ул + УпЛогическая цепь блока декодирования состоит из двухразрядного элемента ИСКЛЮЧАЮЩЕЕ ИЛИ и одноканальногодифференциального декодера, при этом входы элемента ИСКЛЮЧАЮЩЕЕ ИЛИ являются входом блока декодирования, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом одноканального дифференциального декодера, выход которого соединен с выходной клеммой и является выходом блока декодирования.Устройство является наиболее близким к предлагаемому устройству и выбрано в качестве прототипа.Недостатком прототипа является то, что он предназначен для кодирования-декодирования последовательности двоичных цифровых сигналов для цифрового модема со сдвигом и использованием четырех фазовых состояний,Цель изобретения - повышение помехоустойчивости за счет обеспечения работы модема с повышенной кратностью манипуляции.Поставленная цель достигается тем, что в устройство для кодирования и декодирования сигналов цифрового модема, содержащее в блоке кодирования первый и второй дифференциальные кодеры, тактовые входы которых объединены и являются тактовым входом блока кодирования, при этом выход первого дифференциального кодера является первым выходом блока кодирования, в блоке декодирования дифференциальный декодер и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого являются одноименными информационными входами блока декодирования, выход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с информационным входом дифференциального декодера, тактовый вход и выход которого являются соответственно тактовым входом и выходом блокадекодирования, в блок кодирования введентретий дифференциальный кодер и распределитель потока входных импульсов, информационный вход которого является 5информационным входом блока кодирования, тактовый вход распределителя потокавходных импульсов объединен с тактовымвходом третьего дифференциального кодера и подключен к тактовому входу блока 10кодирования, первый-третий выходы .распределителя потока входных импульсов соединены с информационными входамисоответственно первого-третьего дифференциальных кодеров, выхОды второго и 15третьего дифференциальных кодеров являются соответственно вторым и третьим вы-ходами блока кодирования, в блокедекодирования третий вход элемента ИСКЛЮЧАЮЩЕЕ ИЛИ является третьим вхадам блока декодирования,Распределитель потока входных импульсов содержит дешифратор, первый-третий триггеры и делитель частоты на три,вход которога является тактовымвходом 25распределителя, выходы делителя частотына три соединены с входами дешифратора,первый-третий выходы которого подключе-ны к тактовым входам соответственно первого-третьего триггеров, информационные 30входы которых объединены и являются информационным входом распределителя,выходы первого-третьего триггеров"являются соответственно первым-третьим "выходами распределителя. 35На фиг. 1 представлена структурнаясхема устройства кодирования и декодирования; на фиг, 2 - структурная схема распре-делителя потока входных импульсов; на фиг, .3 - временные диаграммы, 40Устройство для кодирования и декодирования сигналов цифрового модема содержит входную клемму 1, распределительпотока входных импульсов 2, первый одноканальныйдифференциальный кодер 3, второй одноканальный дифференциальныйкодер 4, третий одноканальный дифференциальный кодер 5, тактовый вход 6, трехзразрядный элемент ИСКЛЮЧАЮЩЕЕИЛИ 7, одноканальный дифференциальный 50декодер 8, выходную клемму 9, блок кодирования 10 и блок декодирования 11,Входная клемма 1, являющаяся входомблока кодирования 10, соединена с входомраспределителя потока входных импульсов 552, первый, второй и третий выходы которогосоединены соответственно с входами первого 3, второго 4 и третьего 5 одноканальных дифференциальных кодеров, выходыкоторых являются выходами блока кодирования 10. Выход элемента 7 ИСКЛЮЧАЮЩЕЕ ИЛИ соединен с входом одноканального дифференциального декодера 8, Первый, второй и третий входы элемента 7 ИСКЛЮЧАЮЩЕЕ ИЛИ являются входами блока декодирования 11. Выход одноканального дифференциального декодера 8 соединен с выходной клеммой 9 и является выходом блока декодирования 11. Тактовые входы одноканальных дифференциальных кодеров 3,4 и 5, а также тактовый вход распределителя потока входных импульсов 2 соединены с входной клеммой 6, которая является тактовым входом блока кодирования 10.Устройство работает следующим образом, На входную клемму 1 блока кодирования 10 поступает цифровая последовательность Тп (см. фиг. 3). Распределитель потока входных импульсов 2 осуществляет процедуру распределения входного потока данных по правилукаждые первые, вторые и третъи импульсыдайных поступают соответственно на"первой, второй и третий выходы распределителя 2. В результате этого формируются три последовательности сигналов Хь Ук и Ек, которые автоматически получают сдвиг между каналами на 1/3 периода данных, Далее над этими последовательнос тя м и осуществляется-"0 рЬ 4 едура дифференциального кодирования одноканальными дифференциальными кодерами 3-5, в результате чего образуются три новые последовательности данныхх = ХС+ х .1, У = У (+ У -1,7 п = Ъ(+Епгде С+7 означает логическую операцию ИСКЛЮЧАЮЩЕЕ ИЛИ,Эту процедуру называют введением относительности, Тем самым блок кодирования 10 создает три новые последовательности сигналов Хп, Уп и Ъ со скоростью, сниженной в три раза, и со сдвигом между собой на 1/3 периода данных. Последовательности сигналов Хп, Уп и Еп являются выходными сигналами блока кодирования 10 и предназначены для использования в качестве информационных сигналов восьмифазных модуляторов,Далее с помощью когерентного демодулятора сигналов восьми фазовых состояний получают сигналы последовательностей Хп, У, и Ъ, после чего последовательности сигналов Хп, Уп и Ъ поступают на входы элемента 7 ИСКЛЮЧАЮЩЕЕ, ИЛИ блока декодирования 11. В результате этого навыходе элемента 7 формируется последовательностьТп - (Хп 6 Уо) + Еп= Хпб+УпО+2 п.ЮДалее последовательность сигналов Тп, снимаемая с выхода элемента 7 ИСКЛЮЧАЮЩЕЕ ИЛИ, поступает на входодноканального дифференциального декодера 8, в результате работы которого обрадуется новая последовательность сигналовТ о (ХпУоЕп)9(ХпУпЮо)=При этом результирующая последовательность Тп является полным аналогом входной последовательности Тп. Следовательно блок декодирования 11 полностью восстановил цифровую последовательность Т, прежде закодированную блоком кодирования 10. С выхода одноканального дифференциального декодера 8 цифровая последовательность Т и поступает на выходную клемму 9, являющуюся выходом блока декодирования 11,Таким образом по сравнению с прототипом предложенное устройство обеспечивает кодирование-декодирование последовательности двоичных сигналов цифрового модема с повышенной кратностью манипуляции, а именно с использованием восьми фазовых состояний,Формула изобретения1. Устройство для кодирования и декодирования сигналов цифрового модема, содержащее в блоке кодирования первый и второй дифференциальные кодеры, тактовые входы которых оъединены и являются тактовым входом блока кодирования, выход первого дифференциального кодера, является первым выходом блока кодирования, в блоке декодирования содержатся дифференциальныи декодер и элемент ИСКЛЮЧАЮЩЕЕ ИЛИ, первый и второй входы которого являются одноименнымиинформационными входами блока декоди 5 рования, выход элемента ИСКЛЮЧАЮЩЕЕИЛИ соединен с информационным входомдифференциального декодера, тактовыйвход и выход которого являются соответственно тактовым входом и выходом блока10 декодирования, о т л и ч а ю щ е е с я тем,что, с целью повышения помехоустойчивости путем обеспечения работы модема с повышенной кратностью манипуляции, в блоккодирования введен третий дифференци 15 альный кодер и распределитель г токавходных импульсов, информационный входкоторого является информационным входом блока кодирования, тактовые входыраспределителя потока входных импульсов20 и третьего дифференциального кодера подключены к тактовому входу блока кодирования, первый-третий выходы распределителяпотока входных импульсов соединены с информационными входами соответственно25 первого-третьего дифференциальных кодеров, выходы второго и третьего дифференциальных кодеров являются соответственновторым и третьим выходами блока кодирования, в блоке декодирования третий вход30 элемента ИСКЛЮЧАЮЩЕЕ ИЛИ являетсятретьим входом блока декодирования.2, Устройство по и, 1, о т л и ч а ю щ е ес я тем, что распределитель потока входныхимпульсов содержит дешифратор, первый 35 третий триггеры и делитель частоты на три,вход которого является тактовым входомраспределителя, выходы делителя частотына три соединены с входами дешифратора,первый-третий выходы которого подключе 40 ны к тактовым входам соответственно первого-третьего триггеров, информационныевходы которых обьединены и являются информацйонным входом распределителя, выходы первого-третьего триггеров являются45 соответственно первым-третьим выходамираспределителя,Е оставитель С.Шишкинаехред М,Моргентал Корректор Л.ЛукачРеда ельская Тираж Подписноедарственного комитета по изобретениям и открытиям при ГКНТ С 113035, Москва, Ж, Раушская наб 4/5

СмотретьЗаявка

4865622, 10.09.1990

ЛЕНИНГРАДСКОЕ ОТДЕЛЕНИЕ НАУЧНО-ИССЛЕДОВАТЕЛЬСКОГО ИНСТИТУТА РАДИО

ЛАДА ЮРИЙ АНДРЕЕВИЧ

МПК / Метки

МПК: H03M 13/00, H04L 27/18

Метки: декодирования, кодирования, модема, сигналов, цифрового

Опубликовано: 23.12.1992

Код ссылки

<a href="https://patents.su/5-1783625-ustrojjstvo-dlya-kodirovaniya-i-dekodirovaniya-signalov-cifrovogo-modema.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для кодирования и декодирования сигналов цифрового модема</a>

Предыдущий патент: Устройство для мажоритарного декодирования

Следующий патент: Декодирующее устройство

Случайный патент: Способ художественной обработки изделий из стекла, преимущественно боросиликатного и хрусталя