Устройство для умножения чисел по модулю

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1647563

Авторы: Ирхин, Костенко, Краснобаев, Михеева, Цыба

Текст

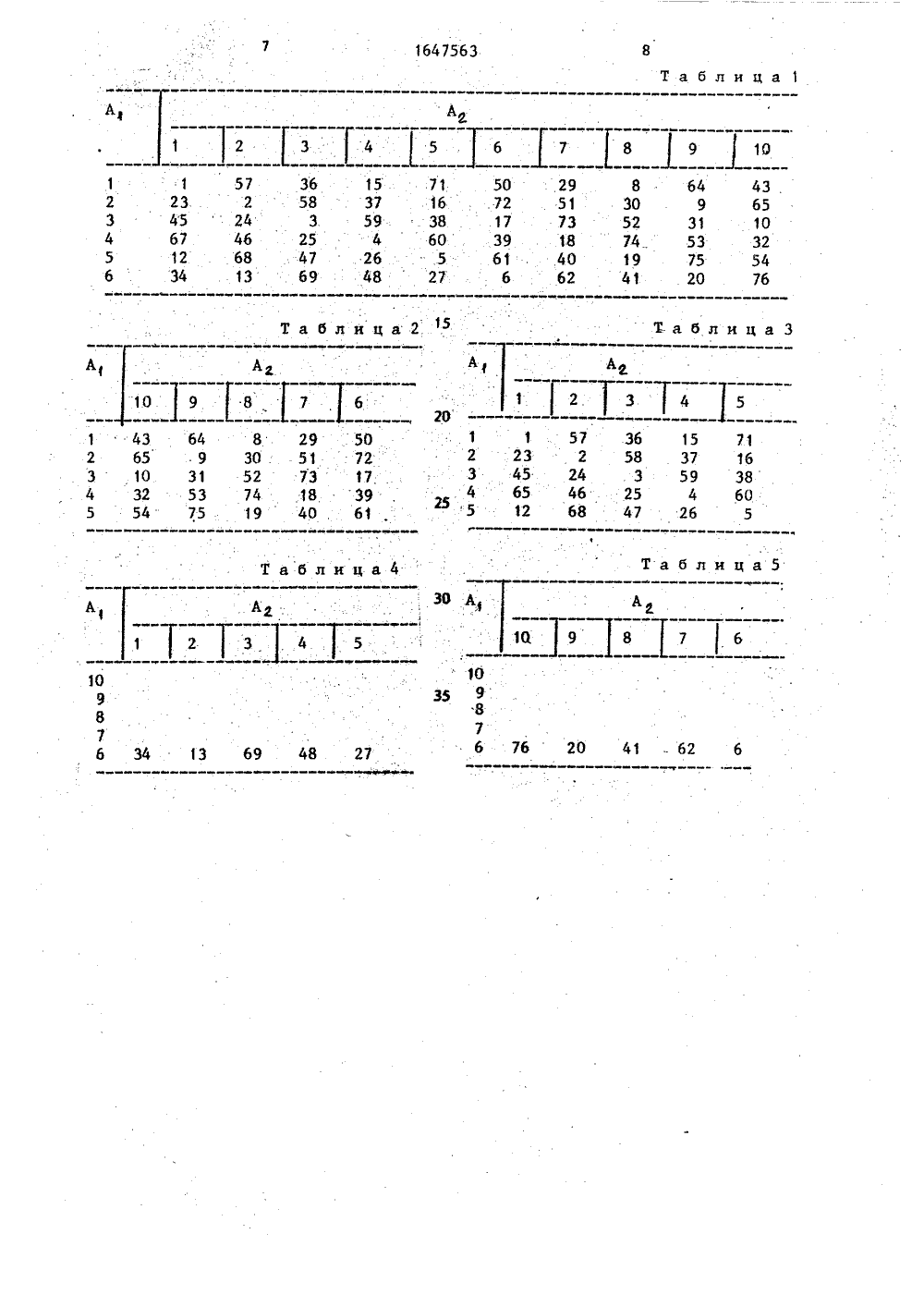

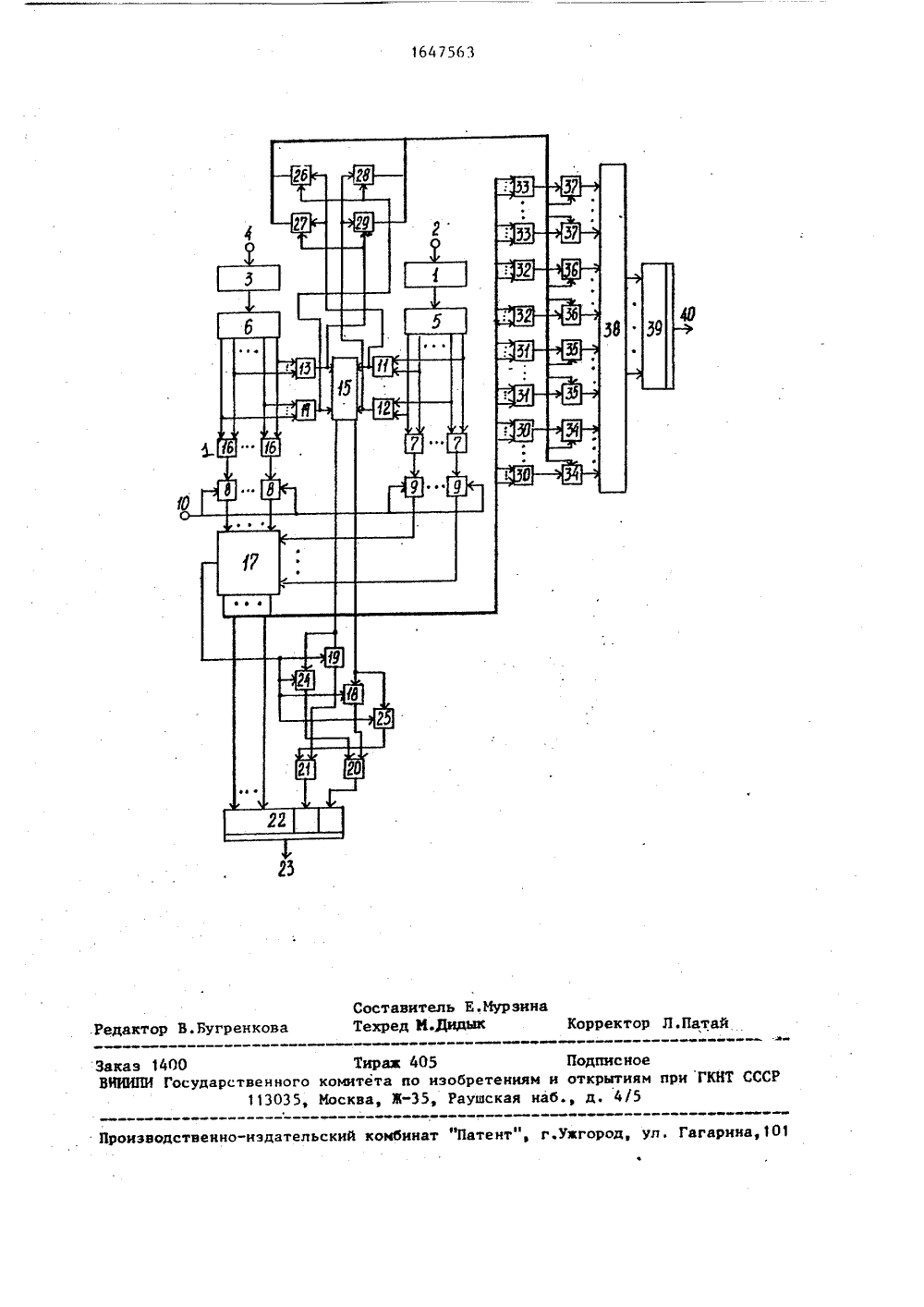

)9) БО)П) 451)5 06 )"." 7/72 ОПИСАНИЕ ИЗОБРЕТЕНИЯ СВИДЕТЕЛЬСТВУ по основанию Р 1 Р (где Рние системы остаточныхнопростые числа, =1,п),лизуется с помощью основтения по основанию РъР- основаклассов, взаимкоторое реа ого изобре 1=7, Р=11 изобрааимосвязь в табл. 1. ена я иэвестрясиадяется 2-4), соотрам квадраичемтветстго понна цы, п чи со перво Велич т.е. 1=77, статГОСУДАРСТВЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТНРЫТИЯМПРИ ГКНТ СССР(56) Авторское свидетельство СССРВ 1095178, кл, С 06 Г 7/72, 1983. (54) УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ ЧИСЕЛ ПО МОДУЛ 1)(57) Изобретение является усовершенствованием устройства по авт,св. У 1095178, относится к области автоматики и вычислительной техники и может быть использовано в вычислительных машинах и устройствах, функционирующих в системе остаточных классов Изобретение относится к автоматике и вычислительной технике, в частности к вычислительным машинам и устройствам, функционирующим в системе оста" точных классов, и является усовершенствованием устройсва по авт.св.Ф 1095178.Целью изобретения является расширение функциональных возможностей за счет реализации функций определения остатка числа по основанию, равному произведению двух оснований в системе остаточных классов.Сущность изобретения состоит в однозначном соответствии мещу остатками числа Сщ А, А А по основаниям Р и Р и остатком этого числа устройства, Цель изобретения - расширение функциональных возможностей засчет реализации функции определения остатка числа по основанию, равному произведению двух оснований в системе остаточных классов. Цель достигается введением четырех элементов И, четырех групп элементов ИЛИ, четырех групп ключей, седьмого элемента ИЛИ, второго выходного регистра. Сущность изобретения состоит в однозначном соответствии между остатками числя С= =(А, А, Ап) по основаниям Р 1 и Р и остатком этого числа ио основанию Р, Р (Р, где =1,п - основания)системы остаточных классов, взаимно .простые числа), которое реализуется с помощью основного изобретения по основанию Р рР . 1 ил., 5 табл. При условии примененнного коммутатора табл.1на четыре таблицы (табл,ветствующие четырем нометов арифметической тяблитаблицы с пятой по восьмвуют номерам квадратов счетвертый соответственнооперандов не кодируется,ки по основанию Р Р =711 Еные 7 или 11, необходимо выполнитьанализом операндов с использованиемсвободных клеток табл. 1 для третьего и четвертого ее квадрантов.В частности, если система остаточныхклассов состоит из двух оснований,то с помощью предлагаемого устройствареализуется перевод чисел из системыостаточных классов в позиционную систему счисления.Для кодирования результата операциинеобходимо иметь семь двоичных разрядов (2 -1=12777).7а чертеже представлена Аункциональная схема устройства, где принятыследующие обозначения: 1 - первыйвходной регистр, 2 - вход первого операнда устройства, 3 - второи входнойрегистр, 4 - вход второго операнда 20устройства, 5 - первый дешиАратор,б - второй дешифратор, 7 - перваягруппа элементов ИЛИ, 8- первая группа ключей, 9 - вторая группа ключей,10 - шина логической единицы, 11 - 14 -25с первого по четвертый элементы ИЛИ,15 - сумматор по модулю два, 16вторая группа элементов ИЛИ, 17 - коммутатор, 18 - первый элемент И, 19 -второй элемент И, 20 - пятый элемент 30ИЛИ, 21 - шестой элемент ИЛИ, 22первый выходной регистр, 23 - первыйвыход устройства, 24 - третий элегмент И, 25 - четвертый элемент И, 26седьмой элемент И, 27 " восьмой элемент И, 28 - пятый элемент И, 29шестой элемент И, 30 - 33 - с третьейпо шестую группы элементов ИЛИ, 3431 - с третьей по шестую группы ключей, 38 - седьмой элемент ИЛИ, 39 - 40второй выходной регистр, 40 - второйвыход устройства.Устройство работает следующим образом,Входные операнды А и А (остатки 45по основанию Р ) по соответствующимвходам 2 и 4 первого и второго операнда в двоичном коде поступают всоответствующие входные регистры 1 н 3и далее через соответствующие дешиАра, тори 5 и 6 и соответствующую пару элементов КПИ 7 и 16 операнды Фи Ьфпоступают на соответствующую пару ключей 9 и 8. Сигнал шины 0 логическойединицы открывает эту пару ключей 9и 8 и сигналы, соответствующие значениям М и р", поступают соответст.венно на первйй и второй входы коммутатора 1. Если у , тогда на нулевом выходе сумматора 15 по модулю два присутствует сигнал, который поступает на первые входы элементов И 18 и 25. Если на выходной управляющей шине коммутатора 17 отсутствует сигнал, то элемент И 18 открыт, и сигнал нулевого выхода сумматора 15 по модулю два через элемент ИЛИ 20 поступает на нулевой вход первого выходного регистра 22. Если на выходную управляющую шину коМчутатора 17 поступает сигнал, то элемент И 25 открыт и сигнал первого выхода сумматора 15 по модулю два через элемент ИЛИ 21 поступает на единичный вход первого выходного регистра 22. Когда,у, то сигнал едиг афничного выхода поступает на первые входы элементов И 19 и 24. Если на выходной управляющей шине коммутатора 17 отсутствует сигнал, то элемент И 19 открыт и сигнал единичного выхода сумматора 15 по модулю два через элемент ИЛИ 21 поступает на единичный вход первого выходного регист- ра 22. Если на выходной управляющей шине коммутатора 17 присутствует сигнал, то элемент И 24 открыт, и сигнал с единичного выхода 15 по модулю два через элемент ИЛИ 20 поступает на нулевой вход первого выходного регистра 22. Одновременно результат операции р 0(вод)Р с выхода коммутатора 11 поступает на соответствующий вход первого выходного регистра 22. Таким образом, в первом выходном регистре 22 содержится результат операции АА(шосР) в КТУ.При рассмотрении работы устройства, реализующего Аункцию определения остатка числа по основанию, равному произведению двух оснований в системе остаточных классов, отметим, что гру- пы элементов ИЛИ (30-33) с третьей по шестую осуществляет преобразование выходного сигнала элемента И коммутатора 17 в соответствующие двоичные представление результата для данного квадрата табл. 1, Определение соответствующего квадранта производится элементами И (28, 20, 26, 27) с пятого по восьмой. Выходной сигнал с одного иэ этих элементов производит открытие соответствующей группы ключей (33-37) с третьей по шестую. Элемент И 28 реализует выбор второго квадранта, И 29 первого, И 26 - третьего и И 27 четвертого.5 647563 6Входные операнды А 1 и А (остатки на четвертый вход второй группы вхо. - 1по основанию соответственно Ри Р 2) дов коммутатора 17. Сигнал вьигнал с выхода йо соответствующим входам 2 и 4 И 29 поступает на управляющие входы первого и второго операнда в двоичном четвертой 35 группы ключей. Че5пы ключей. етверкоде поступают в соответствующие вход- тая 3 1 группа элементов ИЛИ бпрео раные регистры 1 и 3, далее через соот- зует сигнал элемента И кокоммутатора ветствующие дешифраторы 5 и 6 через 17 в двоичные представления соответствующую пару элементов ИЛИ 7 00 111011 =59 результата опе ац и 16 операнды О,и 02 поступают на О согласно табл.б, Результат операции соответствующую пару ключей 9 и 8. через четвертую группу 35 ключейФ Сигнал шины 10 логической единицы от- седьмой 38 элемент ИЛИ поступает во крывает эту пару ключей 9 и 8 и сиг- второй выходной 39 регистр. Это и налы, соответствующие значениям 0, будет результат операции. и ф , поступают соответственно на пер вый и второй входы коммутатора 17, Ф о р м у л а и з о б р е т е н и я Далее элементами И (28, 29, 26, 27)с пятого по восьмой производится вы- Устройство для умножения чисел бор соответствующего квадранта по модулю по авт . св . Р 1095 178, табл. 1, в зависимости от того, в ка". 21 о т л и ч а ю щ е е с я тем, что, ком. диапазоне находятся операнды 0 с целью расширения функциональных и ф (Если 0 А (А )Рато сиг- возможностей за счет Реализапии2 функции определения остатка числа нал поступает с выхода И 29, обозна- по основанию, равному произведению чая выбор второго квадранта). Сигнал 25 двух оснований в системе остаточных выбора квадранта поступает на управ- классов, в него введены йятый шесУ ляющие входы соответствующей группыключей (33-37) с третьей по шестую. . третья, четвертая, пятая и шестая Выходной сигнал коммутатора 17, соот- группы элементов ИЛИ третья, четУ ветствующий результату операции, пре О вертая, пятая и шестая группы эле, образованный соответствующей группой ментов И, седьмой элемент ИЛИ и элементов ИЛИ (30-33) с третьей по , второй выходной регистр, выход шестую в двоичное представление,по- : которого соединен с вторым выходом ступает на информационные входы груп- устройства, а информационный входчпы Ключеи (33-37) и с выхода одной кз 35 с выходом седьмого элемента ИЛИ, них (при втором квадранте выбирается входы которого соединены с выходами четвертая группа ключей 34). Через элементов И третьей, четвертой, пяседьмои элемент ИЛИ 38 результат по- той и шестой групп, первые входы ступает на вход второго выходного ре- которых соединены с выходами элегистра 39, с выхода которого - на 4 О ментов ИЛИ соответственно третьей, второй выход 40 устройства. четвертой,. пятой и шестой групп, аРассмотрим пример конкретного вы- управляющие входы - соответственно полнения операции определения остатка с выходами пятого, шестого, седьмочисла по основанию, равному произве-го и восьмого элементов И, выход дению двух оснований в системе оста-. 45 первого элемента ИЛИ соединен с перточных классов . Пусть Р =7, Р=11. выми входами седьмого и восьмогоНеобходимо определить остаток чис- элементов И, выход второго элемента ла по основанию 77, если остаток чис- ИЛИ соединен с первыми входами пятола по основанию Р равен 3, а остаток го и шестого элементов И, выход трепо основанию Р 2 равен 4. В этом слу О тьего элемента ИЛИ соединен с вточае реализуется второй квадрант, так рыми входами шестого и восьмого элекак ОА (А ) 5 т.е. сигнал на в -( ) , .е. сигнал на вы- ментов И, выход четвертого элемента бор группы ключей (33-37) поступает ИЛИ соединен с вторыми, входами пятоЭВходные операнды А 1=0011 и А =0100 55 ционные выходы коммутатора соединены поступают через соответствуп р тветствующие эле- с входами соответствующих элементовменты устройства на третий вход пер, - ИЛИ третьей, четвертой, пятой и шесвой группы входов коммутатора 17 и той лпзпп.Р16475 бЗ Составитель Е.ИурзинТехред М.Дидык Корректор Л.Патай Редактор В.Бугренко ательский комбинат фйатент", г.ужгород, ул, Гагарина, 10 роиэводственно аказ 1400 Тираж 405ЯИИПИ Государственного комитета до из113035, Иосква, Ж,тениям и ская наб одписноеткрытиям ври ГКНТ ССд. 4/5

СмотретьЗаявка

4711759, 27.06.1989

ХАРЬКОВСКОЕ ВЫСШЕЕ ВОЕННОЕ КОМАНДНО-ИНЖЕНЕРНОЕ УЧИЛИЩЕ РАКЕТНЫХ ВОЙСК ИМ. МАРШАЛА СОВЕТСКОГО СОЮЗА КРЫЛОВА Н. И

КРАСНОБАЕВ ВИКТОР АНАТОЛЬЕВИЧ, ИРХИН ВАЛЕРИЙ ПЕТРОВИЧ, КОСТЕНКО ИГОРЬ КОНСТАНТИНОВИЧ, МИХЕЕВА ИРИНА ВАСИЛЬЕВНА, ЦЫБА МИХАИЛ ИВАНОВИЧ

МПК / Метки

МПК: G06F 7/72

Метки: модулю, умножения, чисел

Опубликовано: 07.05.1991

Код ссылки

<a href="https://patents.su/5-1647563-ustrojjstvo-dlya-umnozheniya-chisel-po-modulyu.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для умножения чисел по модулю</a>

Предыдущий патент: Устройство для сортировки двоичных чисел

Следующий патент: Многоканальное устройство для приоритетного подключения источников информации к мультишинной магистрали

Случайный патент: 401356