Устройство для амплитудной селекции аналоговых сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

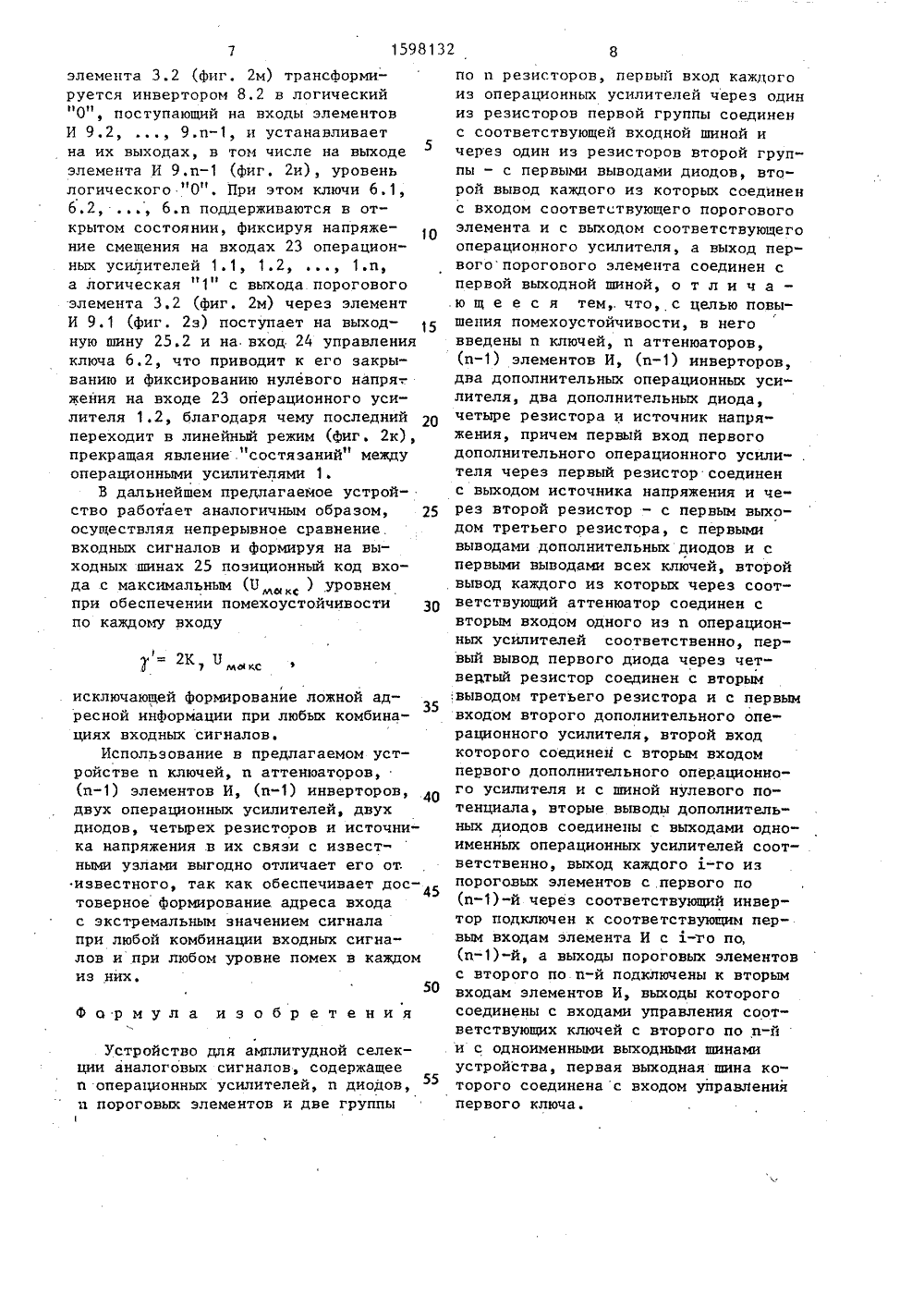

(19) (11 98132 1 0 1)5 Н 03 К 5/04 ГОСУДАРСТВЕННЫЙ НОМИТЕТПО ИЗОБРЕТЕНИЯМ И ОТКРЫТИЯМПРИ ГКНТ СССР ИЗОБРЕТЕТЕЛЬСТВУ Я(71) Институт проблем управл(56) Блоки селектирования тБСЛ-П, БСЛ-Ш. ЦНИИТЭИПриборния. Отраслевой каталог навыпускаемое и перспективноеванне У 9. Т. 4, вып. 3, 19с. 17-20, рис. 24. ия иков в строе- ерийно ор(54) УСЛЕКЦИИ АМПЛИТ ЙСТВО ДЛЯАЛО ГОВНХ НЛЛ к импульс пользова-. оситсбыть ых сигнах контротре мал тег также в к Фиа ПИСАНИЕ К АВТОРСКОМУ(57) Изобретение от ной технике и может но для селекции экс лов вмногоканальных ля и диагностики, а 2тических системах экстремального управления и регулирования. Цель изобретения - повышение помехоустойчивости. Введение в устройство для амплитудной селекции аналоговых сигналов, содержащее и операционных усилителей 1, и диодов 2, и пороговых элементов 3 и две группы резисторов 4, 5, и ключей 6, и аттенюаторов 7 (и) элементов И 9, (и) инверторов 8, двух дополнительных операционных усилителя 11, 12, двух дополнительных диодов 13, 14, четырех резисторов 15-18 и источника 10 напряжения позволяет оперативно изменять величину порогового уровня. При этом обеспечивается детермирование результатов селекции при любой комбинации входных сигналов и любом уровне помех, т.е. повышается помехоустойчивость. 2 ил.Изобретение относится к импульсной технике и может быть использовано для селекции экстремальных сигналов в многоканальных системах контроля и диагностики, а также в кибернетических системах экстремального управления и регулирования.Цель изобретения - повышение помехоустойчивости. 1 ОНа фиг. 1 представлена структурная схема устройства для амплитудной селекции аналоговых сигналов; на фиг. 2- временные диаграммы, поясняющие работу устройства. 15Устройство для амплитудной селекции аналоговых сигналов содержит и операционных усилителей 1, и диодов2; и пороговых элементов 3, первую группу из и резисторов 4, вторую 20 группу из и резисторов 5, и ключей 6, и аттенюаторов 7, (и) инверторов 8, (и) элементов И 9, источник 110 напряжеция, операционный усилитель (и+1) 11, операционный усилитель (и+2) 12, дополнительные диоды 13 и 14, а также с первого по четвертый резисторы 15-18, при этом инвертирующий первый вход 19 каждого из операционных усилителей 1 через один из резисторов 4 первой группы соединен с соответствующей входной шиной 20 и через один из резисторов 5 второй группы соединен.с одним из выводов резистора 18 и с первыми выводами диодов 2, второй вывод каждого из которых соединен с выходом соответствующего операционного усилителя 1 и с входом соответствующего порогового элемента 3. Второй вывод резистора 18 соединен с инвертирующим первым входом 21 операционного усилителя 12 и через резистор 17 с первыми выводами ключей 6, с первыми выводами дополнительных диодов 13, 14 и с пер вым выводом резистора 16, второй вывод которого соединен с инвертирующим первым входом 22 операционного. усилителя 11 и через резистор 15 с ВыхОДОм источника 10 напряжения, Вто рой вывод каждого из ключей 6 через соответствующий аттенюатор 7 соединен с вторым неинвертирующим входом 23 соответствующего операционного усилителя 1, выход порогового элемента55 3.1 соединен с входом 24 управления ключа 6.1 и с выходной шиной 25,1, выход каждого -го из пороговых элементов 3.1.З.пчеред соответствующий инвертор 8 соединен с входами соответствующих элементов И 9,выход каждого из пороговых элементов3.2, , З,п через один из элементов И 9 соединен с входом 24 управления соответствующего ключа 6 и ссоответствующей выходной шиной 25,а второй неинвертирующий вход 26операционного усилителя 11 и второйнеинвертирующий вход 27 операционного усилителя 12 соединены с шинойнулевого потенциала 28.Указанное на фиг. 1 направление,включения диодов 2, 13 и 14 соответствует наличию положительных сигналовна входных шинах 20. При этом напряжение на выходе источника 10 имеетотрицательную полярность. Для работыже с отрицательными входными сигналами полярность включения упомянутыхдиодов и знак напряжения на выходеисточника 10 должны быть изменены наобратные,В предлагаемом устройстве пороговые элементы 3 имеют нулевой уровеньсрабатывания, а параметры прочих элементов удовлетворяют следующим условиям:ЦаНщфФК24 5Р 15 Ыгде Б - напряжение источника 10;Ю - прямое падение напряженияна диодах 2;К - коэффициент усиления операционных усилителей- относительный уровень помех во входных сигналах;К - коэффициент передачи атта 1нюаторов 7;К - сопротивления соответствующих резисторовУстройство работает следующим образомПредположим, что в некоторый момент времени на входных шинах 20,в частности на шинах 20, 1 (фиг. 2 а),20,2 (фиг, 2 б) и 20.п (фиг. 2 в),.имеется нулевой уровень напряжения, поступающего через соответствующие ре 1598132зисторы 4 на инвертирующие входы 19 операционных усилителей 1.Предположим также, что при этом на вьмоде одного из операционных усилителей 1, например на выходе уси 5 лителя 1. 1 (фиг. 2 г), присутствует некоторое отрицательное напряжение, открывающее диод 2.1 и устанавливающее нулевое напряжение на его первом выводе (фиг. 2 д), а также фиксирующее логическую "1" на выходе порогового элемента 3.1 (фиг, 2 е), которая поступает на выходную шину 25.1 и на вход 24 управления ключа 6.1, переводя его в разомкнутое состояние,Нулевой уровень напряжения с первого вывода диода 2. 1 (фиг. 2 д) через резистор 18 поступает на инвертирующий вход 21 операционного усилителя 20 12, на неинвертирующий вход 27 которого поступает нулевое напряжение с шины 28. Напряжение Б с выхода ис 1 оточника 10 через резистор 15 поступает на инвертирующий вход 22 опе рационного усилителя 11, переводя его в линейный режим и формируя на первом выводе диода 13 и на первом выводе резистора 17 напряжение П (фиг, 2 ж), поступающее также на пер вые входы ключей б.Логическая "1" с выхода порогового элемента 3.1 (фиг. 2 е) трансформируется инвертором 8.2 в логический "0", поступающий на входы элементов И 9 и закрывающий их. При этом на выходах элементов И 9, в частности на выходе элемента И 9.1 (фиг, 2 з) и на выходе элемента И 9;и(фиг.2 и), ,формируются уровни логического "0", поступающие на соответствующие выходные шины 25.2.25.п и на входы управления 24 ключей 6.2, , б.п, что приводит к их замыканию и поступлению сигнала У с первого вывода диода 13 (фиг2 ж) через аттенюаторы 7.2, , 7.п на выходы 23 операционных усилителей 1.2, ; 1.п, подтверждая на их выходах, в частности на выходе операционного усилителя 50 1.2 (фиг. 2 к) и усилителя 1.п (фиг. 2 л), положительное напряжение насыщения, запирающее диоды 2.2 2.п и устанавливающее на выходах пороговых элементов 3.2 (фиг, 2 м)ф 55З,п (фиг. 2 н) уровни логического "О".Такое состояние предлагаемого устройства является абсолютно устойчивым, фиксирующим адрес только .од - ного входного сигнала и исключающимего спонтанное изменение.При увеличении сигнала на одной из входных шин 20, например на той же шине 20.1 (фиг. 2 а), напряжение на выходе операционного усилителя1.1 соответствующим образом изменяется, что приводит к соответствующему изменению напряжения на первом выводе диода 2.1 (фиг. 2 д), поступающего через. резистор 18 на инвертирующий вход 21 операционного усилителя 12, вследствие чего в соответствующий момент времени операционные усилители 11 и 12 меняют режим работы, диоды 13 и 14 переключаются и напряжение на первом выводе первого из них увеличивается (фиг, 2 ж), что приводит к увеличению напряжения на входах 23 операционных усилителей 12 1.п до такого уровня, что сигнал помехи на входных шинах 20 не приводит к изменению режимов операционных усилителей 1 и исключает искажение формируемого адреса.Предположим далее, что начиная с некоторого момента времени сигналы на некоторых входных шинах, например на шинах 20.2 и 20.п, начинают синхронно увеличиваться (фиг. 2 б, в), превышая уровень сигнала на шине 20.1 (фиг, 2 а). При этом в момент, когда разность сигналов превысит допустимый уровень помех, напряжение на выходах операционных усилителей 1.2 и 1.п меняет знак (фиг. 2 к, л), что приводит к появлению логических 1 на выходах пороговых элементов 3,2 и З.п (фиг. 2 м, н), а напряжение на выходе операционного усилителя 1 фиксируется на уровне положительного напряжения насыщения (фиг. 2 г), устанавливая логический "0" на выходе порогового элемента 3.1 (фиг. 2 е), на выходной шине 25.1 и на входе 24 управления ключа 6,2, что приводитк его открыванию и появлению напряжения смещения на входе 23 операционного усилителя 1.1, подтверждающего положительное напряжение на его выходе (фиг. 2 г). Логический "0" с выхода порогового элемента 3.1 (фиг, 2 е) поступает на вход инвертора 8.1, логическая "1".с выхода кото-рого поступает на входы элементов И 9.1, . , 9.пи разблокирует их, а логическая "1" с выхода пороговогоэлемента 3.2 (фиг, 2 м) трансформируется инвертором 8.2 в логический "О", поступающий на входы элементов И 9.2, , 9.п, и устанавливает на их выходах, в том числе на выходе элемента И 9.п(фиг. 2 и), уровень логического "О". При этом ключи 6.1, 6.2, , б.п поддерживаются в открытом состоянии, фиксируя напряжение смещения на входах 23 операционных усилителей 1.1, 1.2, , 1.п, а логическая "1" с выхода. порогового элемента 3.2 (фиг. 2 м) через элемент И 9.1 (фиг. 2 з) поступает на выходную шину 25.2 и на вход 24 управления ключа 6.2, что приводит к его закрыванию и фиксированию нулевого напря-, жения на входе 23 операционного усилителя 1.2, благодаря чему последний переходит в линейный режим (фиг. 2 к), прекращая явление "состязаний" между операционными усилителями 1.В дальнейшем предлагаемое устройство работает аналогичным образом, 25 осуществляя непрерывное сравнение.входных сигналов и формируя на выходных шинах 25 позиционный код входа с максимальным Ю) уровнем при обеспечении помехоустойчивости 30 по каждому входу3 = 1 чюкс фГисключаюцей формирование ложной ад 35ресной информации при любых комбинациях входных сигналов.Использование в предлагаемом устройстве п ключей, и аттенюаторов,(и) элементов И, (и) инверторов, 40двух операционных усилителей, двухдиодов, четырех резисторов и источника напряжения в их связи с известными узлами выгодно отличает его от.известного, так как обеспечивает дос товерное формирование адреса входас экстремальным значением сигналапри любой комбинации входных сигналов и при любом уровне помех в каждомиз них,50Формула изобр етенияУстройство для амплитудной селекции аналоговых сигналов, содержащее и операционных усилителей, и диодов, п пороговых элементов и две группы 1 по и резисторов, первый вход каждогоиз операционных усилителей через одиниз резисторов первой группы соединенс соответствующей входной шиной ичерез один из резисторов второй группы - с первыми выводами диодов, второй вывод каждого из которых соединенс входом соответствуюцего пороговогоэлемента и с выходом соответствуюцегооперационного усилителя, а выход первогопорогового элемента соединен спервой выходной шиной, о т л и ч а -(и) элементов И, (и) инверторов,два дополнительных операционных усилителя, два дополнительных диода,четыре резистора и источник напряжения, причем первый вход первогодополнительного операционного усили- .теля через первый резистор соединенс выходом источника напряжения и через второй резистор - с первым выходом третьего резистора, с первымивыводами дополнительных диодов и спервыми выводами всех ключей, второйвывод каждого из которых через соответствующий аттенюатор соединен свторым входом одного из и операционных усилителей соответственно, первый вывод первого диода через четвертый резистор соединен с вторым:выводом третьего резистора и с первымвходом второго дополнительного операционного усилителя, второй входкоторого соединен с вторым входомпервого дополнительного операционного усилителя и с шиной нулевого потенциала, вторые выводы дополнительных диодов соединены с выходами одноименных операционных усилителей соответственно, выход каждого -го изпороговых элементов с первого по(и)-й через соответствующий инвертор подключен к соответствуюцим первым входам элемента И с д-го по,(п)-й, а выходы пороговых элементовс второго по п-й подключены к вторымвходам элементов И, выходы которогосоединены с входами управления соответствующих ключей с второго по и-йи с одноименными выходными шинамиустройства, первая выходная шина которого соединена с входом управленияпервого ключа.оставитель Н.Маркехред Л.Олийнык Тираж 665 Подписноемитета по изобретениям и открытиям при ГКНТ СС сква, Ж, Раушская наб., д. 4/5

СмотретьЗаявка

4635312, 16.01.1989

ИНСТИТУТ ПРОБЛЕМ УПРАВЛЕНИЯ

ПАЩЕНКО ФЕДОР ФЕДОРОВИЧ, СУДАРИКОВ ВЛАДИМИР НИКОЛАЕВИЧ

МПК / Метки

Метки: амплитудной, аналоговых, селекции, сигналов

Опубликовано: 07.10.1990

Код ссылки

<a href="https://patents.su/5-1598132-ustrojjstvo-dlya-amplitudnojj-selekcii-analogovykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для амплитудной селекции аналоговых сигналов</a>

Предыдущий патент: Генератор случайного потока импульсов

Следующий патент: Устройство подавления дребезга контактов

Случайный патент: Учебный прибор по физике