Устройство микропрограммного управления

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1536380

Автор: Карпов

Текст

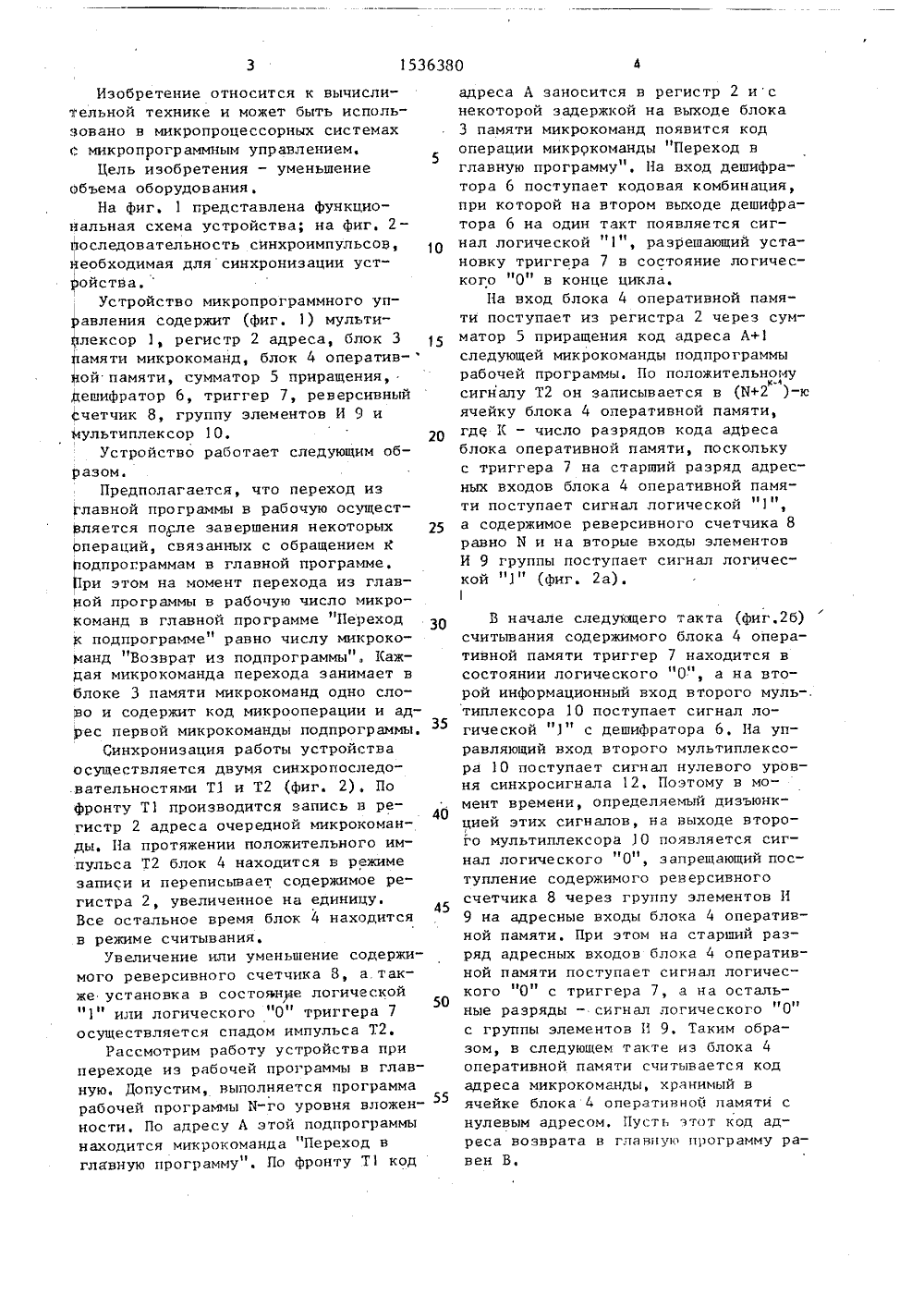

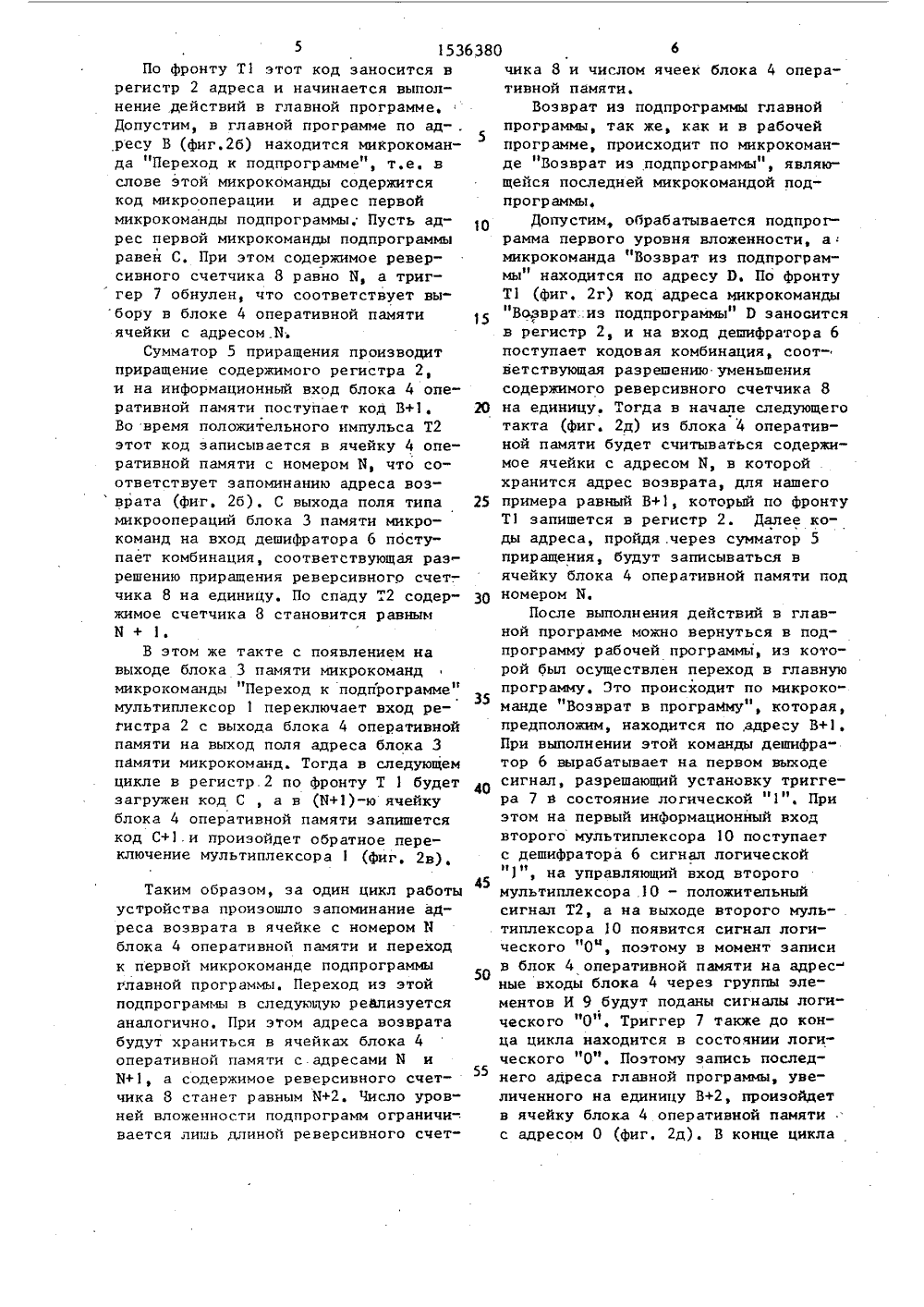

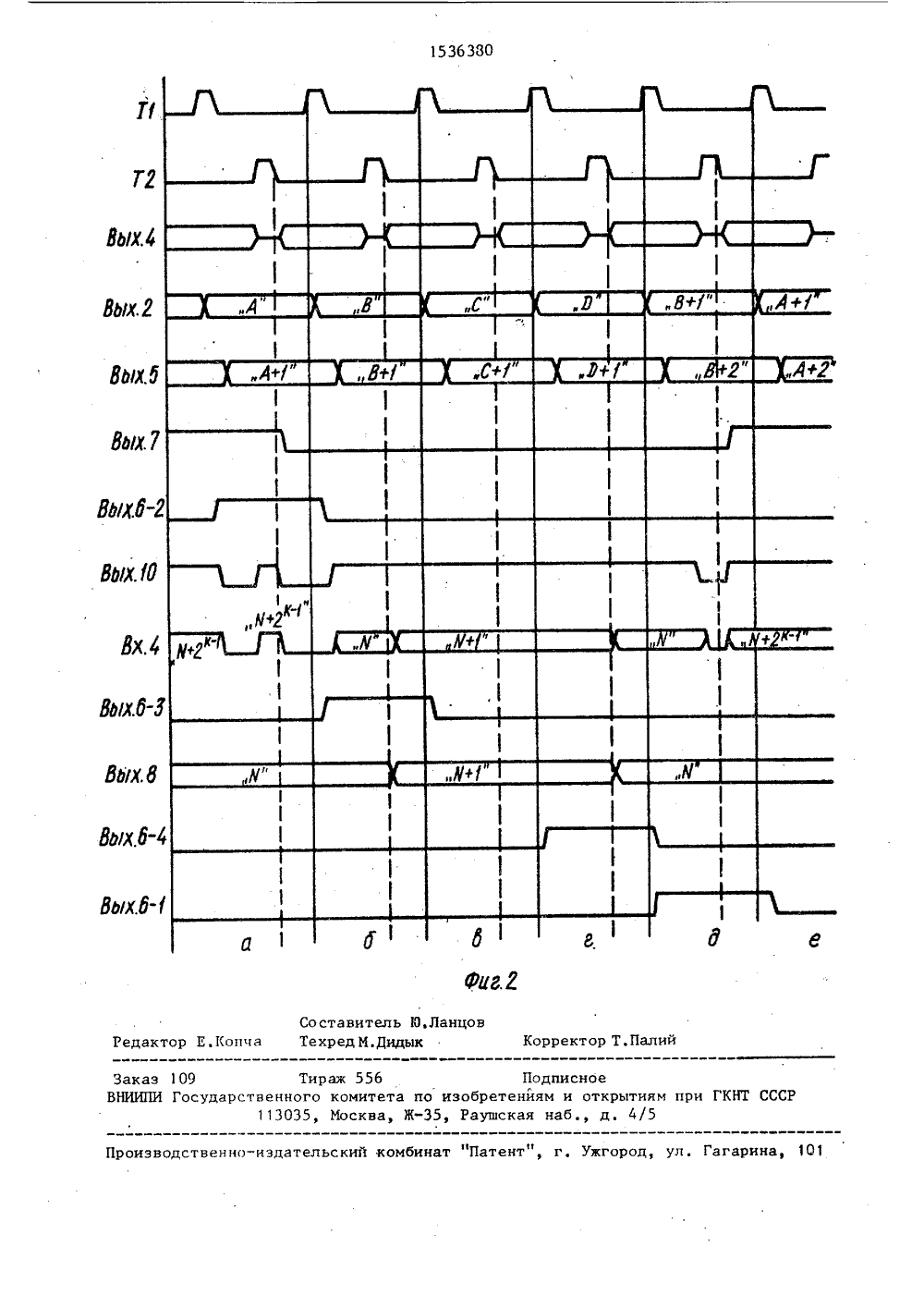

5 10 15 20 25 30 35 40 45 50 55 Изобретение относится к вычислительной технике и может быть использовано в микропроцессорных системахС микропрограммным управлением.Цель изобретения - уменьшениеобъема оборудования,На фиг. 1 представлена функциональная схема устройства; на фиг. 2 -Последовательность синхроимпульсов,необходимая для синхронизации устройства,Устройство микропрограммного управления содержит (фиг, 1) мультиплексор 1, регистр 2 адреса, блок 3йамяти микрокоманд, блок 4 оператив-ной памяти, сумматор 5 приращения,дешифратор 6, триггер 7, реверсивныйсчетчик 8, группу элементов И 9 имультиплексор 10.Устройство работает следующим образом.Предполагается, что переход изглавной программы в рабочую осуществляется после завершения некоторыхОпераций, связанных с обращением к1 одпрограммам в главной программе,11 ри этом на момент перехода из главНой программы в рабочую число микроКоманд в главной программе "Переходподпрограмме" равно числу микрокоИанд "Возврат из подпрограммы", 11 аждая микрокоманда перехода занимает вблоке 3 памяти микрокоманд одно слово и содержит код микрооперации и адрес первой микрокоманды подпрограммы.Синхронизация работы устройстваосуществляется двумя синхропоследо.вательностями Т 1 и Т 2 (фиг. 2), Пофронту Т 1 производится запись в регистр 2 адреса очередной микрокоманды, На протяжении положительного импульса Т 2 блок 4 находится в режимезаписи и переписывает содержимое регистра 2, увеличенное на единицу.Все остальное время блок 4 находитсяв режиме считывания,Увеличение или уменьшение содержимого реверсивного счетчика 8, а также установка в состоянуе логической"1" или логического "0" триггера 7осуществляется спадом импульса Т 2.Рассмотрим работу устройства припереходе из рабочей программы в главную. Допустим, выполняется программарабочей программы Б-го уровня вложенности. По адресу А этой подпрограммынаходится микрокоманда "Переход вглавную программу". По фронту Т 1 код адреса А заносится в регистр 2 ис некоторой задержкой на выходе блока 3 памяти микрокоманд появится код операции микрокоманды "Переход в главную программу", На вход дешифратора 6 поступает кодовая комбинация, при которой на втором выходе дешифратора 6 на один такт появляется сигнал логической "1", разрешающий установку триггера 7 в состояние логического "0" в конце цикла.На вход блока 4 оперативной памяти поступает из регистра 2 через сумматор 5 приращения код адреса А+1 следующей микрокоманды подпрограммы рабочей программы, По положительномук-л сигналу Т 2 он записывается в (М+ 2 ) -к ячейку блока 4 оперативной памяти , гд е 1 - число разрядов кода адр е с а блока оперативной памяти , поскольку с триггера 7 на старший разряд адресных входов блока 4 оперативной памяти поступает сигнал логической " 1 ", а содержимое реверсивного счетчика 8 равно И и на вторые входы элементов И 9 группы поступает сигнал логич еской " 1 " ( фиг . 2 а) .1 В начале следующего такта (фиг,2 б) считывания содержимого блока 4 оперативной памяти триггер 7 находится в состоянии логического "О", а на второй информационный вход второго муль-. типлексора 10 поступает сигнал логической "1" с дешифратора 6, На управляющий вход второго мультиплексора 10 поступает сигнал нулевого уровня синхросигнала 12, Поэтому в момент времени, определяемый дизъюнкцией этих сигналов, на выходе второго мультиплексора 10 появляется сигнал логического 0, запрещающий поступление содержимого реверсивного счетчика 8 через группу элементов И 9 на адресные входы блока 4 оперативной памяти, При этом на старший разряд адресных входов блока 4 оперативной памяти поступает сигнал логического "О" с триггера 7, а на остальные разряды - сигнал логического "Он с группы элементов И 9, Таким образом, в следующем такте из блока 4 оперативной памяти считывается код адреса микрокоманды, хранимый в ячейке блока 4 оперативно 0 памяти с нулевым адресом, Пусть этот код адреса возврата в главную программу ра - вен В.6380 5 153По фронту Т 1 этот код заносится в регистр 2 адреса и начинается выполнение действий в главной программе, Допустим, в главной программе по ад- . ресу В (фиг,2 б) находится микрокоманда "Переход к подпрограмме", т.ев слове этой микрокоманды содержится код микрооперации и адрес первой микрокоманды подпрограммы; Пусть адрес первой микрокоманды подпрограммы равен С, При этом содержимое реверсивного счетчика 8 равно И, а триг гер 7 обнулен, что соответствует выбору в блоке 4 оперативной памяти ячейки с адресом.И.Сумматор 5 приращения производит приращение содержимого регистра 2, и на информационный вход блока 4 оперативной памяти поступает код В+1. Во время положительного импульса Т 2 этот код записывается в ячейку 4 оперативной памяти с номером Б, что соответствует запоминанию адреса воз врата (фиг. 2 б), С выхода поля типа микроопераций блока 3 памяти микро- команд на вход дешифратора 6 поступает комбинация, соответствующая разрешению приращения реверсивного счет-. чика 8 на единицу, По спаду .2 содержимое счетчика 8 становится равным И+ 1.В этом же такте с появлением на выходе блока 3 памяти микрокоманд микрокоманды "Переход к подпрограмме мультиплексор 1 переключает вход регистра 2 с выхода блока 4 оперативной памяти на выход поля адреса блока 3 памяти микрокоманд. Тогда в следующем цикле в регистр.2 по фронту Т 1 будет загружен код С , а в (0+1)-ю ячейку блока 4 оперативной памяти запишетсякод С+1,и произойдет обратное переключение мультиплексора 1 (фиг, 2 в),Таким образом, за один цикл работы устройства произошло запоминание адреса возврата в ячейке с номером Ю блока 4 оперативной памяти и переход к первой микрокоманде подпрограммы главной программы, Переход из этой подпрограммы в следующую реализуется аналогично. При этом адреса возврата будут храниться в ячейках блока 4 оперативной памяти с.адресами Б и И+1, а содержимое реверсивного счетчика 8 станет равным И+2. Число уровней вложенности подпрограмм ограничи-. вается лишь длиной реверсивного счет 5 1 О 15 20 25 30 35 40 45 50 55 чика 8 и числом ячеек блока 4 оперативной памяти,Возврат из подпрограммы главнойпрограммы, так же, как и в рабочейпрограмме, происходит по микрокоманде "Возврат из подпрограммы", являющейся последней микрокомандой подпрограммы,Допустим, обрабатывается подпрограмма первого уровня вложенности, амикрокоманда "Возврат из подпрограммы" находится по адресу О. По фронтуТ 1 (фиг. 2 г) код адреса микрокоманды"Возврат.из подпрограммы" Р заноситсяв регистр 2, и на вход дешифратора 6поступает кодовая комбинация, соответствующая разрешению уменьшениясодержимого реверсивного счетчика 8на единицу. Тогда в начале следующеготакта (фиг. 2 д) из блока 4 оперативной памяти будет считываться содержимое ячейки с адресом И, в которойхранится адрес возврата, для нашегопримера равный В+1, который по фронтуТ 1 запишется в регистр 2. Далее коды адреса, пройдя .через сумматор 5приращения, будут записываться вячейку блока 4 оперативной памяти подномером Б,После выполнения действий в главной программе можно вернуться в подпрограмму рабочей программы из которой был осуществлен переход в главнуюпрограмму. Это происходит по микрокоманде "Возврат в программу", которая,предположим, находится по,адресу В+1.При выполнении этой команды дешифратор 6 вырабатывает на первом выходесигнал, разрешающий установку триггера 7 в состояние логической "1". Приэтом на первый информационный входвторого мультиплексора 10 поступаетс дешифратора 6 сигнал логической"1", на управляющий вход второгомультиплексора 10 - положительныйсигнал Т 2, а на выходе второго мультиплексора )О появится сигнал логического "0", поэтому в момент записив блок 4 оперативной памяти на адрес-ные входы блока 4 через группы элементов И 9 будут поданы сигналы логического "О". Триггер 7 также до конца цикла находится в состоянии логического 0. Поэтому запись последнего адреса главной программы, увеличенного на единицу В+2, произойдетв ячейку блока 4 оперативной памятис адресом 0 (фиг. 2 д). В конце циклапо спаду Т 2 триггер 7 устанавливается в состояние логической "1" и считывание следующего адреса микрокоманды из блока 4 оперативной памяти (фиг. 2 е) будет осуществляться из ячейки с номером И+2 , поскольку од в реверсивном счетчике 8 сохранил свое значение, равное И, а на 1старший разряд входа адреса блока 4 перативной памяти поступает логиеская "1" с триггера 7, 3 этой ячейе хранится код адреса, для данного римера равный А+1, Далее этот код , дреса по фронту Т 1 заносится в реистр 2 и выполняются операции в рабочей программе,1 О 15 Переход низ них в раб вляется точи ной программ что адреса в ячейки блока такими номер разряд адрес кой "1 п,озврат а подпрограммы очей программе о так же, как и е, с той лишь р озврата записыв 4 оперативнойкоторых осущест главазницеи аются в памяти с старший 25 логичесами, в а ячейк вен ф о р м у л а яЗО и з о б р е т е в и Устройство микропрограммного управления, содержащее первый мульти,плексор, регистр адреса блок памятимикрокоманд, блок оперативной памяти,сумматор приращения, дешифратор,35триггер, реверсивный счетчик, группуэлементов И, причем первый информаци,онный вход первого мультиплексорасоединен с выходом поля адреса блокапамяти микрокоманд, второй информаци Оонный вход первого мультиплексорасоединен с выходом блока оперативнойпамяти, выход первого мультиплексорасоединен с информационным входом регистра ацреса, выход которого соединен с адресным входом блока памятимикрокоманд, а также с входом сумматора приращения, выход которого подключен к информационному входу блокаоперативной памяти, выход поля микроопераций блока памяти микрокоманд является выходом устройства, выход полятипа микрокоманды блока памяти микрокоманд соединен с входом денифратора,первый и второй выходы дешифраторасоединены соответственно с входамиустановки в "1" и в "О" триггера,третий и четвертый выходы дешифратора соединены соответственно с суммирующим и вычитающим входами реверсивного счетчика, выходы которого соединены с первыми входами элементов Игруппы, выходы которых соединены садресными входами младших разрядовблока оперативной памяти, первый тактовый вход устройства подключен ксинхровходу регистра адреса, второйтактовый вход устройства подключен ксинхровходам триггера и реверсивногосчетчика, а также к входу чтения-записи блока оперативной памяти, о тл и ч а ю щ е е с я тем, что, с целью уменьшения объема оборудования,оно содержит второй мультиплексор,причем выход триггера соединен с адресным входом старшего разряда блокаоперативной памяти, управляющий входпервого мультиплексора соединен стретьим выходом,цешифратора, первыйи второй выходы,цешифратора соединены соответственно с первым й вторыминформационными входами второго мультиплексора, управляющий вход которого соединен с вторым тактовым входомустройства, выход второго мультиплексора соединен с вторыми входами элементов И группы,/х.4 Вых юг АХ Составитель 1 О,Ланцовактор Е,1(опча Техред М,Дидык Корректор Т. Палий В при ГКНТ СССР изводственио-издательский комбинат "Патент",ул. Гагари жг з 109 Тираж 556 НИИПИ Государственного комитета по 113035, Москва, Ж

СмотретьЗаявка

4415567, 25.04.1988

ПРЕДПРИЯТИЕ ПЯ А-7162

КАРПОВ АНАТОЛИЙ ФЕДОРОВИЧ

МПК / Метки

МПК: G06F 9/22

Метки: микропрограммного

Опубликовано: 15.01.1990

Код ссылки

<a href="https://patents.su/5-1536380-ustrojjstvo-mikroprogrammnogo-upravleniya.html" target="_blank" rel="follow" title="База патентов СССР">Устройство микропрограммного управления</a>

Предыдущий патент: Микропрограммное устройство управления

Следующий патент: Устройство циклического приоритета

Случайный патент: Щетка для электрической машины