Устройство для приема многопозиционных дискретных частотно фазоманипулированных сигналов

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1501301

Авторы: Барлабанов, Литвиненко, Посохов

Текст

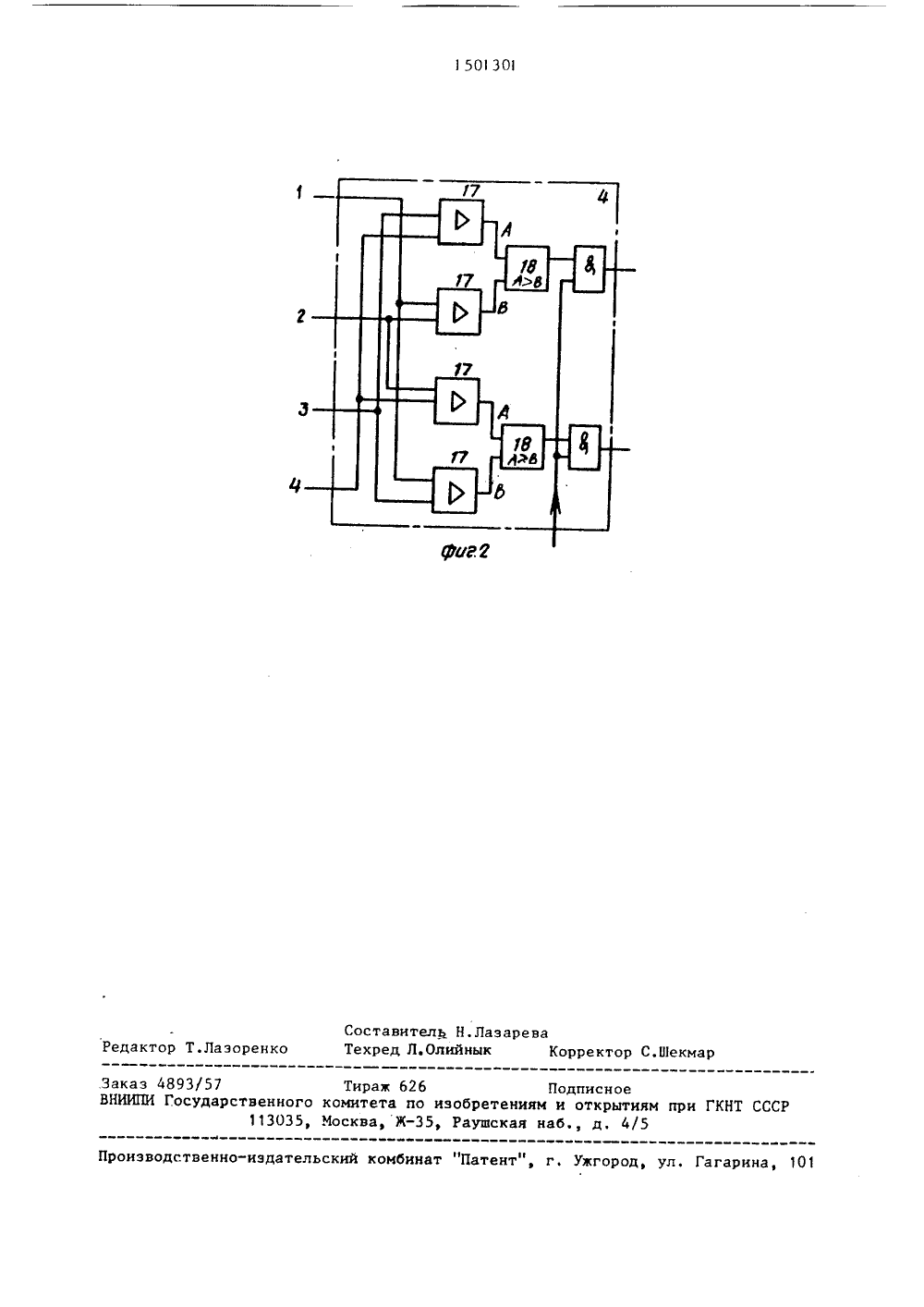

3 150 ОИ:эс бретецттетцстттся к рлдцосвя -10 15 30 45 зц, в частности к устрсйсттлм для брл боткц псевдослучайных дттс кре тцых чттстотО фл эоыдцттпузтироэцт х сигналов 1 тЧФМС).Цель ттзобретенття - повышение помехоустойчивости за счет уво.тцчецця ансамбля мцогопозццццных сц ндлов,д фиг, 1 изображена структурная электрическая схема предложенного устройсттэл; цд фиг. 2 - схема решающего блока устройства.Устройство содержит блок 1 свертки, полосовые фильтры 2, блок 3 опорных сигналов, решающий блок ст, регистры 5 сдвига, блок 6 памяти, элементы 7 равнозначности, сумматор 8, регистр 9 памяти, компаратор 10, буферный регистр 11, счетчик 12, генератор 13 тактовых импульсов, регистр 1 А инФормации, делитель 15, деиптфрд - тор 16.Устройство работает следующим образом.Принимаемый ДсИ 1 С поступает на первый вход блока 1 свертки, где цсуществляется свертка фазомаццпулированного ФМ) по закону псевдослучайной последовательности (ПСП) элемента Мс 1 С. В зависимости от номера частотной позиции ь элемента МЧС т,з. Е 1. . . и) отклик блока 1 будет появляться на выходе фильтра 2, наст. роенного на эту частоту. Блок 1 свертки може г быть выполнен в виде ттеремттоэтгттеля, тогда на его второй вход ттоступдет опорттый видеосигнал, соответс.твующцй принимаемому коду ФМ ПСП. Все элементы каждого из мцогопаз;тц .оцных МЧС промаципулцрованы ,одной и тоц же ПСП. При этом и процессе ст.нхроцного перемножения входцого фдзомднипулцровдццого и опорного видео. тгцалов Чдзовдя манттпуляция снимается и ца выходе перемцожителя имеют ь, .то отрезки тдрмоцических колеблцттй с частотой, рдттной несущей частоте;трцнимаемого в длттьтй момент элемента МЧС. В этсм случае Фильтры 2 согласованы с радиоимпульсдмц, поступаюшцми нд цх входы, Еттк 1 м- жет быть также выполнен в вде коцвольвера. Прц этом частотатторцсго сцгцдлд, который поступает тл тсэро вход блока 1 с выходя блока 3, ыбцрается тлкттм обрядом, чтобы т злвцттртттымо мента МЧС тстотл кочеблнтьй цл из 20 25 35 40 50 55 тр кцвливера совллддла с централь - нй леттй соответствуоего фильтря 2, Тсэгттт фильтры выполцятотся так, то ы цх ттмттзцттудцо- тлстсгтндя характерис.тцкл была согласована с формойи тте.тт,тсс тт,то о оклика коцвольвера. Роттлоттш блок ч по цомеру одного из своих входов, цд который поступает максимальный сигнал, определяет номер принимаемого элемента МЧС и производит кодирование таким образом, тта номер принятого элемента МЧСпреобразуется в двоичный код, который ца выходах решающего блока 4 предста;ляется в параллельном коде. Последовлтельность таких двоичных кодовых томбтацит, сосэтветствующих номерам принимаемых элементов МЧС. отрдкает структуру принимаемого сигнала. По сигналам, поступающим нд тдктсцэые вхоты регистров 5, двоичный код, тображающии структуру МЧС, записывается ц продвигается по 1 раэрядоэ регистров 5. Для кода с основанием 2, как, например, в прототипе, или ялогичных дискретных согласоваттттт,тх Фильтрах, для запоминания структуры сигнала и последовательного обновления кода путем его сдвига цс.обходим один регистр 5. В предлагаемом устройстве аналогичные функтити тзыполцяют К = 1 оти регистровсдви,а 5, где п одновременно является числом частотных позиций сигнала ц основанием кода сигнала. Количество разрядов в каждом из регистров 5 одццаково и определяется числом зременцых позиций мцогочастотного мцогопозттционного сигнала. Совокупность двсичных символов, записанных в 1-ы разряде всех регистров 5, определяет омер конкретного частотного элемента МЧС, стоящего на однойцз временных позиций, Прц этом структура принятого МЧС оиределяется всейсовокупностью состояний разрядоввсех К регистров 5. Сравнение кодовыхкомбинаций, записанных в регистрах5 ирацящихся в блоке 6 памяти, осуществляется при помощи элементов 7 равнозначности. Каждый элемент 7 равнозндтности состоит из К элементарнь.х элементов равнозначности и схемь И Первые входы элементарных элементов рдтэнозттачности подключены к1-му разряду соответствукпцего регистра 5, вторые входы этих элементарных этететтов равнозначности соединеныс сооттт т з туютики выходами блока 6 памяти, Выходь тлемецтарцых элемецтов равнозначности подключены к входам зтемецта И, выход которого является выходом элемента / равцоттначцости. На выходе элементарного злемецта равнозначности имеет место "1"если на его оба входа поступаютодинаковые двоичные символы, Ееи жеца олин из входов поступает "1", ана другой "О", то на выходе элементарного элемента равно. цачцости имеет место "О". На выходе элемента И,т.е. на выходе элемента 7 равнозначности, находится только в томслучае, если происходит совпадениетзо всех элементарных элементах равнозначности, т.е.,если двоичные символы, записанные в )-м разряде всехрегистров 5 совпадут с соответствующими сцмволамц, хранящимися в блокеб памяти. Таким образом, каждый элемент 7 равнозначности позволяет определить соответствие номера принятого элемента МЧС номеру, хранящемуся в блоке 6 ц представленному в двоичном коде. Вся совокупность элементов 7 равнозначности позволяет определить стеттець соответствия структуры принятого сигнала одной из структур используемых мцогопозиттионньтх сигналов. В оттределеццьтт момент времени происходит совпадение кодов,записанных в регистрах 5 и на выхо -дах блока 6, В этом случае "1", отражающая согпадецие кодов, с выходовэлементов 7 равцозначцости поступаетна входы цифрового сумматора 8. Количество логических единиц, поступающих на вход цифрового сумматора 8,определяет число совпадений в элементах 7 равнозначности. Цифровойсигнал ца выходе цифрового сумматора8 отображает в двоичном коде числосовпадений между кодамц, считываемыми из блока 6 с кодом, находящимсяв данный момент времени в регистрах5. В начале дик."та обработки ячейки регистра 9 памяти находятся в нулевом состоянии, а запись информации в него происходит цо сигналу с выхода компаратора 10, который появляется только в случае, когда поступаюццй код с выхода ттцфрового сумма тора 8 отображает большее число, чем код, храцяптцйся т регистре 9 памяти, Этот же сигца. с выхтцта компаратора 10 15 20 25 30 35 40 45 50 55 1 О подается ца вход р тзрешсцця заццсц буферного регистра 11 для записи информационного кода. Счетчиком 12 формируются разряды информационного кода, которые являются также управляютики сигт тттамт блока 6, П)стте окончания 1,. Гтакт в, где . частота генератора 13, Г - количество временных позиций МЧС (колестцо разрядов регистров памяти), М - количество многопозиционных сигналов, в буферцом регистре 11 записывается кодовая комбинация из К = 1 од Мг двоичных информационных символов, соответствующая максимуму взаимной корреляционной функции принятого ДЧФГ 1 С и одного из опорных кодов. Эта кодовая комбинация считывается в регистре 14 сигналом, поступающим с делителя 15. который также устанавливает в нулевое состояние регистр 9, В течение следующего цикла работы угтроттства инфорттаттия с выхода регистра 14 поступает к потребителю. При обработке М сигналов счетчик 12 считает до М. К моменту сравнения всех М опорных сигналов с кодом, записанных в регистрах 5, происходит свертка принимаемого и опорного ФМ псевдослучайных сигналов в блоке 1 ц принимается решение решающим блоком 4. По сигналу, поступившему с детштфратора 16, который является так. же управляющим для регистров 5, записывается решение решающего блока 4 в первые разряды регистров 5. В регистрах 5 осуществляется постоянный сдвиг номера частотной позиции сигнала. Например, состояние регистров 5 можно определить как числовую последовательность: 6, 1, 12, 15, 3,Опорный код, считываемый из блока 6. отражает аналогичную числовую последовательность, При совпадении числовых последовательностей на входы сумматора 8 поступают с выходов элемецтов 7 равнозначности сигналы . В сумматоре 8 в совокупности с компаратором 10 ц регистром 9 производится оптттмальттое определение максимального результата сравнения принятого и опорных кодов. Предложенное устройство позволяет осуществить частичную когерентцую свертку ДЧФМС, так как элементы ФМ ПСП обрабатываются в блоке свертки когерентно, а частотно-временная матрица - некогерентцо в цифровой части устройства.Обычно ДЧФЯС формирует на передающей стороне от одного опорного генератора. Поэтому и на приемной стороне генератор 13 тактовых импульсов работает синхронно с блоком 3 опорного сигнала.Решающий блок может быть выполнен по схеме, представленной на фиг. 2. Усилители 17 выполняют функцию детектирования и объединения двух сигналов и могут быть выполнены на микросхемах 140 УД 7 или заменены двумя диодами, катоды которых объединены и подключены к входам компаратора. Ком параторы 18 могут выполняться на микросхемах типа 521 СА 1, на выходе которых при величине сигнала на входе А большем, чем на входе В, имеет место " 1". Согласно представленной схеме, если уровень сигнала на первом входе больше, чем на остальных входах, на выходе решающего блока имеем код 00, соответствующий номеру частотной позиции сигнала. Схему решаю щего блока можно развивать и на большее число частотных каналов, чем 4. Формула изобретения30Устройство для приема многопозиционных дискретных частотно-фазоманипулированных сигналов, содержащее регистр сдвига, выходы которого соединены с первыми входами элементов35 равнозначности, выходы которого соединены с соответствующими входами сумматора, выходы которого соединены с одной группой входов компаратора и регистра памяти, выходы которого соединены с другой группой входов компаратора, выход которого соединен с управляющими входами регистра памяти и буферного регистра, выходы которого соединены с входами регистра информации, соответствующие входы которого соединены с выходом делителя и первым выходом генератора тактовых импульсов, второй выход которого соединен с входом счетчика, выход делителя соединен с соответствующимвходом регистра памяти, о т л и ч а ю щ е е с я тем, что, с целью повышения помехоустойчивости за счет увеличения ансамбля многопозиционных сигналов, введены блок свертки, блок опорных сигналов, и фильтров, решающий блок, Крегистров сдвига (К1 о,п), де(пифратор и блок памяти, причем первый вход блока свертки является входом устройства, а выход через соответствующие фильтры соединен с входами решающего блока, выходы которого соединены с первыми входами всех регистров сдвига, вторые входы которых, управляющий вход решающего блока и вход делителя соединены с выходом дешифратора, входы которого, входы блока памяти и буферного регистра соединены с выходами счетчика, выходы блока памяти соединены с вторыми входами элементов равнозначности, выходы Крегистров соединены с первыми входами элементов равнозначности, первый и второй выходы блока опорных сигналов соединены соответственно с вторым входом блока свертки и входом генератора тактовых импульсов..Ла Подписноеобретениям и открытиям приРаушская наб., д, 4/5 роиэводственно-издательский комбинат "Патент", г. Ужгород, ул, Гагарина, 101 Заказ 4893/57 Тираж 626 ВНИИПИ Государственного комитета по 113035, Москва, Ж

СмотретьЗаявка

4266120, 23.06.1987

КИЕВСКОЕ ВЫСШЕЕ ВОЕННОЕ ИНЖЕНЕРНОЕ ДВАЖДЫ КРАСНОЗНАМЕННОЕ УЧИЛИЩЕ СВЯЗИ ИМ. М. И. КАЛИНИНА

БАРЛАБАНОВ ВАЛЕРИЙ ВЛАДИМИРОВИЧ, ЛИТВИНЕНКО ВЛАДИМИР ВЛАДИМИРОВИЧ, ПОСОХОВ ВИКТОР ПАВЛОВИЧ

МПК / Метки

МПК: H04L 27/28

Метки: дискретных, многопозиционных, приема, сигналов, фазоманипулированных, частотно

Опубликовано: 15.08.1989

Код ссылки

<a href="https://patents.su/5-1501301-ustrojjstvo-dlya-priema-mnogopozicionnykh-diskretnykh-chastotno-fazomanipulirovannykh-signalov.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для приема многопозиционных дискретных частотно фазоманипулированных сигналов</a>

Предыдущий патент: Устройство для приема частотно-манипулированных сигналов

Следующий патент: Устройство для цифроаналогового преобразования

Случайный патент: 195404