Микропрограммный процессор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

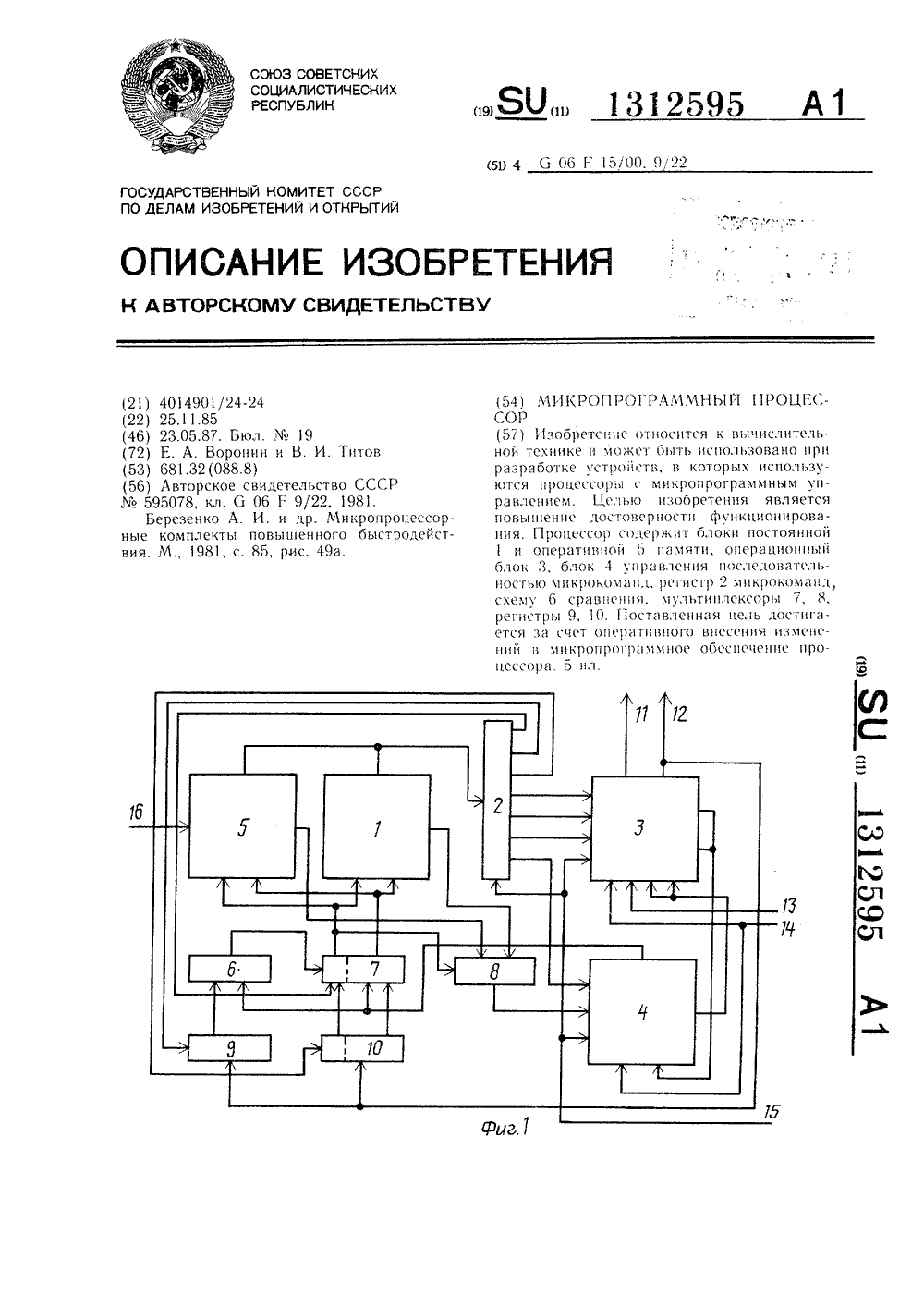

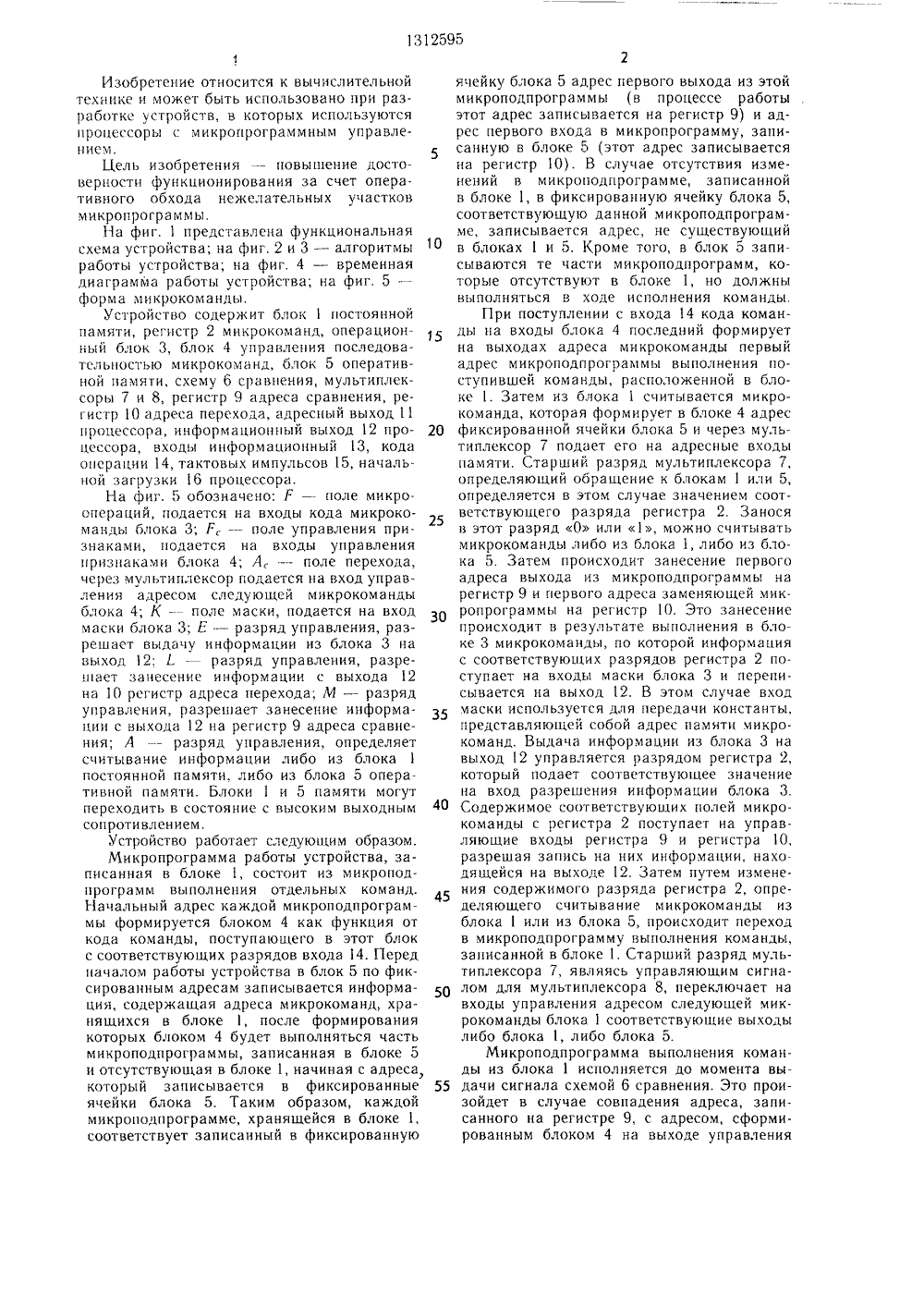

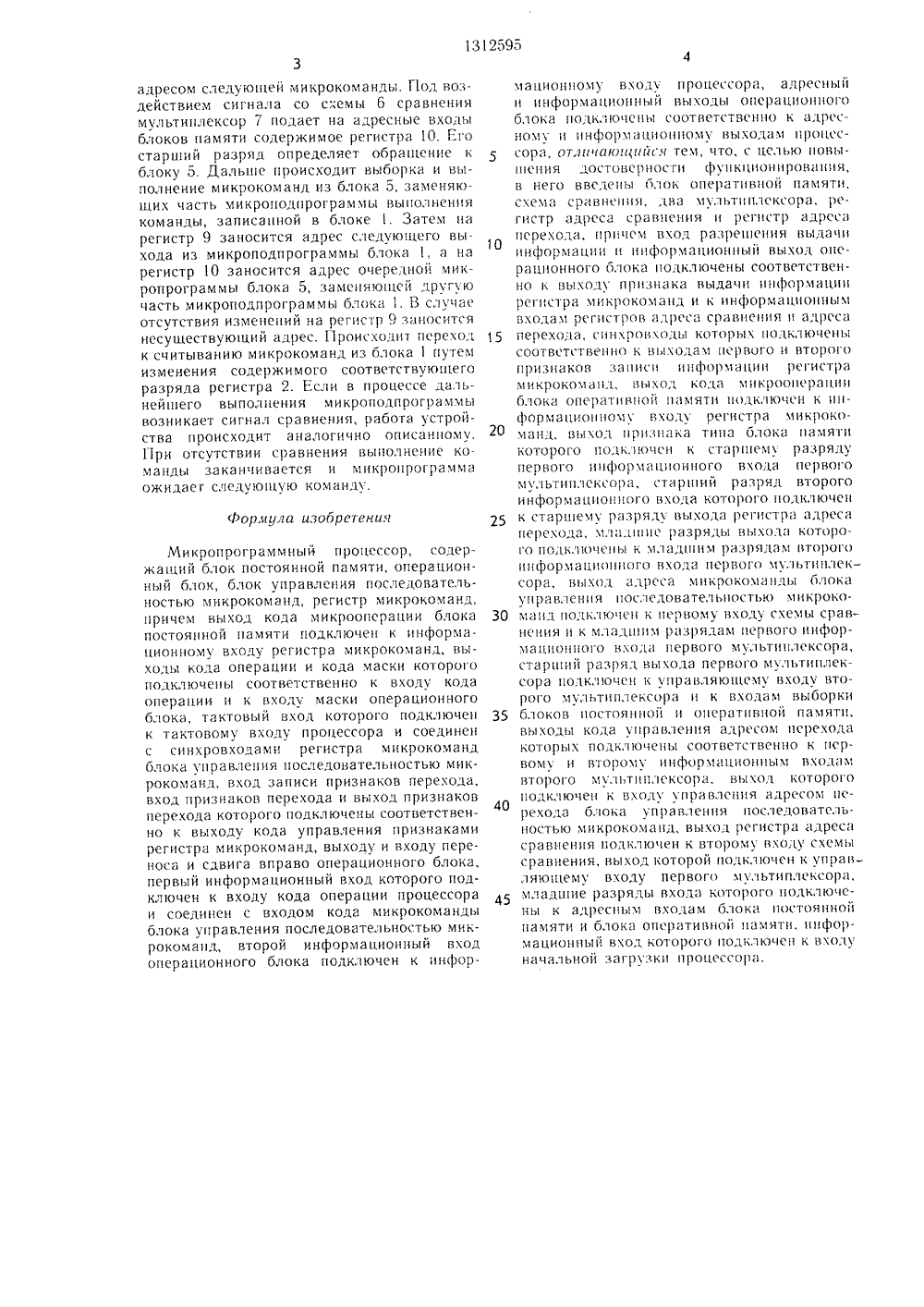

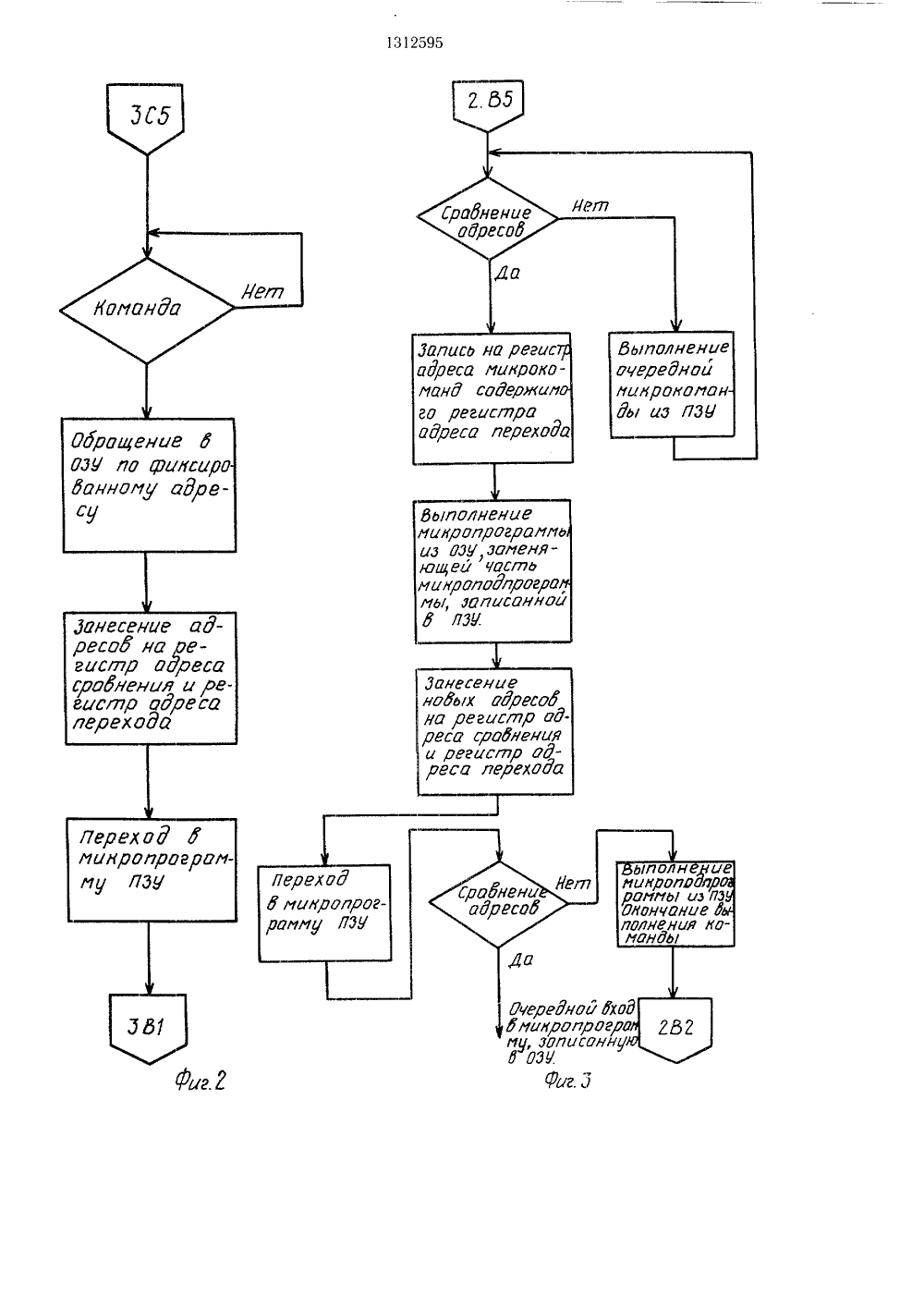

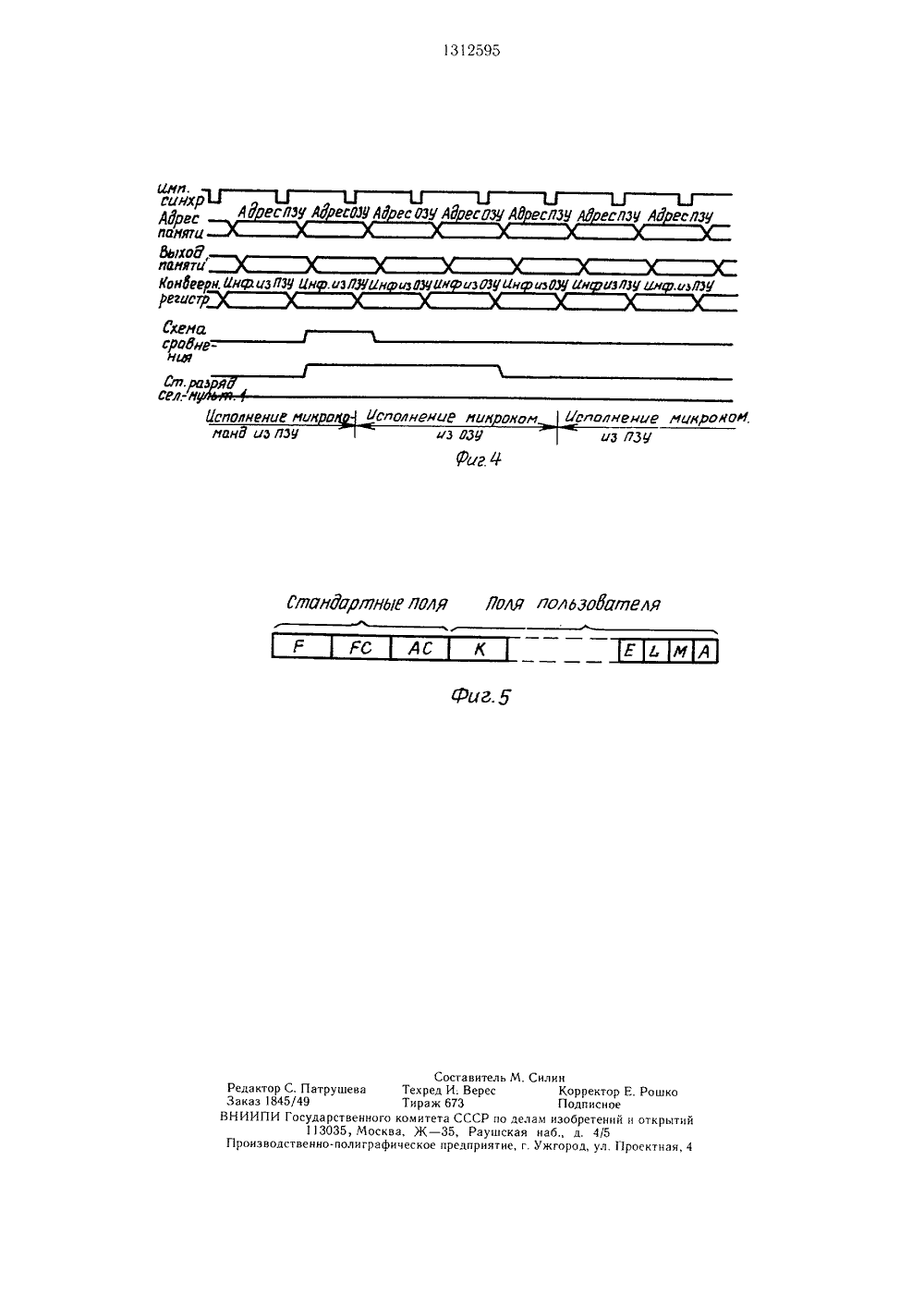

(5 У ЕТЕНИЯ 9В. И. Тит СССР81.роироцесбыстроде тельство9/22, 19лр. Мигненногонс. 49 а. р -тОСУДАРСТВЕНКЫИ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕКИЙ И ОТКРЫТИЙ ПИСАНИЕ ИЗ Н АВТОРСКОМУ СВИДЕТЕПЬСТ(57) 1 зобретение относится к вычислительной тенике и мокст быть использовано приразработке устройств, в которы используются процессоры с микропрограммным управлением. Целью изобретения являетсяиовыгиение достоверности функционирования. Процессор соцерькит олоки постоянной1 и оперативной 5 памяти, операционныйблок 3, блок 4 управления послецовдтельносью микрокомаиц, регист 11 2 микрокоманц,схему 6 сравнения. мультиплексоры 7, 8,регистры 9, 1 О. Поставленная цель достигается зд счет оперативного внесения изменений в микроцрогрдммное обеспечение процессора. 5 ил,Изобретение относится к вычислительнойтехнике и может быть использовано при разработке устройств, в которых используютсяпроцессоры с микропрограммным управлением,Цель изобретения - повышение достоверности функционирования за счет оперативного обхода нежелательных участковмикропрограммы.На фиг. 1 представлена функциональнаясхема устройства; на фиг. 2 и 3 - алгоритмыработы устройства; на фиг. 4 - временнаядиаграмма работы устройства; на фиг. 5 -форма микрокоманды.Устройство содержит блок 1 постояннойпамяти, регистр 2 микрокоманд, операционный блок 3, блок 4 управления последовательностью микрокоманд, блок 5 оперативной памяти, схему 6 сравнения, мультиплексоры 7 и 8, регистр 9 адреса сравнения, регистр 1 О адреса перехода, адресный выход 11процессора, информационный выход 12 процессора, входы информационный 13, кодаоперации 14, тактовых импульсов 15, начальной загрузки6 процессора.На фиг. 5 обозначено: Е - поле микроопераций, подается на входы кода микрокоманды блока 3; Р,поле управления признаками, подается на входы управленияпризнаками блока 4; А,поле перехода,через мультиплексор подается на вход управления адресом следующей микрокомандыблока 4; К - поле маски, подается на входмаски блока 3; Е -- разряд управления, разрешает выдачу информации из блока 3 навыход 12; Е - разряд управления, разрешает занесение информации с выхода 12на 10 регистр адреса перехода; М - разрядуправления, разрешает занесение информации с выхода 12 на регистр 9 адреса сравнения; А - разряд управления, определяетсчитывание информации либо из блока 1постоянной памяти, либо из блока 5 оперативной памяти. Блоки 1 и 5 памяти могутпереходить в состояние с высоким выходнымсопротивлением.Устройство работает следующим образом.Микропрограмма работы устройства, записанная в блоке 1, состоит из микрогндпрограмм выполнения отдельных команд.Начальный адрес каждой микроподпрограммы формируется блоком 4 как функция откода команды, поступающего в этот блокс соответствующих разрядов входа 14. Передначалом работы устройства в блок 5 по фиксированным адресам записывается информация, содержащая адреса микрокоманд, хранящихся в блоке 1, после формированиякоторых блоком 4 будет выполняться частьмикроподпрограммы, записанная в блоке 5и отсутствующая в блоке 1, начиная с адреса,который записывается в фиксированныеячейки блока 5. Таким образом, каждоймикроподпрограмме, хранящейся в блоке 1,соответствует записанный в фиксированную 5 1 О 15 20 25 30 35 40 45 50 55 ячейку блока 5 адрес первого выхода из этой микроподпрограм мы (в процессе работы этот адрес записывается на регистр 9) и адрес первого входа в микропрограмму, записанную в блоке 5 (этот адрес записывается на регистр 10). В случае отсутствия изменений в микроподпрограмме, записанной в блоке 1, в фиксированную ячейку блока 5, соответствующую данной микроподпрограмме, записывается адрес, не существующий в блоках 1 и 5. Кроме того, в блок 5 записываются те части микроподпрограмм, которые отсутствуют в блоке 1, но должны выполняться в ходе исполнения команды.Г 1 ри поступлении с входа 14 кода команды на входы блока 4 последний формирует на выходах адреса микрокоманды первый адрес микроподпрограммы выполнения поступившей команды, расположенной в блоке 1. Затем из блокасчитывается микро- команда, которая формирует в блоке 4 адрес фиксированной ячейки блока 5 и через мультиплексор 7 подает его на адресные входы памяти. Старший разряд мультиплексора 7, определяющий обращение к блокам 1 или 5, определяется в этом случае значением соответствующего разряда регистра 2. Занося в этот разряд 0 или 1, можно считывать микрокоманды либо из блока 1, либо из блока 5. Затем происходит занесение первого адреса выхода из микроподпрограммы на регистр 9 и первого адреса заменяющей микропрограммы на регистр 10. Это занесение происходит в результате выполнения в блоке 3 микрокоманды, по которой информация с соответствующих разрядов регистра 2 поступает на входы маски блока 3 и переписывается на выход 12. В этом случае вход маски используется для передачи константы, представляющей собой адрес памяти микро- команд. Выдача информации из блока 3 на выход 12 управляется разрядом регистра 2, который подает соответствующее значение на вход разрешения информации блока 3. Содержимое соответствующих полей микро- команды с регистра 2 поступает на управляющие входы регистра 9 и регистра 10, разрешая запись на них информации, находящейся на выходе 12. Затем путем изменения содержимого разряда регистра 2, определяющего считывание микрокоманды из блока 1 или из блока 5, происходит переход в микроподпрограмму выполнения команды, записанной в блоке 1. Старший разряд мультиплексора 7, являясь управляющим сигналом для мультиплексора 8, переключает на входы управления адресом следующей микрокоманды блока 1 соответствующие выходы либо блока 1, либо блока 5.Микроподпрограмма выполнения команды из блока 1 исполняется до момента выдачи сигнала схемой 6 сравнения. Это произойдет в случае совпадения адреса, записанного на регистре 9, с адресом, сформированным блоком 4 на выходе управленияФормула изобретения адресом следуюцей микрокоманды. Г 1 од воздействием сигнала со схемы 6 сравнения мультиплексор 7 подает ца адресные входы блоков памяти содержимое регистра 10. Его старший разряд определяет обращение к блоку 5. Дальше происходит выоорка и выполнение микрокоманд из блока 5, заменяк)- щих часть микроподпрограммы выполнения команды, записанной в блоке . Затем ца регистр 9 заносится адрес следующего выхода из микроподпрограммы блока 1, а на регистр О заносится адрес очередной микропрограммы блока 5, заменяюцей другую часть микроподпрограммы блока 1. В случае отсутствия изменений на регистр 9 ззюсится несуществующий адрес. Гроисходит перехол к считыванию микрокоманл из блока 1 путем изменения содержимого соответствующего разряда регистра 2. Если в процессе дальнейшего выполнения микроподпрограммы возникает сигнал сравнения, работа устройства происходит аналогично описанюму. При отсутствии сравнения выполнение ко. мацды заканчивается и микропрограмма ожидает следующую команду. Микропрограммный процессор, содержаций блок постоянной памяти, операционный блок, блок управления последовательностьо микрокоманд, регистр микрокоманд, причем выход кода микрооперации блока постоянной памяти подключен к информационному входу регистра микрокоманл, выходы кола операции и кода маски которого подключены соответственно к входу кода операции и к входу маски операционного блока, тактовый вход которого подключен к тактовому входу процессора и соединен с синхровходами регистра микрокоманд блока управления последовательностью микрокоманд, вход записи признаков перехода, вход признаков перехода и выход признаков перехода которого подключены соответственно к выходу кода управления признаками регистра микрокоманд, выходу и входу переноса и сдвига вправо операционного блока, первый информационный вход которого подключен к входу кода операции процессора и соединен с входом кода микрокоманлы блока управления последовательностью микрокоманд, второй информационный вход операционного блока подключен к инфор 5 1 О 15 20 25 30 35 40 45 мационному вхолу процессора, адресный и информационный выходы онерациоццого блока полключецы соответственно к злреснох)у и информационному выходам процессора, от,)иипюии 1 с) тем, что, с цельк) цовыцц.ния лостовсрцоси фуцкционировзни 5), в него введены блок оперативной памяти, схема сравнен и 5), лва мультцп,)сксор), регистр адреса сравнения и регистр адреса перехола, причем вход разрешения выдачи информации ц информационный выход операционного блока подключены соответственно к выходу признака выдачи информации регистра микрокомзнл и к информационным входам регистров а;ц)есз сравнения ц алроса перехода, сицхровходы которых полклн)чены соответственно к выходам первого и второго признаков записи информации регистра микрокомзил, ыхол кола микрооперации блока оперативной памяти подключен к ицформзциоцномх вхолх регистра микрокомацл, выхол призгака типа блока памяти которого полклктчсц к старшему разряду первого ицформационцого входа первого мультиплексора, стариии разряд второго информационного входа которого полключец к старшему рззрялу выхола регистра адреса перехода, млзлшие разрялы выхолз которого по;1 клкхчсц ы к младц им разрядам второго информационного вхола первого мультицлексора, вхол алресз мцкрокомацлы блока управления цослеловательцостьк) микрокомзцл по;1 ключсн к первому входу схемы сравнения и к хл)лц)и рззрялам первого информационного вхс)лз первого мультиплексора, старший разряд выхода первого мультиплексора полкцо )ен к управляющему входу второго мультиплексора и к входам выборки блоков постоянной и оперативной памяти, выходы кода управления адресом перехода которых подключены соответственно к первому и второму информационным входам второго мул)типлсксора, вы;ол которого подключен к вхс)лу управления адресом перехода блока управления последователь. ностыо микрокомац;1, выхс)д регистра адреса сравнения подключен к второму входу семы сравнения, выход которои подкл)очен к управляющему входу первого мультиплексора, младшие разряды входа которого подключены к алресшм вхо;1 ам блока цостоянцой памяти и блока оперативной памяти, информационный вход которого подключен к вхолу начальной загрузки процессора.ИИЕЗП 1312595 дя е И есПЗУ Ао есОЩА 3 есОЗУАЫ есОЗУА 0 есПЗУ Ао есПЗУ Ао есПЗУсйнх,о паня 7 и дыхоУ ианяти" конбеерн иноаизпзу ин .иъпзуин изюзуин и 303 ин изОяин иьпзуин .иьпзу регистр бо.раз юСЕяи Исаоянение лю о исполненцЕ лин окои Исполнение чцнронои,ланд из ПЗу иЗ ОЗУ Риг 4 из ПЗу СхеиаСРОВнЕнщ ЬлаН 1 аРЩНЫ ПОПО ПОЛЯ ПОИЬЗО 1 а 77 ЕЬЯ Составитель М. СилинРедактор С. Патрушева Техред И. Верес Корректор Е. РошкоЗаказ 1845/49 Тираж 673 ПодписноеВНИИПИ Государственного комитета СССР по делам изобретений и открытий113035, Москва, Ж - 35, Раушская наб., д. 4/5Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

СмотретьЗаявка

4014901, 25.11.1985

ПРЕДПРИЯТИЕ ПЯ Р-6380

ВОРОНИН ЕВГЕНИЙ АЛЕКСЕЕВИЧ, ТИТОВ ВЯЧЕСЛАВ ИВАНОВИЧ

МПК / Метки

МПК: G06F 15/00, G06F 9/22

Метки: микропрограммный, процессор

Опубликовано: 23.05.1987

Код ссылки

<a href="https://patents.su/5-1312595-mikroprogrammnyjj-processor.html" target="_blank" rel="follow" title="База патентов СССР">Микропрограммный процессор</a>

Предыдущий патент: Устройство для моделирования систем массового обслуживания

Следующий патент: Адаптивная система обработки данных

Случайный патент: Способ ультрозвуковой сварки полимерных пленок