Устройство для формирования прерывания при отладке программ

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1305680

Авторы: Гаврилов, Колесников, Федосов

Текст

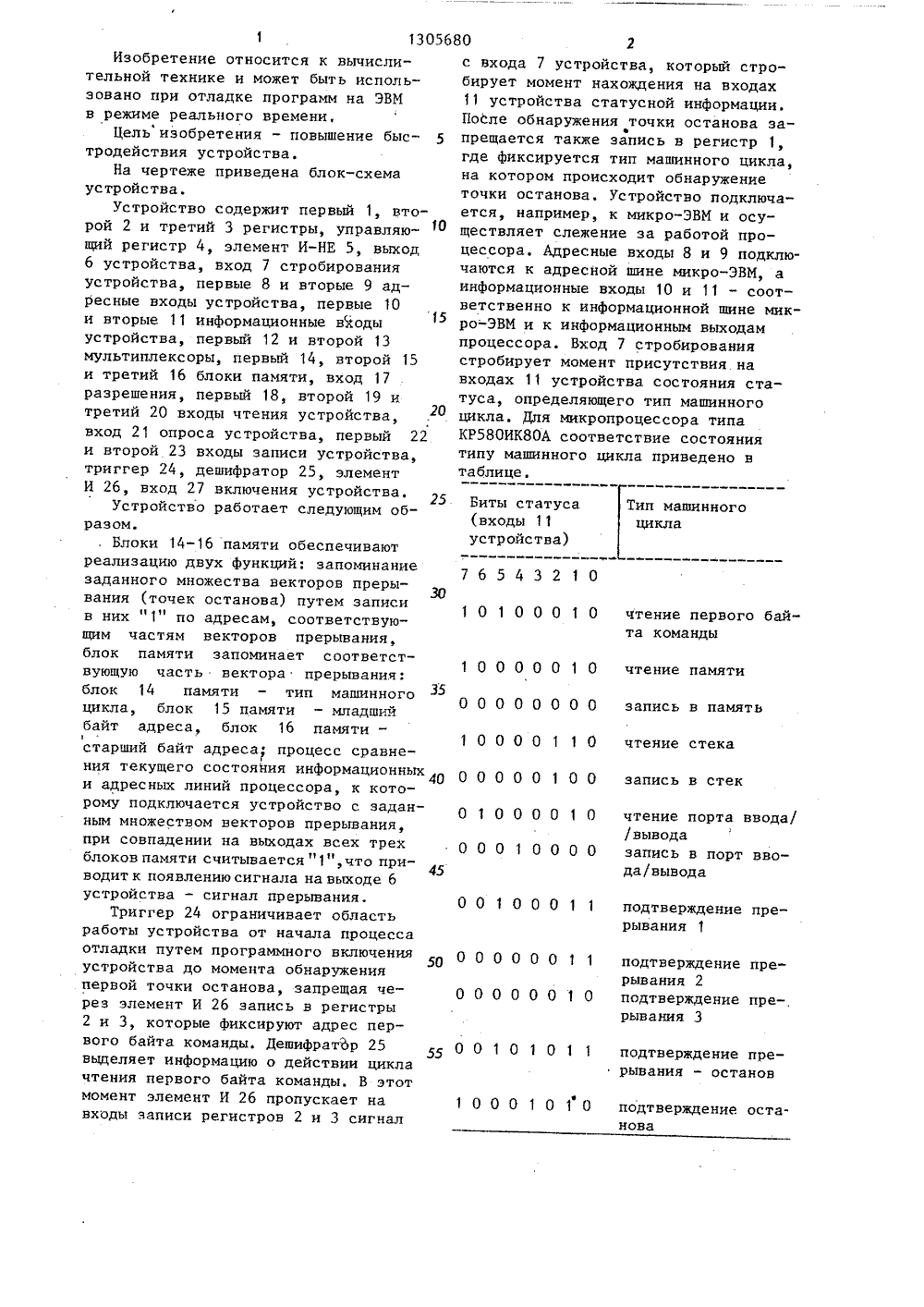

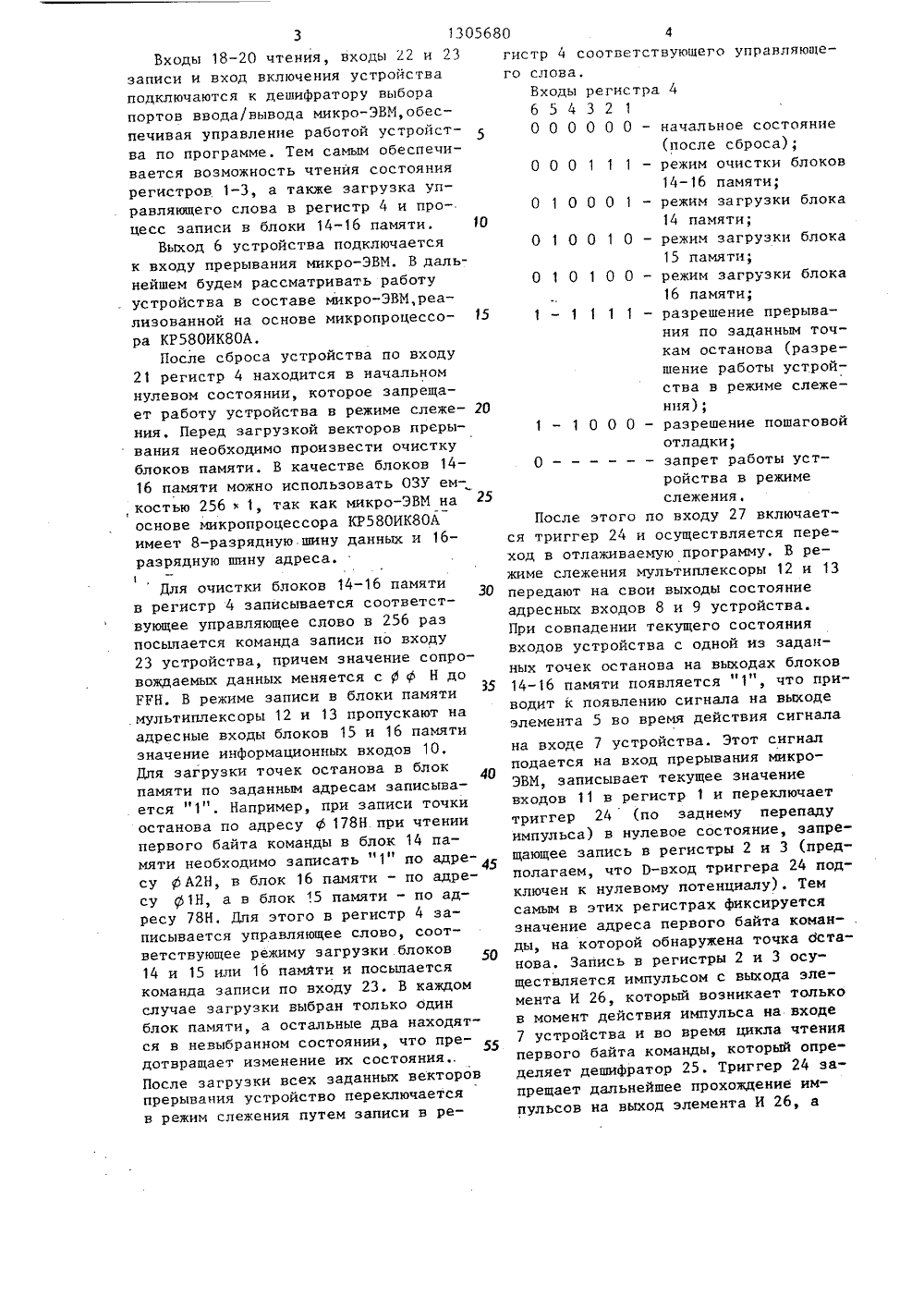

130568Изобретение относится к вычиспительной технике и может быть использовано при отладке программ на ЭВМв режиме реального времени.Цель изобретения - повышение быстродействия устройства.На чертеже приведена блок-схемаустройства,Устройство содержит первый 1, второй 2 и третий 3 регистры, управляющий регистр 4, элемент И-НЕ 5, выход6 устройства, вход 7 стробированияустройства, первые 8 и вторые 9 адресные входы устройства, первые 10и вторые 1 1 информационные входыустройства, первый 12 и второй 13мультиплексоры, первый 14, второй 15и третий 16 блоки памяти, вход 17разрешения, первый 18, второй 19 итретий 20 входы чтения устройства,вход 21 опроса устройства, первый 22и второй 23 входы записи устройства,триггер 24, дешифратор 25, элементИ 26, вход 27 включения устройства.Устройство работает следующим образом.Блоки 14-16 памяти обеспечиваютреализацию двух функций; запоминаниезаданного множества векторов прерывания (точек останова) путем записив них " 1" по адресам, соответствующим частям векторов прерывания,блок памяти запоминает соответствующую часть вектора прерывания:блок 14 памяти - тип машинногоцикла, блок 15 памяти - младшийбайт адреса, блок 16 памяти -1старший байт адреса процесс сравнения текущего сОстОяния информационных 40и адресных линий процессора, к которому подключается устройство с заданным множеством векторов прерывания,при совпадении на выходах всех трехблоковпамяти считывается "1",что приводит к появлению сигнала на выходе 6устройства - сигнал прерывания,Триггер 24 ограничивает областьработы устройства от начала процессаотладки путем программного включенияустройства до момента обнаруженияпервой точки останова, запрещая через элемент И 26 запись в регистры2 и 3, которые фиксируют адрес первого байта команды. ДешифратЬр 25выделяет информацию о действии циклачтения первого байта команды, В этотмомент элемент И 26 пропускает навходы записи регистров 2 и 3 сигналТип машинного цикла Биты статуса(входы 11устройства) 7654321010100010 чтение первого байта команды 1 0 0 0 0 0 1 0 чтение памяти 00000000 запись в память 1 0 0 0 О 1 1 О чтение стека0 0 0 0 0 1 0 0 запись в стек чтение порта ввода//вывода запись в порт ввода/вывода 01000010 00010000 00100011 подтверждение прерывания 1 подтверждение прерывания 2подтверждение прерывания 3 О О О О О О 1 1 00000010 00101011 подтверждение прерывания - останов 1 0 0 0 1 0 1 0 подтверждение останова о гс входа 7 устройства, который стробирует момент нахождения на входах11 устройства статусной информации.После обнаружения точки останова запрещается также запись в регистр 1,где фиксируется тип машинного цикла,на котором происходит обнаружениеточки останова. Устройство подключается, например, к микро-ЭВМ и осуществляет слежение за работой процессора. Адресные входы 8 и 9 подключаются к адресной шине микро-ЭВМ, аинформационные входы 10 и 1 1 - соответственно к информационной шине микро- ЭВМ и к информационным выходампроцессора. Вход 7 стробированиястробирует момент присутствия навходах 11 устройства состояния статуса, определяющего тип машинногоцикла. Для микропроцессора типаКР 580 ИК 80 А соответствие состояниятипу машинного цикла приведено втаблице.на входе 7 устройства. Этот сигналподается на вход прерывания микроЭВМ, записывает текущее значениевходов 11 в регистр 1 и переключаеттриггер 24 (по заднему перепадуимпульса) в нулевое состояние, запрещающее запись в регистры 2 и 3 (предполагаем, что П-вход триггера 24 подключен к нулевому потенциалу), Темсамым в этих регистрах фиксируетсязначение адреса первого байта коман- .ды, на которой обнаружена точка бстанова, Запись в регистры 2 и 3 осуществляется импульсом с выхода элемента И 26, который возникает тольков момент действия импульса на входе7 устройства и во время цикла чтенияпервого байта команды, который определяет дешифратор 25. Триггер 24 запрещает дальнейшее прохождение импульсов на выход элемента И 26, а 3 13056Входы 18-20 чтения, входы 22 и 23записи и вход включения устройстваподключаются к дешифратору выборапортов ввода/вывода микро-ЭВМ,обеспечивая управление работой устройства по программе. Тем самым обеспечивается возможность чтения состояниярегистров 1-3, а также загрузка управляющего слова в регистр 4 и процесс записи в блоки 14-16 памяти. ЮВыход 6 устройства подключаетсяк входу прерывания микро-ЭВМ. В дальнейшем будем рассматривать работуустройства в составе микро-ЭВМ,реализованной на основе микропроцессора КР 580 ИК 80 А,После сброса устройства по входу21 регистр 4 находится в начальномнулевом состоянии, которое запрещает работу устройства в режиме слежения. Перед загрузкой векторов прерывания необходимо произвести очисткублоков памяти. В качестве блоков 1416 памяти можно использовать ОЗУ емкостью 256 х 1, так как микро-ЭВМ наоснове микропроцессора КР 580 ИК 80 Аимеет 8-разрядную шину данных и 16 разрядную шину адреса.Для очистки блоков 14-16 памяти в регистр 4 записывается соответствующее управляющее слово в 256 раз посылается команда записи по входу 23 устройства, причем значение сопровождаемых данных меняется сф Н до РРН. В режиме записи в блоки памяти35 мультиплексоры 12 и 13 пропускают на адресные входы блоков 15 и 16 памяти значение информационных входов 10. Для загрузки точек останова в блок 40 памяти по заданным адресам записывается "1", Например, при записи точки останова по адресу Ф 178 Н при чтении первого байта команды в блок 14 памяти необходимо записать 1 по адре су ф А 2 Н, в блок 16 памяти - по адресу ф 1 Н, а в блок 5 памяти - по адресу 78 Н. Для этого в регистр 4 записывается управляющее слово, соответствующее режиму загрузки. блоков 14 и 15 или 16 памяти и посылается команда записи по входу 23. В каждом случае загрузки выбран только один блок памяти, а остальные два находятся в невыбранном состоянии, что предотвращает изменение их состояния После загрузки всех заданных векторов прерывания устройство переключается в режим слежения путем записи в ре 80 4гистр 4 соответствующего управляющего слова,Входы регистра 46 5 4 3 2 10 0 0 О 0 0 - начальное состояние(после сброса);0 0 0 1 1 1 - режим очистки блоков14 - 16 памяти;0 1 0 0 0 1 - режим загрузки блока14 памяти;0 1 0 0 1 0 - режим загрузки блока15 памяти;0 1 0 1 0 0 - режим загрузки блока16 памяти;1 - 1 1 1 1 - разрешение прерывания по заданным точкам останова (разрешение работы устройства в режиме слежения);1 - 1 О 0 0 - разрешение пошаговойотладки0 ------ запрет работы устройства в режимеслеженияПосле этого по входу 27 включается триггер 24 и осуществляется переход в отлаживаемую программу. В режиме слежения мультиплексоры 12 и 13 передают на свои выходы состояние адресных входов 8 и 9 устройства. При совпадении текущего состояния входов устройства с одной из заданных точек останова на выходах блоков 14-16 памяти появляется "1", что приводит к появлению сигнала на выходе элемента 5 во время действия сигнала5680 6 второго и третьего регистров, группы информационных выходов первого,130 110 входов статусных данных устройства 40 45 50 тем самым и на входы записи регистров 2 и 3. В регистре 1 фиксируется тип машинного цикла, на котором обнаружена точка останова,Прочитав значение адреса первого байта команды из регистров 2 и 3 можно программно проанализировать наличие установленных на данную команду точек останова и выдать на дисплей соответСтвующее сообщение, При этом ни одна" точка останова не будет потеряна. После этого по входу 27 триггер 24 включается в состояние, разрешающее дальнейшую работу устройства до обнаружения следующих точек оста- нова. Возможные паразитные точки останова исключаются путем программного анализа после прерывания и чтения первого байта команды. Чтением состояния регистра 1 можно сократить время программного анализа. Если из регистра 1 читается состояние, соответствующее всем типам машинного цикла, кроме чтения инструкции, то это свидетельствует об отсутствии других точек останова на данной команде,"сли в регистр 4 записать управляющее слово, соответствующее режиму пошаговой отладки (трассировка по каждой команде), тб прерывание происходит после каждой команды, В этом режиме все блоки памяти находятся в невыбранном состоянии, котороеприводит к постоянному присутствию "1" на их выходах. Можно также в невыбранное состояние перевести только второй и третий блок памяти, записав в первый блок памяти "1" по адресу, соответствующему коду какого-либо типа адресации, тем самым, обеспечивается трассировка программы по заданному типу адресации. Формула изобретения Устройство для формирования прерывания при отладке программ, содержащее регистр управляющего слова,первый, второй и третий регистр, первый и второй мультиплексор, первый, второй и третий блоки памяти, элемент И-НЕ, выход элемента И-НЕ соединен с выходом прерывания устройства и с входом записи первого регистра, вход чтения которого соединен с первым входом чтения устройства, второй и третий входы чтения устройства соединены соответственно с входом чтения 15 20 25 ЭО 35 второго и третьего регистров, группа информационных входов регистра управляющего слова и первые группы информационных входов первого и второго мультиплексоров соединены с группой входовых программных данных устройства группа соединена с группой информационныхвходов первого регистра и группойадресных входов первого блока памяти,вторые группы информационных входовпервого и второго мультиплексоровсоединены с группой адресных входовустройства, группа выходов первогомультиплексора соединена с группойинформационных входов второго регистра и группой адресных входов второгоблока памяти, группа выходов второгомультиплексора соединена с группойинформационных входов третьего регистра и группой адресных входов третьего блока памяти, выходы первого,второго и третьего блоков памяти соединены соответственно с первым, вторым и третьим входами элемента И-НЕ,четвертый, пягый и шестой входы которого соединены соответственно с выходом разрешения прерывания регистрауправляющего слова, входом стробирования и входом разрешения устройства,входы записи первого, второго и третьего блоков памяти соединены с входом записи устройства, второй вход записи которого соединен с входомзаписи регистра управляющего слова,вход сброса которого соединен с входом сброса устройства, управляющиевходы первого и второго мультиплексоров соединены с выходом управляющей работой мультиплексора регистрауправляющего слова, о т л и ч а ю -щ е е с я тем, что, с целью повышения быстродействия устройства, в него введены дешифратор, элемент И итриггер, причем группа информационных входов дешифратора соединена сгруппой входов статусных данных устройства, выход дешифратора соединенс первым входом элемента И, второй,третий и четвертый входы которого соединены соответственно с выходомразрешения прерывания регистра управляющего слова, входом стробирования устройства и выходом триггера,тактовый вход которого соединен с1305 б 80 Составитель Г.ПономареваРедактор Г.Гербер Техред Д.Олейник , Корректор А.Зимокосов Заказ 1452/4 б Тираж 673 ПодписноеВНИИПИ Государственного комитета СССРпо делам изобретений и открытий113035, Москва, Ж, Раущская наб., д.4/5 Производственно-полиграфическое предпринтие, г.ужгород, ул.Проектная,4 выходом элемента И-НЕ, вход сбросатриггера соединен с входом сбросаустройства, вход установки триггерасоединен с входом включения устройства, выход триггера соединен с седьмым входом элемента И-НЕ, выход элемента И соединен с входами записивторого и третьего регистров, первый,второй и третий выходы загрузки регистра управляющего слова соединенысоответственно с входами выбора первого, второго и третьего блоков памяти, а выход записи точки остановарегистра управляющего слова соединенс информационными входами первого,второго и третьего блоков памяти.

СмотретьЗаявка

3910442, 13.06.1985

РИЖСКОЕ ПРОИЗВОДСТВЕННОЕ ОБЪЕДИНЕНИЕ ВЭФ ИМ. В. И. ЛЕНИНА

ГАВРИЛОВ АЛЕКСЕЙ АЛЕКСЕЕВИЧ, КОЛЕСНИКОВ АНДРЕЙ НИКОЛАЕВИЧ, ФЕДОСОВ ВИКТОР ПЕТРОВИЧ

МПК / Метки

МПК: G06F 9/48

Метки: отладке, прерывания, программ, формирования

Опубликовано: 23.04.1987

Код ссылки

<a href="https://patents.su/5-1305680-ustrojjstvo-dlya-formirovaniya-preryvaniya-pri-otladke-programm.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для формирования прерывания при отладке программ</a>

Предыдущий патент: Микропрограммное устройство управления с контролем

Следующий патент: Микропрограммное устройство управления

Случайный патент: Сифонный водовыпуск