Устройство для отображения хода программ микро-эвм

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1203530

Автор: Николайчук

Текст

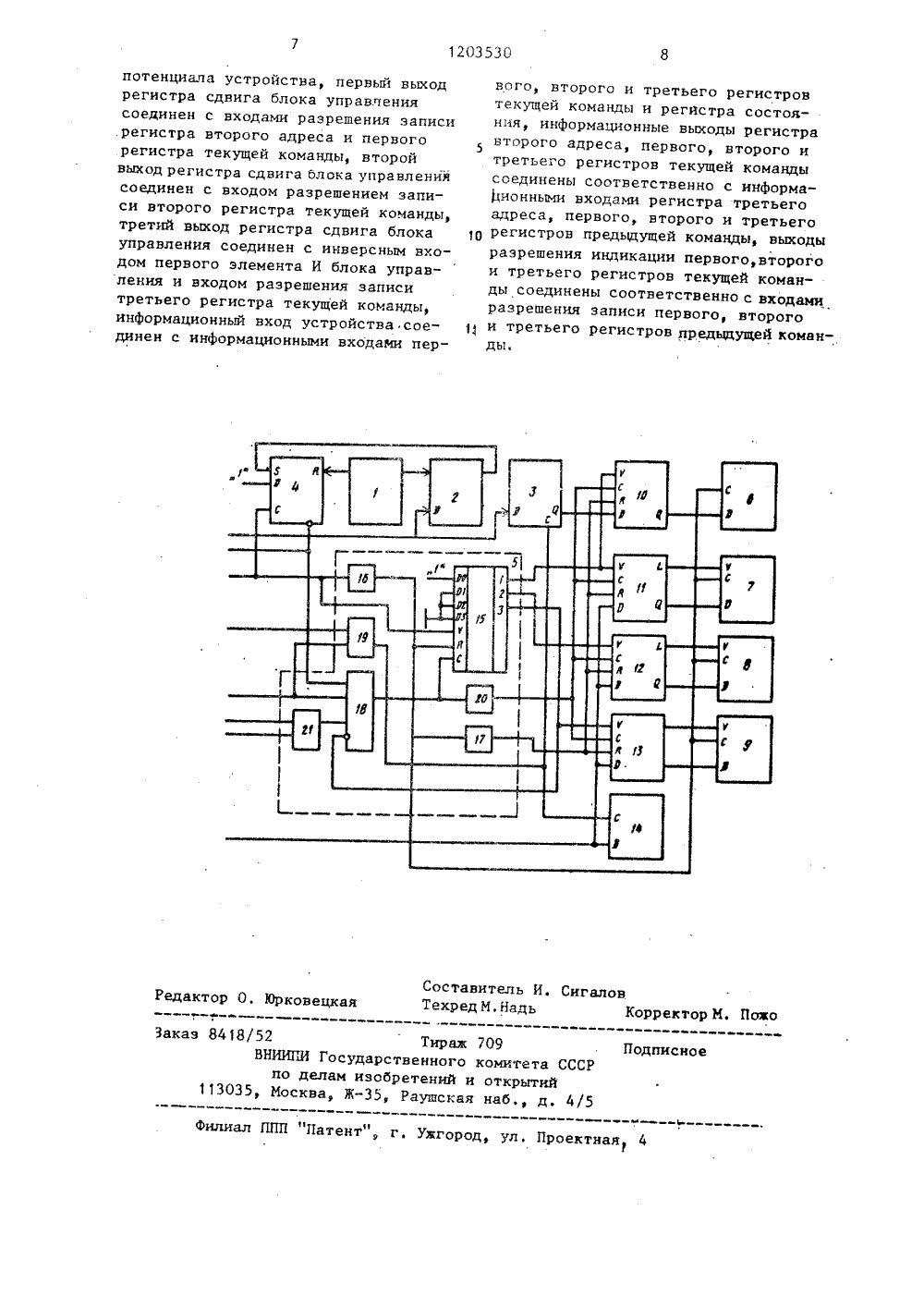

СОЮЗ СОВЕТСНИХСОЦИАЛИСТИЧЕСНИХРЕСПУБЛИК 8012035 50 4 С,06 Р 11/28 ОПИСАНИЕ ИЗОБРЕТЕНК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ СССР1979ССР 974. НИЯ вычи ачен ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЫТИЙ(54) УСТРОЙСТВО ДЛЯ ОТОБРАЖЕ(57) Изобретение относитсялительной технике и предназ,для отладки программ и аппаратурной части микро-ЭВМ. Целью изобретения является расширение функциональных возможностей за счет обеспечения одновременного отобракения предыдущегоФ текущего и очередного. адресов и команды. В устройство, содержащее блок задания режима, блок сравнения, триггер, регистры первого и второго адресов, блок управления, включены ,дополнительно регистр третьего адреса три регистра предыдущей команды, три регистра текущей команды и регистр состояния.Изобретение относится к вылиспи-л"РЛЬНО 11 ТЕХНИКЕ И ПРЕДНЯЗНЯЧЕНО ДЛЯ отображения хода отлаживаемой проГгЯММЫ.11 Г Г" л 1 Лу "Огл 1 пЕН я ягяягетмъгд р ыъШИГл ЕНИЕ ЙУНХТИ 01 ЯЛЬНЫХ ВОЗ 1",ОжНОСТРЙпутем обеспечения одновременногоотображения предь;дущего текущего и ОЯРреднОГО ядрРссВ и команды,ИЯ чертеже приведена уХциснальная схеьья предлагаемого устройства.устройство гля отобр ьжения хода про 1 рамм 1 икро" 381 содержи-. блок 1 зядяь 1 ия рожЫял ОлОк 2 сря:знееия, регистр 3 первого адреса триггер ч,Ртт"Д -л Оег 1-лстОЫ 1 ОЕ 11 Ь дуще 11 КОНДЫи л1 ЕО, Ь: 00, 0лР С.-, П РЯоПл 11,. ВтОрсй 12 и трРийрегистры "1","К ЩЕИ КОМЯНДЬ Л РЕл И. Л 1 Р 1 Л СОСТЛ ЛЛБлок 5 управления Вкл 1 очает в себяпегиств 15 сдвига,. одновибратср 1 д,пес вьлл эл лмен 1 7Рдерхки перв л.-Имя соединен с первым Входом блокаСРЯЗНРН 1 Ял ВтОРОИ ВХОД КОТОРОГОсоединен с инфср 1 яционныч Входом1)еи:тпяЛРВВОГО адреса 11 адрес" НЬлы ВХОДОМ устрс.11 СТВЯ, Я ВьлХОДединичным Входом триггер 1, Нулевой вход которого соРдинен с Втсрьпк ВхоДОЫ ЯДВРОЯ. Остансва б 110 ка , задания Оежима. Н 1 ЯФОрь 1 яписы 1 сь 1 й Вход - с ши-. НОИ ЕПИНИЧНОГО ПОТЕКИВ,1 Я, Я Талктовшй: 1 КЯ -.гС" НДЫ УГ;Р Ройства ВХОДОМ РЯЗВРШЕНГЯ ЗаПИСИ регистоа 15 сдвига блока 5 управления,. через одлновибратор 16 олока 5 упрявлен,Р с хоц 011 ","стяновки 0 Ое-. гистра 15 сдвига блока 5 управления, гяк"1 овьгья Входами регистра о адреса первого 7 Второго 8 и 1 гретье го 9 регистров предыдущей команды и через первый элемент 17 задержки бло ка 5 управления с входами установкив 0 оегиства 10 Второго адреса, первого 11. второго 2 и третьего 13 регистров текущей ком"ндь 1. инвегсный выход триггера 4 соединен с Вьгхэ,цом останова устройства и г:ервым входом первогб элемента И 18 блока 5 управле.Ия, в-Од признака байтаОС:нояллия УСТООллл ТВ Я гОРГУЬлР 11 С ГлслР ВЬЬл ВХОДОу Вт 1 рОГО Э л 1 ллМЕлт; И 1 О б 1 г И(;Л кя 5 управления, выход которого соеди Рь с тактовыми входами регистров 1 А состояния и 3 первого адреса, тактовый Вход устройства соединен с гторыми Входами второго 19 и первого "8 элементов И блока 5 управления, ВыОд которого соединен с тактовым-одом регистра 15 сдвига блока 5 управления и через второй элемент 20 задержки блока 5 управления с тактовыми входами регистра 10 второго адреса, первого 11, второго 12 и третьего 13 регистров текущей команды, входы записи и чтения устройства соединены с входами элемента ИЛИ 21 блока 5 управления, од кстороГО соединен с третьим входом первого элемента И 18 блока 5 управлен:,я, :нфоомяцис 1 ный вход первого разряда рРгистрЯ 15 сДВНГЯ блока 5 управлеН 1 лн СОЕДИНЕН С ШИНОЙ ЕДИНИЧНОГО ПО- тенцияла, а Входы второго, третьегочетвертогс разрядов регистра 15 :двига соединены с шиной нулевого по е 11 пиаг 1 Я, первый выход регистра 15 с 11 вига блока 5 управления соединен ". Входами разрешения записи регистра О второго адреса и первого реГистра 11 текущей команды, второй выход регистра 15 соединен с входом разрешения записи Второго регистра 12 текушлей команды, третий выход регистра 15 сдвига блока 5 управле- ,1-;я соединен с инверсным входом пер" В:ГО элемента И 18 блока 5 управления и Входом разрешения записи третьего регистра 13 текущей команды, 1 ИФормяционный вход устройства соединен с информационными входами первого 11 второго 12 и третьего 113 регистров текущей команды и реГистра 1 ч состояния, информационные Вььходы регистра 10 второго адреса,.-,Ярвого 11, вгорого 12 и третьего 13регистров текущей команды соединенысост в етственно с информационными входяю-., регистра 6 третьего адреса перФзого 7 второго 8 и.третьего 9 регист."ров Г 1 редыдущей команды, выходы разрзше 1 ия индикации первого 11, второГО 1 л 2 и третьего 13 регистров те 1 СлщЕй КОМЯНДЬ 1 СОЕДИНЕНЫ СООтВЕтСтВЕНно с вхоцзми разрешения записи первого 7 второго 8 и третьего 9 регистров предыдущей комацды.устроиствс работает следу 1 ощимОбразомфР. блоке 1 задания режима устанав"ливается адрес останова, который1203постоянно подается на первый вход блока 2 сравнения. При системном сбросе микро-ЭВМ на адресном входе устройства устанавливается нулевой адрес, поступающий на второй вход5 блока 2 сравнения и на информационный вход регистра 3 первого адреса, В это время на информационном входе устройства микро-ЭВМ выставляет байт состояния, на входе признака байта 10 состояния появляется единичный потенциал, поступающий на первый вход второго элемента И 19 блока 5 управления, на второй вход которого, соединенный с тактовым входом устройства, поступает синхроимпульс. Элемент И 19 повторяет импульс, который записывает байт состояния в регистр 14 состояния и адрес и регистр 3 первого адреса, н зто же время на входе 20 признака команды устройства появляется логическая "1", по появлению которой триггер 4 переводится н единичное состояние, а на инверсном выходе и на выходе останова устройства 25 появляется признак останова - логический 0, который также поступает на первый вход первого элемента И 18 блока 5 управления, блокируя работу устройства. Кроме того, по фронту признака команды одновибратор 1 б блока 5 управления вырабатывает импульс установки н "0 регистра 15 сдвига блока 5 управления, который также является импульсом записи в регистр б третьего адреса, первого 7, вта 35 рого 8 и третьего 9 регистров предыдущей команды, а с задержкой на элементе 17 задержки вырабатывается чмпульс установки в "0" регистра 1040 второго адреса, первого 11, второго 12, третьего 13 регистров текущей команды. Кроме того, признак команды поступает на вход разрешения записи регистра 15 сдвига блока 5 управле 45 ния, осуществляя запись в него кода, установленного на информационных входах. В таком состоянии устройстно кдет поступления импульса запуска с блока 1 задания режима.50По поступлении импульса запуска с второго выхода блока 1 задания режима триггер 4 устанавливается в логический "0, снимает признак оста- нова, как следствие, микро-ЭВМ выс тавляет сигнал чтения и на информационных входах появляется код команды. При приходе следующего син 304хроимпульса ка тактовый вход устройства ок через герньп элемент И 18 поступает на тактовый вход регистра 15 сдвига блока 5 управления, осуществляется сдвиг кода, логическая "1" поступает на входы разрешения записи регистра 10 второго адреса и первого регистра 11 текущей команды, разрешая запись. Кроме того, синхроимпульс с задержкой, обусловленной элементом 20 задержки, поступает на тактовые входы регистра 10 второго адреса, перного 11, второго 12 и третьего 13 регистров текущей команды, осуществляется запись информации только в те иэ указанных регистров, на входах разрешения записи которых присутствует логическая "1", т.е. в данном случае в регистр 10 второго адреса переписывается адрес команды из регистра 3 первого адреса, а в первый регистр 11 текущей команды записывается код команды с информационного входа устройства. Если выполняемая команда имеет длину два или три байта, то микро- ЭВМ меняет адрес на адресных входах устройства и выставляет новый байт сс:таяния, которые снова после запуска с блока задания режима записываются н регистры 3 первого адреса и 14 состояния по совпадению синхраимпульса на тактовом входе устройства и признака на входе признака состояния, Зятем микро-ЭВМ выставляет на информационном входе устройства второй байт команды и выдает сигнал на одном из входов устройства чтения или записи, при этом синхроимпульс с выхода элемента И .18 поступает на тактовый вход регистра 15 сдвига, осуществляется сдвиг кода, на втором выходе устанавливается логическая "1", при этом синхроимпульс через элемент 20 задержки осуществляет запись во второй регистр 12 текущей команды. Аналогично осуществляется запись третьего байта в третий 13 регистр текущей команды, а также их адреса в регистр 3 и байта состояния в регистр 14 состояния, при этом логическая "1" с третьего выхода регистра 15 сдвига блокирует по инверсному входу первый элемент И 18. При выполнении более короткой команды, состоящей иэ одного или двух байтов, запись происходит анаIлогично с той разницей, что к устройству приходят одно или два обращения по входам чтения или записи вместо трех, Далее микро-ЭВМ опять меняет адрес и выставляет новый байт состояния (признак состояния), при этом осуществляется запись адреса и состояния в регистры 3 первого адреса и 14 состояния, затем приходит признак команды, который переводит триггер 4 в режим останова, устанавливает в. "0" регистр 15 сдвига, переписывает всю информацию из регистра 10 второго адреса, первого 11, второго 12 и третьего 13 регистров байта текущей команды в регистр 6 третьего адреса, первый 7, второй 8 и третий 9 регистры байтов предыдущей команды, после1 л 1 чего осуществляется сброс в 0 регистра 10 второго адреса, первого 11, второго 12 и третьего 13 регистров байтов текущей команды. Далее происходит исполнение второй команды и т.д. При этом в регистрах 6-9 - адреса и байты предыдущей команды, в регистрах 10 - 13 - адреса и байты текущей команды, а в регистрах 3 и 14- адрес перехода и байт состояния,Регистры первого 3, второго 10 и третьего 6 адресов, а также первые 11 и 7, вторые 12 и 8 и третьи 13 и 9 регистры соответственно текущей и предыдущей команды и регистр 14 состоякия выполнены с индикацией значения в шестнадцатиричной Форме. Индикация осуществляется только в случае, если к регистру было обращение..Формула изобретенияУстройство для отображения хода программ микро-ЭВМ содержащее блок задания режима, блок сравнения, триггер, регистр первого адреса, регистр второго адреса и блок управления, включающий первый и второй элементы задержки, причем адресный вход устройства соединен с информационным входом регистра первого адреса и первым входом блока сравнения, выход сравнения которого соединен с единичным входом, триггера, выход адреса останова блока задания режима соединен с вторым входом блока сравнения, инверсный выход триггера является выходом останова устройства, выход регистра первого адреса соединен с информационным входом регистра второго адреса, о т л и ч а ю щ е е с я тем, что, с целью расшлрекия Функциональных возможностей путем обеспечения одновременного отображения предыдущего, текущего и очередного адресови команды, в него введены регистртретьего адреса, первый, второй итретий регистры предыдущей команды,.первьп, второй и третий регистры текущей команды и регистр состояния, а1; в блок управления введены первый ивторой элементы И, элемент ИЛИ,одновибратор и регистр сдвига, причем инверсный выход триггера соединен с первым входом первого элемекта И блока управления, вход признака команды устройства соединен с,тактовым входом триггера, входом разрешения записи регистра сдвига, через одновибратор с входом установкинуля регистра сдвига блока управле 2 С 1ния, с тактовыми входами регистратретьего адреса, первого, второгои третьего регистров предыдущей команды и через первый элемент задержки блока управления с входами устаЗО юю 1 еновки в 0 регистра второго адресаи первого, второго и третьего регистров текущей команды, вход признакабайта состояния устройства соединенс первым входом второго элемента Иблока управления, выход которого соединен с тактовыми входами регистрасостояния и регистра первого адреса,тактовый вход устройства соединенс вторыми входами второго и первогоэлементов И блока управления, выходкоторого соединен с тактовым входомрегистра сдвига и через второй эле -мент задержки блока управления стактовыми входами регистра второго садреса, первого, второго и третьегорегистров текущей команды, входызаписи и чтения устройства соединены с соответствующими входами элемента ИЛИ, выход которого соединенс третьим входом первого элемента И. блока управления, информационныевходы первого и второго разрядоврегистра сдвига блока управления соединены соответственно с ши;-.й нулевого и единичного потенциалов устройства, входы третьего и четвертогоразрядов регистра сдвига блока управления соединены с шиной нулевого1203530 Составитель И. СигаловР едактор О, Юрковецкая Техред М, Надь Корректор М. Пакошш шиш шшЮодписное 8418/52ВНп13035, М ир ИИПИ Государственн делам изобретен ква, Ж, Рауш709 го комитета СС ий и открытий кая наб, д Патент", г. Ужгород, улПр 4 т потенциала устройства, первый выходрегистра сдвига блока управлениясоединен с входами разрешения записирегистра второго адреса и первогорегистра текущей команды, второйвыход регистра сдвига блока управлениясоединен с входом разрешением записи второго регистра текущей команды,третий выход регистра сдвига блокауправления соединен с инверсным входом первого элемента И блока управления и входом разрешения записитретьего регистра текущей команды,информационный вход устройства соединен с информационными входами первога, второго и третьего регистровтекущей команды и регйстра состояния, информационные выходы регистравторого адреса, первого, второго итретьего регистров текущей командысоединены соответственно с информационными входами регистра третьегоадреса, первого, второго и третьего 1 О регистров предыдущей команды, выходыразрешения индикации первого, второгои третьего регистров текущей команды соединены соответственно с входамиразрешения записи первого, второгои третьего регистров предыдущей команды.

СмотретьЗаявка

3713910, 11.03.1984

КИШИНЕВСКОЕ ОТДЕЛЕНИЕ ВСЕСОЮЗНОГО НАУЧНО-ИССЛЕДОВАТЕЛЬСКОГО ИНСТИТУТА ТОКА НАУЧНО-ПРОИЗВОДСТВЕННОГО ОБЪЕДИНЕНИЯ "КВАНТ"

НИКОЛАЙЧУК ОЛЕГ ИГОРЕВИЧ

МПК / Метки

МПК: G06F 11/28

Метки: микро-эвм, отображения, программ, хода

Опубликовано: 07.01.1986

Код ссылки

<a href="https://patents.su/5-1203530-ustrojjstvo-dlya-otobrazheniya-khoda-programm-mikro-ehvm.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для отображения хода программ микро-эвм</a>

Предыдущий патент: Устройство для обслуживания запросов

Следующий патент: Устройство для обмена данными между вычислительными машинами

Случайный патент: Рабочий орган вентиляторного опрыскивателя