Устройство для сбора, кодирования, передачи и приема информации с исправлением ошибок

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1141439

Авторы: Анищенко, Антоневич, Коялис, Сабаляускас

Текст

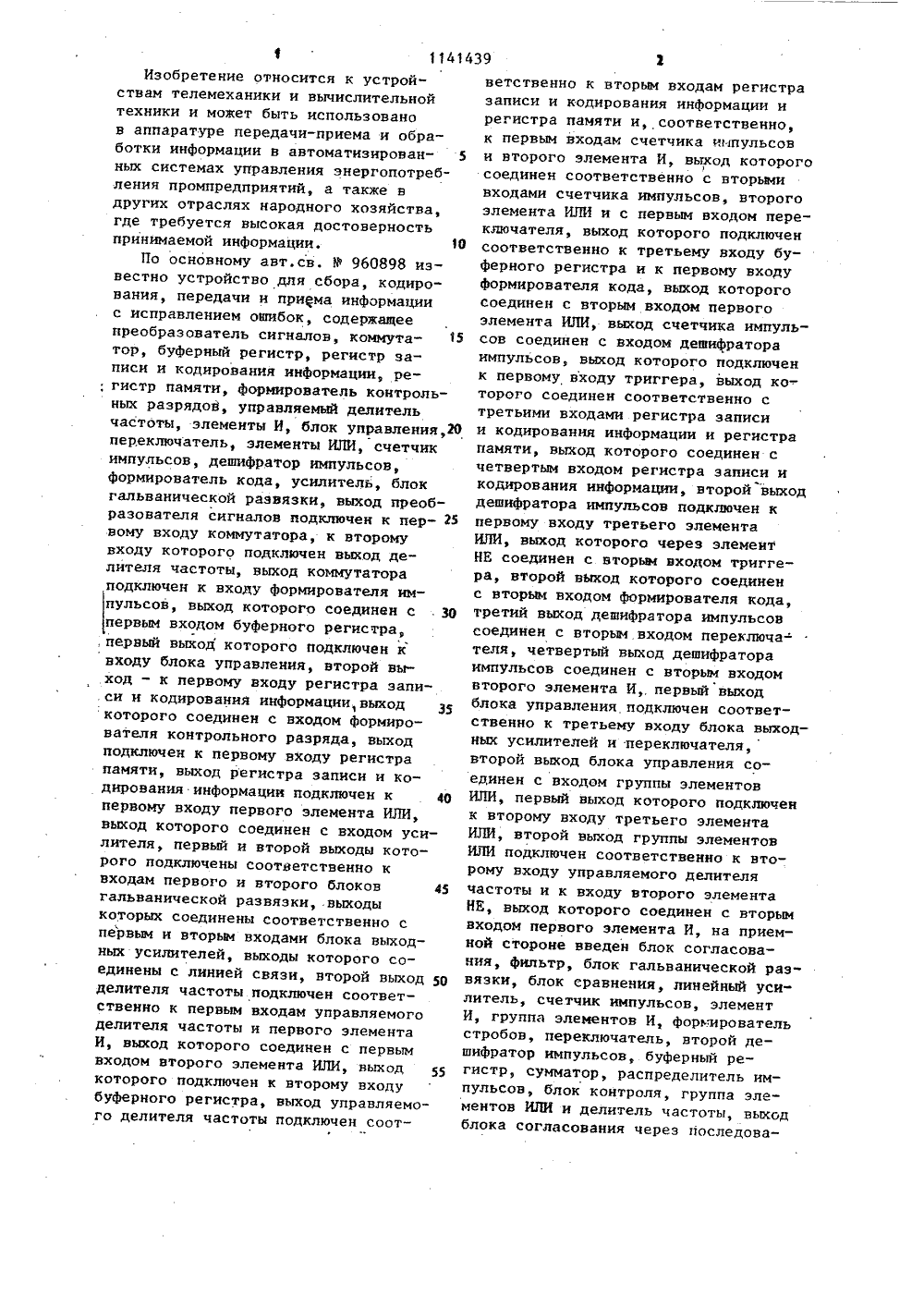

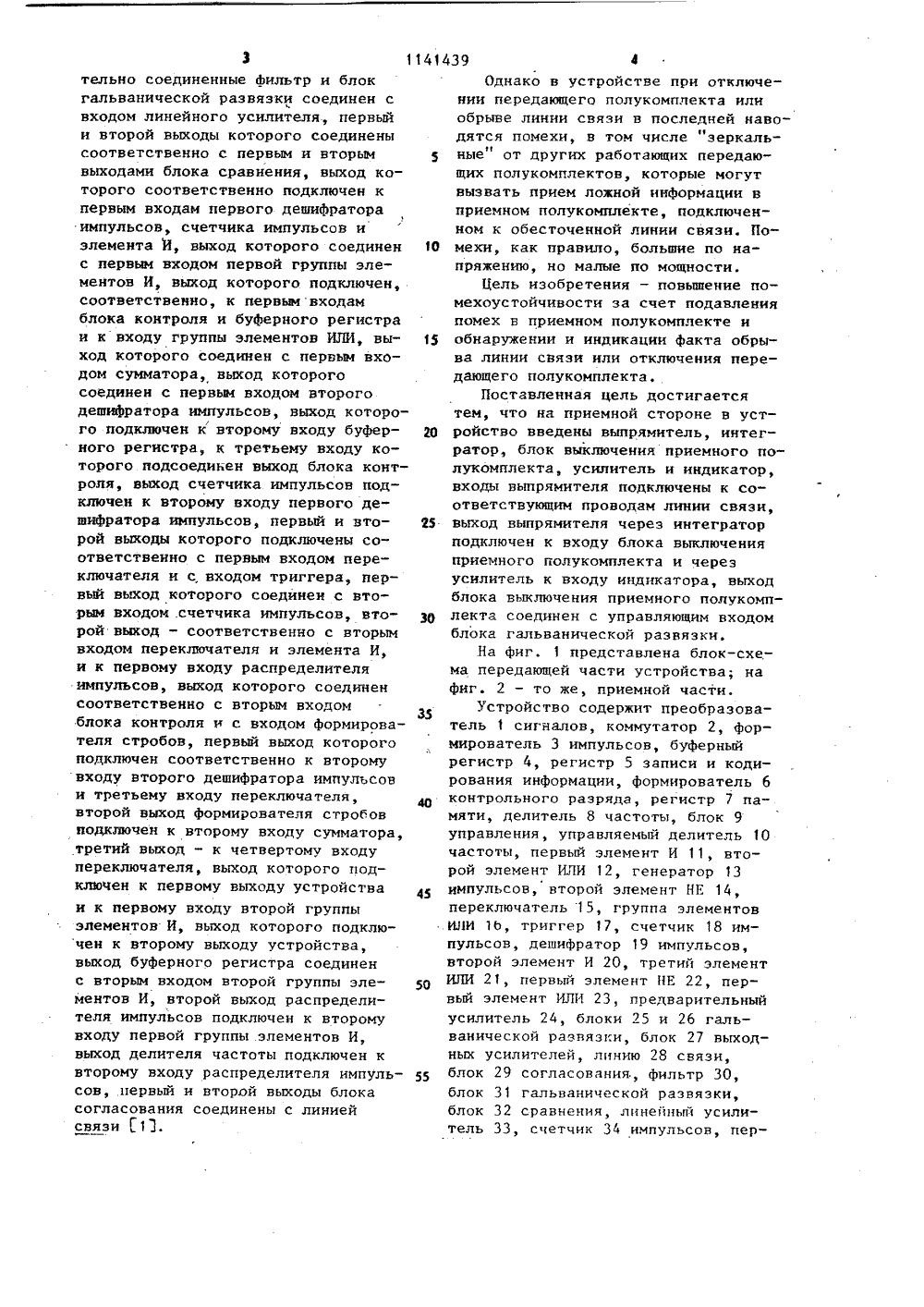

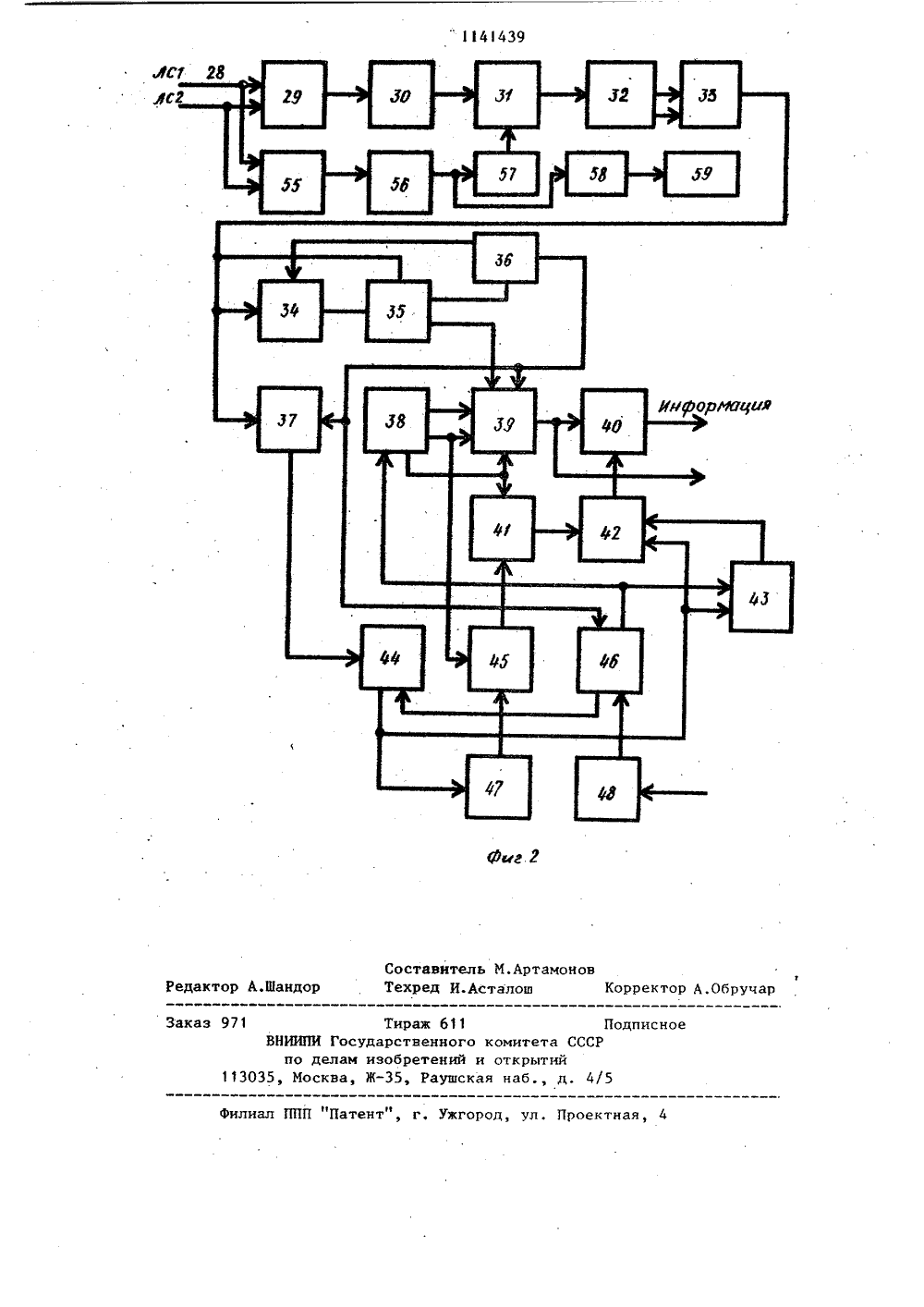

(19) ЪР 1 аР . Ф( С 08 С 25/04 ОПИСАНИЕ ИЗОБРЕТЕНИ нтоневичскаслектроиз детельство СС /04, 1980.ДЛЯ СБОРА, КОПРИЕМА ИНФОР ОШИБОК по л и ч а юГОСЗЩАРСТВЕННЫЙ ХОМИТЕТ СССР00 ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТНРЫПЮМ АВТОРСКОМУ СВИД;(71) Вильнюсский заводрительной техники(54)(57) УСТРОЙСТВОДИРОВАНИЯ, ПЕРЕДАЧИ ИМАЦИИ С ИСПРАВЛЕНИЕМавт.св. У 960898, о т щ е е с я тем, что, с целью повышения помехоустойчивости устройства,в него дополнительно введены выпрямитель, интегратор, блок выключения приемного полукомплекта, усилитель и индикатор, входы выпрямителяподключены к соответствующим проводам линии связи, выход выпрямителячерез интегратор подключен к входублока выключения приемного полукомплекта и через усилитель - к входуиндикатора, выход блока выключенияприемного полукомплекта соединен суправляющим входом блока гальванической развязки.Изобретение относится к устройствам телемеханики и вычислительной техники и может быть использовано в аппаратуре передачи-приема и обработки информации в автоматизирован ных системах управления энергопотребления промпредприятий, а также в других отраслях народного хозяйства, где требуется высокая достоверность принимаемой информации.10По основному авт.св. У 9 б 0898 известно устройство для сбора, кодирования, передачи и приема информации с исправлением ошибок, содержашее преобразователь сигналов, коммута тор, буферный регистр, регистр записи и кодирования информации, ре; гистр памяти, формирователь контрольных разрядой, управляемый делитель частоты, элементы И, блок управления,20 переключатель, элементы ИЛИ, счетчик импульсов, дешифратор импульсов, формирователь кода, усилитель, блок гальванической развязки, выход преобразователя сигналов подключен к пер вому входу коммутатора, к второму входу которого подключен выход делителя частоты, выход коммутатора подключен к входу формирователя импульсов, выход которого соединен с . 30 первым входом буферного регистра, первый выход которого подключен к входу блока управления, второй выход - к первому входу регистра запи,си и кодирования информации, выход которого соединен с входом формирователя контрольного разряда, выход подключен к первому входу регистра памяти, выход регистра записи и кодирования информации подключен к 0первому входу первого элемента ИЛИ, выход которого соединен с входом усилителя, первый и второй выходы которого подключены соответственно к входам первого и второго блоков 45гальванической развязки, выходы которых соединены соответственно спервым и вторым входами блока выходных усилителей, выходы которого соединены с линией связи, второй выход 50 делителя частоты подключен соответственно к первым входам управляемого делителя частоты и первого элемента И, выход которого соединен с первымвходом второго элемента ИЛИ, выход 55 которого подключен к второму входу буферного регистра, выход управляемого делителя частоты подключен соответственно к вторым входам регистразаписи и кодирования информации ирегистра памяти и, соответственно,к первым входам счетчика импульсови второго элемента И, выход которогосоединен соответственно с вторымивходами счетчика импульсов, второгоэлемента ИЛИ и с первым входом переключателя, выход которого подключенсоответственно к третьему входу буферного регистра и к первому входуформирователя кода, выход которогосоединен с вторым входом первогоэлемента ИЛИ, выход счетчика импульсов соединен с входом дешифратораимпульсов, выход которого подключенк первому входу триггера, выход которого соединен соответственно стретьими входами регистра записии кодирования информации и регистрапамяти, выход которого соединен счетвертым входом регистра записи икодирования информации, второй выходдешифратора импульсов подключен кпервому входу третьего элементаИЛИ, выход которого через элементНЕ соединен с вторым входом триггера, второй выход которого соединенс вторым входом формирователя кода,третий выход дешифратора импульсовсоединен с вторым. входом переключа-теля, четвертый выход дешифратораимпульсов соединен с вторым входомвторого элемента И, первый выходблока управления подключен соответственно к третьему входу блока выходных усилителей и переключателя,второй выход блока управления соединен с входом группы элементовИЛИ, первый выход которого подключенк второму входу третьего элементаИЛИ, второй выход группы элементовИЛИ подключен соответственно к второму входу управляемого делителячастоты и к входу второго элементаНЕ, выход которого соединен с вторымвходом первого элемента И, на приемной стороне введен блок согласования, фильтр, блок гальванической развязки, блок сравнения, линейный усилитель, счетчик импульсов, элементИ, группа элементов И, форнировательстробов, переключатель, второй дешифратор импульсов, буферный регистр, сумматор, распределитель импульсов, блок контроля, группа элементов ИЛИ и делитель частоты, выходблока согласования через последовательно соединенные фильтр и блокгальванической развязки соединен свходом линейного усилителя, первыйи второй выходы которого соединенысоответственно с первым и вторымвыходами блока сравнения, выход которого соответственно подключен кпервым входам первого дешифратораимпульсов, счетчика импульсов иэлемента И, выход которого соединенс первым входом первой группы элементов И, выход которого подключен,соответственно, к первьвювходамблока контроля и буферного регистраи к входу группы элементов ИЛИ, выход которого соединен с первым входом сумматора, выход которогосоединен с первым входом второгодешифратора импульсов, выход которого подключен к второму входу буферного регистра к третьему входу которого подсоединен выход блока контроля, выход счетчика импульсов подключен к второму входу первого дешифратора импульсов, первый и второй выходы которого подключены соответственно с первым входом нереключателя и с,входом триггера, первый выход которого соединен с вторым входом .счетчика импульсов, второй выход - соответственно с вторымвходом переключателя и элемента И,и к первому входу распределителяимпульсов, выход которого соединенсоответственно с вторым входомблока контроля и с входом формирователя стробов, первый выход которогоподключен соответственно к второмувходу второго дешифратора импульсови третьему входу переключателя,второй выход формирователя стробовподключен к второму входу сумматора,третий выход - к четвертому входупереключателя, выход которого подключен к первому выходу устройстваи к первому входу второй группыэлементов И, выход которого подключен к второму выходу устройства,выход буферного регистра соединенс вторым входом второй группы элементов И, второй выход распределителя импульсов подключен к второмувходу первой группы элементов И,выход делителя частоты подключен квторому входу распределителя импульсов, первый и второй выходы блокасогласования соединены с линиейсвязи11,5 10 5 20 25 30 35 40 45 50 55 Однако в устройстве при отключении передающего полукомплекта илиобрыве линии связи в последней наводятся помехи, в том числе зеркальные от других работающих передающих полукомплектов, которые могутвызвать прием ложной информации вприемном полукомплекте, подключенном к обесточенной линии связи. Помехи, как правило, большие по напряжению, но малые по мощности.Цель изобретения - повышение помехоустойчивости эа счет подавленияпомех в приемном полукомплекте иобнаружении и индикации факта обрыва линии связи или отключения передающего полукомплекта,Поставленная цель достигаетсятем, что на приемной стороне в устройство введены выпрямитель, интегратор, блок выключения приемного полукомнлекта, усилитель и индикатор,входы выпрямителя подключены к соответствующим проводам линии связи,выход выпрямителя через интеграторподключен к входу блока выключенияприемного полукомплекта и черезусилитель к входу индикатора, выходблока выключения приемного полукомплекта соединен с управляющим входомблока гальванической развязки,На фиг. 1 представлена блок-схема передающей части устройства; нафиг. 2 - то же, приемной части,Устройство содержит преобразователь 1 сигналов, коммутатор 2, формирователь 3 импульсов, буферныйрегистр 4, регистр 5 записи и кодирования информации, формирователь 6контрольного разряда, регистр 7 памяти, делитель 8 частоты, блок 9управления, управляемый делитель 10частоты, первый элемент И 11, второй элемент ИЛИ 12, генератор 13импульсов, второй элемент НЕ 14,переключатель 15, группа элементов.ИЛИ 1 Ь, триггер 17, счетчик 18 импульсов, дешифратор 19 импульсов,второй элемент И 20, третий элементИЛИ 21, первый элемент НЕ 22, первый элемент ИЛИ 23, предварительныйусилитель 24, блоки 25 и 26 гальванической развязки, блок 27 выходных усилителей, линию 28 связи,блок 29 согласования фильтр 30,блок 31 гальванической развязки,блок 32 сравнения, линейный усилитель 33, счетчик 34 импульсов, пер 1141Фвый дешифратор 35 импульсов, триггер36, элемент И 37 формирователь 38стробов, переключатель 39, вторуюгруппу элементов И 40, второй дешифратор 41 импульсов, буферный регистр 42, блок 43 контроля, вторуюгруппу элементов И 44, сумматор 45,распределитель 46 импульсов, группуэлементов ИЛИ 47, делитель 48 частоты, формирователь 49 кода.Блок 26 гальванической развязки26 содержит оптрон 50, стабилитрон51, резисторы 52 и 53 транзистор54 и источник питания (не показан).Приемный полукомплект устройствадополнительно содержит выпрямитель55, интегратор 56, блок 57 выключения приемного полукомплекта, усилитель 58 и индикатор 59,Устройство работает следующим образом.С выхода передающего полукомплекта сигнал через линию связи 28 (приотсутствии информации передатчик передает сигнал, соответствующий информации "0) поступает на блоксогласования 29 приемного полукомплекта 3, далее на фильтр 30, блок31 гальванической развязки 6 и линейный усилитель 33, где он фильт 439руется, декодируется и, при необходимости, исправляется от одиночнойошибкиОдновременно с блоком согласования 29 сигнал с линии связи 5 28 поступает на выпрямитель 55, навыходе которого при необесточеинойлинии связи (при необорванной линиисвязи и не отключенном передатчике)присутствует постоянное напряжение.10 Это напряжение поступает на входинтегратора 56, При наличии сигнала.с интегратора 56 блок 57 выключенияприемного полукомплекта держит управляющий ключ блока 31 гальваническойразвязки в открытом состоянии,тем самым разрешая прием информациис линии связи. Одновременно сигналс интегратора 56 через усилитель58 с порогом срабатывания поступа ет на индикатор 59, который показывает нормальную работу приемопередатчика, При обесточенной линиисвязи маломощная помеха (в томчисле "зеркальная" ) не вызывает фф появления нужного для открыванияуправляющего ключа блока 31 гальванической развязки сигнала. Такимобразом, приемный нолукомплект 3отключается, и этот факт покаэывает- ЗО ся на индикаторе 59..Шандор Техред И.Асталош Корректор А,Обручар Редак аз 971 ПоцписноСССР мит открытиия наб., д. 4/5 лиал 1 П 1 П "Патент", г. Ужгород, ул. Проектная ВНИИНИ по дел 113035, Моск

СмотретьЗаявка

3546277, 31.01.1983

ВИЛЬНЮССКИЙ ЗАВОД ЭЛЕКТРОИЗМЕРИТЕЛЬНОЙ ТЕХНИКИ

АНИЩЕНКО АЛЕКСАНДР ДМИТРИЕВИЧ, АНТОНЕВИЧ ВАЛЕРИЙ ФЕДОРОВИЧ, КОЯЛИС ВИТАУТАС КОСТОВИЧ, САБАЛЯУСКАС АЛЬГИМАНТАС ИОНОВИЧ

МПК / Метки

МПК: G08C 25/04

Метки: информации, исправлением, кодирования, ошибок, передачи, приема, сбора

Опубликовано: 23.02.1985

Код ссылки

<a href="https://patents.su/5-1141439-ustrojjstvo-dlya-sbora-kodirovaniya-peredachi-i-priema-informacii-s-ispravleniem-oshibok.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для сбора, кодирования, передачи и приема информации с исправлением ошибок</a>

Предыдущий патент: Устройство для приема информации

Следующий патент: Тренажер оператора систем управления

Случайный патент: Однотактный преобразователь постоянного напряжения