Устройство для обнаружения и локализации ошибок при передаче информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1051541

Авторы: Кондратьев, Чукавин

Текст

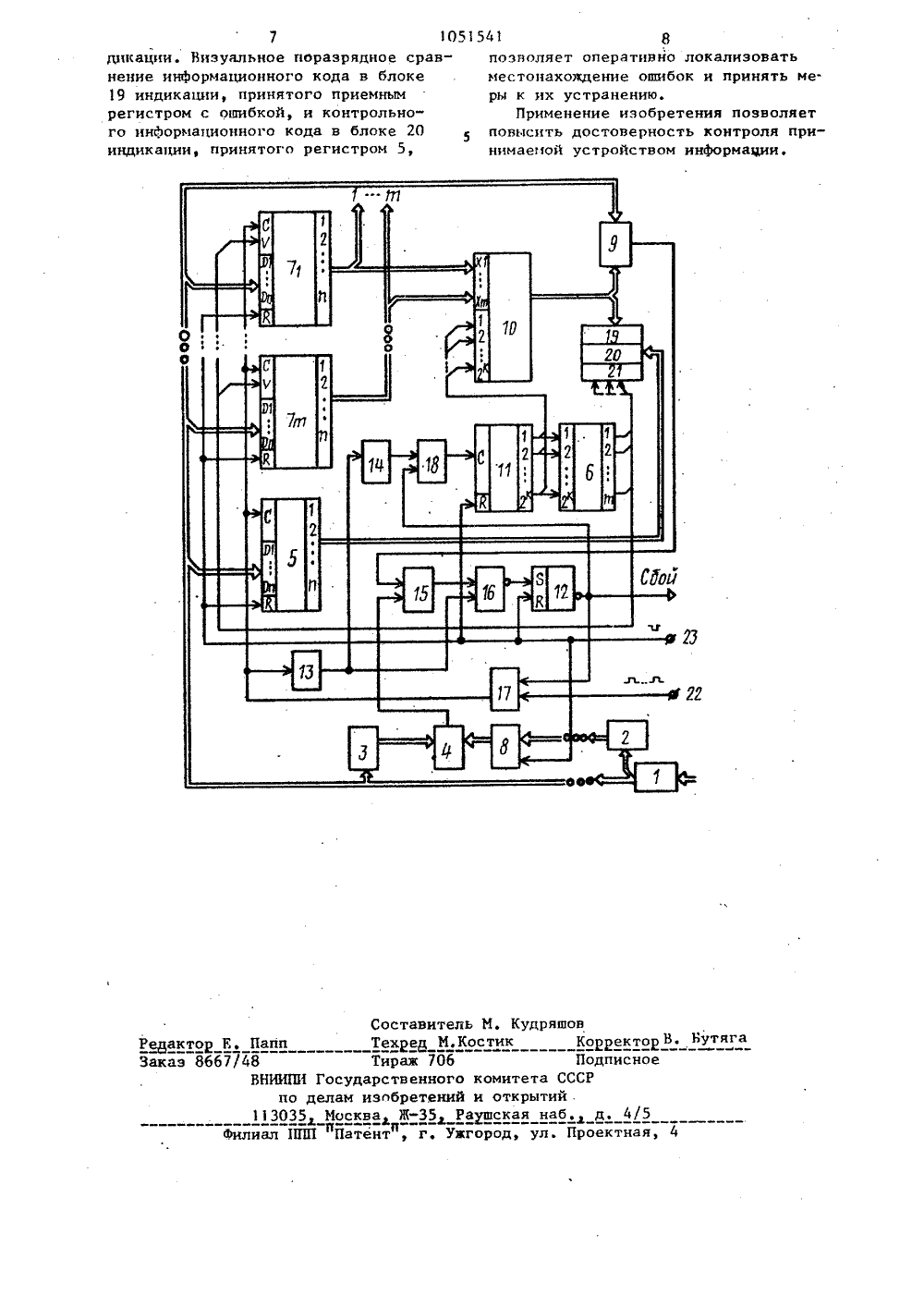

1 Ш СОЮЗ СОВЕТСКИХСОЦИАЛИСТИЧЕСКИХРЕСПУБЛИК Ф09) (11) Зся) а О 6 Г 11/О ЗОБ ОПИСА АВТОРСНО ЛЬСТ ГОСУДАРСТВЕННЫЙ КОМИТЕТ СССРПО ДЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЬ 1 ТИЙ(56) 1, Авторское свидетельстно СССР Р 56 1965, кл. С 1 06 Г 11/00, 1977,2. Авторское свидетельство СССР Р 445045, кл, С 06 Р 11/08, 1974 (прототип).(54)(57) УСТРОЙСТВО ДЛЯ ОБНАРЛИНИЯ. И ЛОКА)П 1 ЗАЦИИ ОИИБОК ПРИ ПЕРЕДАЧЕ ИНФОРИА 11 И 11, содержащее входной регистр, первый и второй блоки свертки по модулю два, схему сравнения контрольных разрядов, регистр ошибки, регистр контрольных разрядов, дешифратор и группу приемных регистров, информационные входы которых подключены к выходам входного регистра и к входам первого блока свертки по модулю два, выходы которого подключены к входам регистра контрольных разрядов, первая и вторая группы входов схемы сравнения контрольных разрядов соединены соответственно с выходами регистра контрольных разрядов и второго блока сверт" ки но модулю два, выходы дешифратора подключены к управляющим входам соответствующих приемных регистров группы, о т л и ч а ю щ е ес я тем, что, с целью повышения достоверности контроля путем обнаружения многократных ошибок, в него дополнительно введены два элемента И, элемент ИЛИ, элемент И-НЕ, два элемента задержки, счетчик, три блока индикации, триггер сбоя, схема сравнения информационных разрядов и коммутатор, выходы которого подключены к входу первого блока индикации и к первой группе входов. схемы сравнения информационных разрядов, выход которой подключен к первому входу элемента ВП 1, выход которого соединен с первым входом элемента И-НЕ, выход которого соединен с единичным входом триггера сбоя, инверсный выход которого подключен к первым входам первого и второго элементов И, вторые входы которых подключены соответственно к выходу первого элемента задержки и к входу синхронизации устройства, выход первого элемента И подключен к счетному входуФ счетчика, выходы которого соединены с входами деюифратора и управляющими входами коммутатора, информационные входы которого подключены к информационнымвыходам соответствующихе приемных регистров группы, синхронизирующие входы которых подключены к выходу второго элемента И и через второй элемент задержки к второму входу элемента И-НЕ и к входу первого элемента задержки, выход схемы сравнении контрольных разрядов подключен к второму входу элемента ИЛИ, нходы второго блока свертки по модулю дна, вторая группа входон схемы. сравнения информационных разрядов и информационные нходы регистра ошибки подключены к выходам входного регистра, выходы регистра ошибки и дешиФратора подключены соответственно к входам второго и третьего блоков индикации, вход синхронизации регистра ошибки соединен с выходом второго элемента И, выходы приемных регистров являются информационными10515 ц 1выходами устройства, выход сбоя уст-, ва соединен с входами сброса всехройства соединен с инверсным выходом регистров, с входом сброса триггератриггера сбоя, вход сброса устройст- сбоя и счетчика.1Изобретение относится к вычислительной технике и может быть использовано в устройствах контроля при пе.редаче цифровой информации из ЭВМв периферийные устройства, 5Известно устройство для обнаружения неисправностей цифровых систем,содержащее постоянный запоминающийблок, блок управления, счетчик команд, блок вывода информации, входные и выходные коммутаторы, блоксравнения, регистр приема информации, сумматор, схему И, схему ИЛИ иблок индикации 111,Однако данное устройство имеет 15сложную схему,Наиболее близким техническим решением к предлагаемому является устройство для обнаружения и локализацииодиночных ошибок при передаче цифровой информации. Данное устройстводля обнаружения и локализации одиночных ошибок при передаче цифровойинформации содержит приемный регистринформации подключенный, линией 25связи к передающему регистру, выходыкоторого соединены с входами первойсхемы кодирования, к выходам которойчерез линию связи подключены входыприемного регистра контрольных разрядов, выходы которого подключены ксхеме сравнения, вторую схему кодиро"вания и регистр ошибки, выходы которого через дешифратор слова ошибкисоединены с входами приемного регистра, причем вторая схема кодированиявключена между приемным регистроми схемой сравнения, выход которойподключен к входу регистра ошибки а-эОднако данное устройство для об"наружения и локализации одиночныхошибок при передаче цифровой информации не позволяет обнаруживать одновременные многократные ошибки (двеи более) при приеме цифрового кодаприемным регистром информации. Кроме того, недостатком данного устрой 2ства является прямая зависимость роста дополнительных схем коцирования при увеличении количества приемных регистров и отсутствие визуальной индикации содержимого в ошибочном информационном коде.Цель изобретения - повышение достоверности контроля путем обнаружения многократных ошибок.11 оставленная цель достигается тем, что в устройство для обнаружения и локализации ошибок при передаче инФормации, содержащее входной регистр, первый и второй блоки свертки по модулю два, схему сравнения контрольных разрядов, регистр ошибки, регистр контрольных разрядов, дешифратор и группу приемных регистров, информационные входы которых подключены к выходам входного регистра и к входам первого блока свертки по модулю два, выходы которого подключены к входам регистра контрольных разрядов, перФ вая и вторая группы входов схемы . сравнения контрольных разрядов соединены соответственно с выходами регистра контрольных разрядов и второго блока свертки по модулю два, выходы дешифратора подключены к управляющим входам соответствутощих приемныхрегистров группы, введены два элемента И, элемент И 1 П 1, элемент И-НЕ, два элемента задержки, счетчик, три блока индикации, триггер сбоя, схема сравнения информационных разрядови коммутатор, выходы которого подключены к первому блоку индикации и к первым входам схемы сравнения информационных разрядов, выход которой подкпючен к первому входу элемента ИЛИ, выход которого соединен с первым входом элемента И-НЕ, выход которого соединен с единичным входом триггера сбоя, инверсный выход которого подключен на первые входы первого и второго элементов И, вторые,входы которых подключены соответственно к выходу первого элементазадержки ц к входу синхронизации устройства, выход первого элемента И подключен к счетному входу счетчика, выходы которого соединены с входами дешифратора и управляющими входами коммутатора, информационные входы которого подключены к информационным выходам соответствующих приемных регистров группы, сцнхронизцрующие входы которых подкпючены к выходу О второго элемента И и через второй элемент задерж:ц к второму входу элемента И-НЕ и к входу первого элемента задержки, выход схемы сравнения контрольных разрядов подключен к вто рому входу элемента ИЗП 1, входь второго блока свертки по модулю два, вто-рые входы схемы сравнения информационных разрядов и информационные входы регистра ошибки подключены к выходам входного регистра, выходы регистра ошибки и дешифратора подключены соответственно к второму и третьему блокам индикации соответственно, вход синхронизации регистра ошиб ки соединен с выходом второго элемента И, выходы приемных регистров являются информационными выходами устройства, выход сбоя устройства соединен с инверсньп выходом тригге 30 ра сбоя, вход сброса устройства соединен с входами сброса всех регистров, с входом сброса триггера сбоя и счетчика.На чертеже приведена схема устройства для обнаружения и локализации ,ошибок при приеме информации.Устройство содержит входной регистр 1, блоки 2 и 3 свертки по модулю два, схему 4 сравнения контрольных разрядов, регистр 5 ошибки, дешифратор 6, приемные регистры 7 -7; группы, регистр 8 контрольных разрядов, схему 9 сравнения информационных разрядов, коммутатор 10, счетчик 11, триггер 12 сбоя, элементы 13 и 45 14 задержки, элемент ИЛИ 15, элемент И-НЕ 16, элементы И 17 и 18, блоки 19-21 индикации, вход 22 синхронизации устройства, вход 23 сброса устройства. 50Устройство работает следуюпрм об, разом.Импульсом сброса, поступающим по входу 23, устанавливаются в исходноесостояние приемные регистры 7 -7 л, 55 регистр 5 ошибки, двоичный счетчик 11 ц триггер 12 сбоя и регистр 8, при этом на инверсном выходе тригге. ра 12 сбоя устаанлцается еднчИп лоГЪГвский уровень сцгализцруюц об отсутствии сигнаа сбояи разрешающий прохождение импульсовзаписи, поступающих по входу 22синхронизации через элемент Ц 17. Спервого выхода дешцфратора 6 поступает единичный логический уровеньна управляют вход приемного регистра 71, подготавливая его к приемуинформации с входного регистра 1,при этом на управляющие входы остальных приемных регистров 7 с выхо- .дов дешцфратора 6 подаются нулевыелогические уровни, запрещающие прием информаци, В исходном состояниикоммутатор 10 подключает информационни выход приемного регистра 7 кпервм входам схемы 9 сравнения ик входам блока 19 индикации, приэтом транспаранты блоков 9-21 индикации высвечивают нулевой код.В общем случае запись информациис регистрав приемные регистры7 -71 производится поочередно н виде информационных слов, сопровождаемых цмпульсаыц записи по входу 22синхронизации,Управление почередной записью инФормационных слов в приемные регистры 7 -7 п производится двоичным счетчиком 1 через дешифратор б следующим образом. 11 о заднему фронту первого импульса записи информационноеслово с выхода регистра 1 заноситсяв приемньш регистр 7 и регистр 5онбкц, Этот же импульс записи, задержанный элементом 13 задержки навремя срабатывания приемного регистра 71, коммутатора 10 ц схемы 9 сравнения, поступает на вход счетчика 11через элемент 14 задержки ц элементИ 18. Информационное слово с выхода приемного регистра 7 поступаетчерез коммутатор 1 О на схему 9 сравнения, где поразрядно сравниваетсяс информационным словом, поступившимна информационные входы приемногорегистра 7,Нри положительном результате контроля на выходе схемы 9 поразрядного сравнения, так же как и на выходе схемь 4 сравнения контрольных раз.рядов, сохраняется нулевой логический уровень, которьш поступает через элемент ИЗП 1 15 на элемент И-НЕ 6, на выходе которого сохраняется единичный логический уровень, грцэтом триггер 12 сбоя остается в исходном состоянии.Йо заднему фронту первого импульса записи, задержанного элементами 13 и 14 задержки, переключается дво ичный счетчик 11 и переводится в следующее (второе) положение коммутатор 10, при этом к схеме 9 сравнения подключается выход следующего приам.ного регистра (7) на управляющий вход которого с второго выхода дешифратора 6 поступает единичный логический уровень, разрешающий прием (зались) информации, На управляющие входы остальных приемных регистров поступает нулевой логический уровень, блокирующий прием информацииПо заднему Фронту второго импульса записи следующее информационное слово с выхода передающего регистра 2 О 1 заносится в приемный регистр 7 ,и в регистр 5 ошибки. В дальнейшем аналогично описанному выше лроизводится поразрядное сравнение информационного слова, записанного в при емный регистр 2 с информационньм словом, поступившим на его вход, При положительном результате сравнения производится переключение наприем следуюцего информационного слова и тедаОбнаружение и локализация ошибок в данном устройстве производится по двум направлениям: непосредственно при,передаче. информационного слова и при приеме (записи) его в приемные регистры 71 в .7,.В первом случае производится конт" роль с целью обнаружения однократных ошибок, возникающих при передаче информационного слова с выхода передаюцего регистра 1. Контроль осуцествляется блоками 2 и 3 свертки по модулю два и схемой 4 поразрядного сравнений контрольных разрядов. При наличии однократной ошибки в информационном слове на выходе схемы 4 сравнения контрольных разрядов формируется единичный логический урОвень, который поступает через элемент ИИИ 15 на вход элемента И-НЕ , 16, где стробируется по его друго" му входу задержанным импульсом записи единичного уровня с выхода элемента 13 задержки. При совпадении единичных логических уровней на 55 входах элемента И-НЕ 16 на его выходе формируется нулевой логичес". кий уровень, под действием которого срабатывает триггер 12 сбоя, в результате чего блокируется прохождение данного импульса записи с выхода элемента 1 ч задержки через элемент И 18 на счетный вход двоичного счетчика 11 и блокируется прохождение лослед 7 юцих импульсов записи через элемент И 17, Дальнейший приеминформационных слов прекращается.в регистре 5 ошибки фиксируется информационное слово, содержащее однократную ошибку, код которого высвечивается блоком 20 индикации, а блоком 21 индикации высвечивается номер информационного слова, в котором обнаружена ошибка. Блоком 19 индикации при этом высвечивается код этого же информационного слова, но записанным приемным регистром на момент обнаружения однократной ошибки, Идентичность кодов в блоках 19 и 20 индикации указывает на достоверностьприема регйстром 5 ошибки информационного слова, содержащего однократную ошибку.Во втором случае производится контроль с целью обнаружения много" кратных ошибок, возникающих непосредственно при приеме приемным регистром. Контроль производится схемой 9 сравнения, с выхода которой при отрицательном результате сравнения формируется единичный логический уровень., который поступает через элемент 11 эй 15 на вход элемента Я-ЧЕ 16 где также стробируется по его другому входу задержанным импульсом записи. На выходе элемента И-НЕ 16 появляется нулевой логический уровень, лод действием которого срабатывает триггер 12 сбоя, Формируется сигнал "Сбой", который блокирует прохождение импульса записи на счетный вход двоичного счетчика 11 и прохождение последующих импульсов записи через элемент И 17, Дальнейший прием информационных слов прекращается, блоком 19 индикации высвечивается код информационного слова содержащего ошибку (ошибки) а блоком 21 индикации высвечивается номер информационного слова, соответствующий номеру приемного регистра, в котором зафиксирована ошибка (ошибки).:егистр 5 ошибки в данном случае выполняет функцию контрольного регистра, код информационного1 слова в котором принят без ошибок и высвечивается в блоке 20 ин"7 1051 дикации. Визуальное поразрядное сравнение информапионного кода в блоке 19 индикации, принятого приемным регистром с ошибкой, и контрольного информационного кода в блоке 20 индикации, принятого регистром 5,541 8позволяет оперативно локализовать местонахождение ошибок и принять ме. ры к их устранению.Применение изобретения позволяет повысить достоверность контроля принимаемой устройством информации,ставитель И. хоеп М.Кости яга о Е, Пап аказ 8667/4 а Проектная 8 Тираж 706 ВНИКНИ Государственного коми по делам изобретений и о 113035 Москва, Жа Раушс филиал ППП Патент , г. Ужгороддря шовКорректор ВПодписноета СССРытий .наб. д. 4/5

СмотретьЗаявка

3402541, 26.02.1982

ПРЕДПРИЯТИЕ ПЯ В-2969

ЧУКАВИН ГЕННАДИЙ ТИМОФЕЕВИЧ, КОНДРАТЬЕВ ВЛАДИМИР БОРИСОВИЧ

МПК / Метки

МПК: G06F 11/08

Метки: информации, локализации, обнаружения, ошибок, передаче

Опубликовано: 30.10.1983

Код ссылки

<a href="https://patents.su/5-1051541-ustrojjstvo-dlya-obnaruzheniya-i-lokalizacii-oshibok-pri-peredache-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для обнаружения и локализации ошибок при передаче информации</a>

Предыдущий патент: Устройство управления оперативной памятью

Следующий патент: Устройство для обработки изображений

Случайный патент: Способ подготовки порошкообразных образцов для нейтронно активационного анализа