Процессор микро-эвм

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

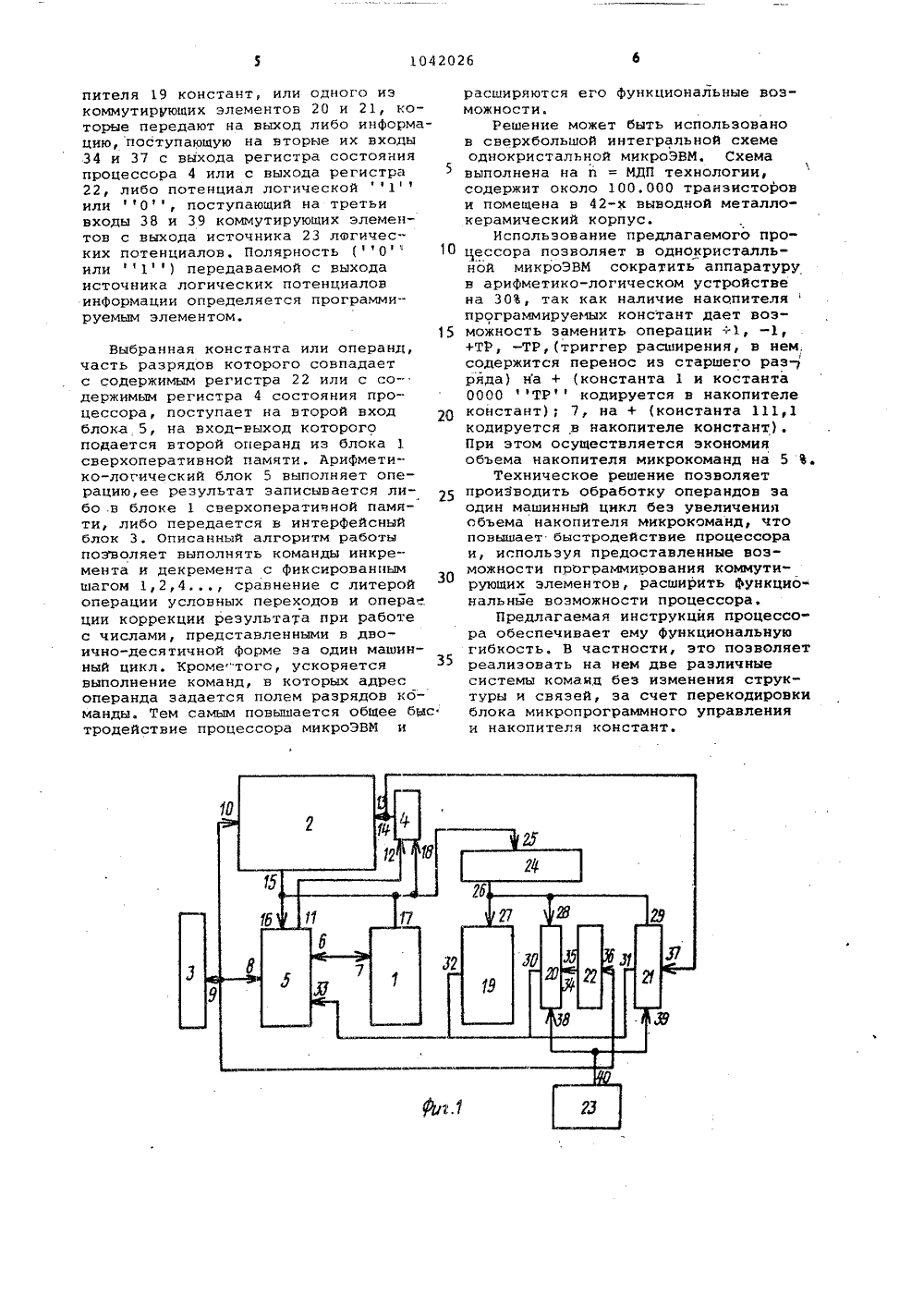

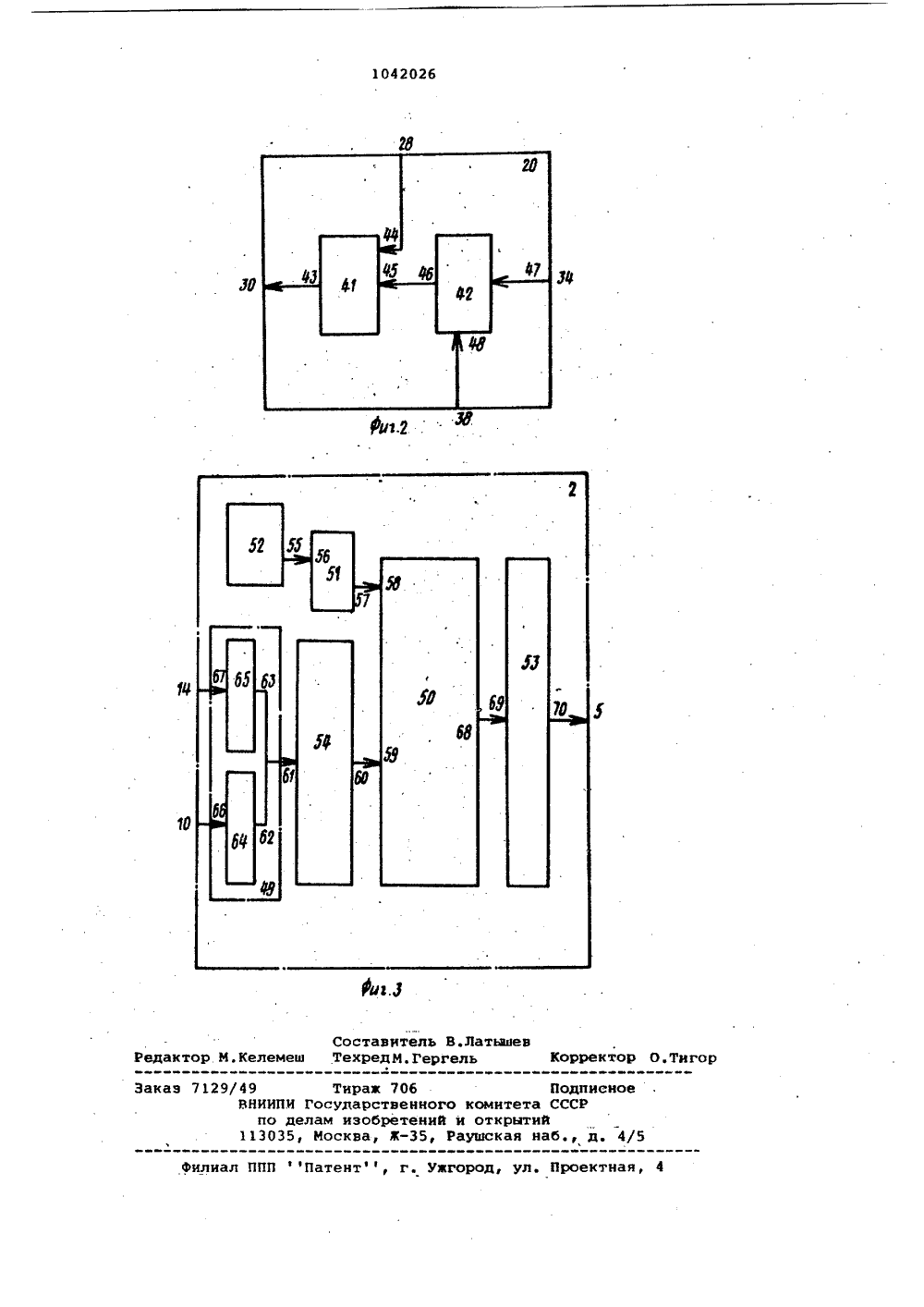

(5) 6 0 5 0 ОСУДАРСТВЕННЫЙ КОМИТЕТ ССПО ЕЛАМ ИЗОБРЕТЕНИЙ И ОТКРЬ Г СРА )ТИЙОПИСАНИЕ ИЗОБРЕТЕНИЯ : К АВТОРСКОМУ СВИДЕТЕЛЬСТВУь ко,(прототип),(54)(57) ПРОЦЕССОР МИКРОЭВМ, содержащий блок сверхоперативной памяти, блок микропрограммного управления, интерфейсный блок, регистрсостояния процессора и арифметикологический блок, причем первый входвыход арифметико-логического блокасоединен с входом-выходом блокасверхоперативной памяти, второйвход-выход - с входом-выходом интерФейсного блока и первым входом блокамикропрограммного управления, выходарифметико-логического блока соединенс первым входом регистра состоянияпроцессора, выход которой соединенсо вторым входом блока микропрограм,много управления, управляющий выходкоторого соединен с первым входом арифметико-логического блока, входом блока сверхоперативной памятии со вторым входом регистра состояния процессора, о т л и Ч а ю щ и йс я тем, что, с целью повышениябыстродействия и увеличения функциональных возможностей за счет реализации команд символьной обработкиданных на микропрограммном уровне,в него введены накопитель констант,первый и второй коммутирующие элементы, регистр, источник логических потенциалов и дешифратор, причемвход дешифратора соединен с управ- .ляющим выходом блока микропрограммного управления, а его выход соединен с входом накопителя константы с первыми входами первого и второго коммутирующих элементов, выходыкоторых, а также выход накопителяконстант соединены с вторым входомарифметико-логического блока, второйвход первого коммутирующего элементасоединен с выходом регистра, входкотррого соединен с входом-выходоминтерфейсного блока, второй входвторого коммутирующего элементасоединен с выходом регистра состояния процессора, а третьи входы первого и второго коммутирующих элементов соединены с выходом источника логических потенциалов.Изобретение относится к вычисли-тельйой технике и микроэлектроникев частности к процессорам микроЬВМ,область применения которых - устройства автоматики, устройства обработки цифровой информации, системыуправления, вычислительные машиныобщего назначения.Известен микропроцессор, содержащий блок сверхоперативной памяти,блок управления, арифметико-логическое устройство и интерфейсныйблок 11 .Однако отсутствие воэможностивыполнения алгоритмов символьнойобработки данных на микропрограммном уровне приводит к снижениюбыстродействия процессора.Наиболее близким к изобретениюявляется процессор микроЭВМ, содержащий микропрограммного упранления, блок обработки и интерфейсныйблок, Блок обработки содержит сверхоперативную память, арифметико-логическое устройство и регистр состояния процессора, причем первый 25вход-выход арифметико-логическогоустройства соединен с первым вхо"дом-выходом блока сверхоперативнойпамяти, второй нход-ныход - с входом-ныходом интерфейсного блока ивходом-выходом блока микропрограммного управления, управляющие входыблока сверхоперативной памяти, арифметико-логического устройства ирегистра состояния процессора соединены с входом-выходом блока микропрограммного управления, вход регистра состояния процессора подключенк выходу арифметико-логическогоустройства, выход - ко входу-выходублока микропрограммного управления 12, 40Выполнение команд процессороммикроЭВМ обычно связано с использованием заранее заданных константв качестве операндов, а также операндов, отдельные поля разрядов 45которых совпадают с полем разрядовкоманды или полем разрядов регистрасостояния процессора. С целью обеспечения .возможности выполнениятаких операций н известном процессоре 50микроЭВМ предусмотрены микрокомандыформата условных переходов и формата литеральных микрокоманд,В качестве одного из операндов в них используется поле разрядов ,25 микроманды. Такое решение приводит к существенному снижению быстродействия при расширении разрядности операндов, поскольку разрядность выделенного под операнд поля микро команды меньше разрядности операнда т.е. один операнд приходится обрабатывать за несколько машинных циклов. Увеличение разрядности микро" манды не снижает быстродействия, 65 однако приводит к существенномуувеличению накопителя микропрограмм.Цель изобретения - повышение быстродействия и увеличение функциональных возможностей за ечет реализации команд символьной обработки данных на микропрограммном уровне.Поставленная цель достигается тем, что н процессор микроЭВМ, содержащий блок сверхоперативной памяти, блок микропрограммного управления, интерфейсный блок, регистр состояния процессора и арифметико-логический блок, причем первый вход-выход арифметико-логического блока соединен с нходом-ныходом блока сверхоперативной памяти, второй вход-выход - с входом-выходом интерфейсного блока и первым входом блока микропрограммного управления, выход арифметико-логического блока соединен с первым входом регистра состояния процессора, выход которого соединен со нторым входом блока микропрограммного.управления управляющий выход которого соедйндн с первым входом арифметико-логического блока, входом блока сверхоперативной памяти .и со вторым входом регистра состояния процессора, введены накопитель констант, первый и второй коммутирующие элементы, регистр, источник логических потенциалов и дешифратор, причем вход дешифратора соединен с управляющим выходом блока микропрограммного управления, а его выход соединен со входом накопителя констант и с первыми входами первого и второго коммутирую. щих элементов, выходы которых, а также ныход накопителя констант соединены с вторым входом арифметикологического блока, второй вход первого коммутирующего элемента соединен с выходом регистра, вход которого соединен с входом-выходом интерфейсного блока, второй вход коммутирующего элемента соединен с выходом регистра состояния процессора, а третьи входы первого и второго коммутирующих элементов соединены с выходом источника логических потенциалов. При этом коммутирующий элемент содержит элемент И и програймируемый элемент, причем выход элемента И соединен с выходом коммутирующего элемента, первый вход схемы И соединен с первым нходом коммутирующего элемента, второй вход - с выходом программируемого элемента, первый вход которого соединен со вторым входом коммутирующего элемен-. та, второй вход программируемого элемента соединен с третьим входом коммутирующего элемента.На фиг. 1 представлен предлагаемый процессор микроЭВМ 1 на фиг. 2 коюутирующий элемент; на фиг. 3 ,блок микропрограммного управления.Процессор микроЭВМ включает блок 1 сверхоператйвной памяти, блок 2 микропрограммного управления, интерфейсный блок 3, регистр 4 состояния процессора и арифметико-логический блок 5, первый вход-выход б которого соединен с входом-выходом 7 блока 1 сверхоперативной памяти второй вход-выход 8 - с входом-выходом 9 интерфейсного блока 3 и первым входом 10 блока 2 микропрограммного управления, а выход 11 арифметико-логического блока 5 соединен с первым входом 12 регистра 4 состояния процессора, ныход 13 которого соединен с вторым входом (шина) 14 блока 2 микропрограммного управления, управляющий выход 15 которого соедийен с первым входом 16 арифметико-логического блока 5, входом 17 блока 1 сверхоперативной памяти и с вторым Входом 28 регистра соетояния процессора 4. Процессор микро ЭВМ дополнительно включает накопитель 19 констант, представляю" щий собой постоянное запоминающее устройство (ПЗУ); разрядность кото" рого соответствует разрядности арифметико-логического устройства 5.Первый 20 и второй 21 коммутирующие элементы, регистр 22, источник 23 логических потенциалов. (в процессоре соответствует шинам фпитанияф - источник логического потенциала ф 1 ф и фземли - источник логического потенциала 0) и дешифратор 24, вход 25 которого подключен к.управляющему выходу 15 блока 2 микропрограммного управления, а его выход 26 соединен со входом 27 накопителя 19 констант и с первыми входами 28 и 29 первого 20 и второго 21 коммутирующих элементов, выходы 30 и 31 которых и ныход 32 накопителя 19 констант соединены со вторым входом 33 арифметико-логического блока 5Второй вход 34 первого коммутирующего элемента 20 (Фиг. 2) соединен с выходом 35 регистра 22, вход 36 которого соединены с входом-выходом 9 интерфейсного блока 3, второй вход 37 второго коммутирующего элемента 21 соединен с выходом 13 регистра 4 состояния процессора, а третьи входы 38 и 39 первого 20 и второго 21 коммутирующих элементов соединены с выходом 40 источника 23 логических потенциалов.Коммутирующий элемент 20 включает элемент И 41 и программируемый элемент 42, который представляет собой коммутирующую перемычку н .схеме ипрограммируется н ходе технологического процесса с помощью маски, при-.чем, выход 43 элемента И 41 .соединенс выходом 30 коммутирующего элемента20, первый вход 44 элемента И 41 соединен йервым входом 28 коммутирующего.элемента 20; второй вход 45 - с выходом 46 программируемого элемента .42,первый вход 47 которого соединен со 1 О вторым входом 34 коммутирующегоэлемента 20, второй нход 48 программируемого элемента 42 соединен стретьим входом 38 коммутирующегоэлемента.15 Блок 2 микропрограммного управления (фиг. 3) включает группу регистрон 49, накопитель 50,микрокоманд,счетчик 51, генератор 52 тактовых.импульсов, регистр 53 микрокоманд,логический узел 54 Формированияначального адреса микропрограммы..Выход 55 генератора 52 тактовых импульсов 52 соединен со,входом 56счетчика 51,выход 57 счетчика 51 - спервым входом 58 накопителя 50 микрокоманд, второй вход 59 котореео соединен с выходом 60 логического узла54 формирования начального адресамикропрограммы, служащего для оптимизации объема накопителя микрокоманд,Впростейшем случае этот узел вырож. -дается в электрическую связь, вболее сложных случаях может бытьприменен кодератор, а в наиболеесложных случаях в качестве логики З 5 формирования начального адреса микропрограммы используется микропрограммный автомат, Вход 61 логическогоузла 54 формирования начального адреса микропрограммы подключен к выхо дам 62 и 63 регистров 64 и 65 группырегистров 49, которая состоит издвух регистров: регистра 64 командвход 66 которого соединен с многоканальной шиной 10, и регистра 65 45 состояния, вход которого 67 соединенс многоканальной шиной 14. Выход 68накопителя 50 микрокоманд соединенс входом 69 регистра 53 микрокоманд,выход 70 которого соединен с выходом15 блока 2Командадля исполнения поступаетиз интерфейсного блока 3 на входблока 2 микропрограммного управления и на вход регистра 22, где запоминается. Каждая команда, выйол-няемая процессором, интерпретируетсяблоком 2 микропрограммного управления в последовательность микрокомандкоторые содержат следующие поля:поле управления арифметико-логичес" 60 ким блоком, поле адреса операнда вблоке снерхоперативной памяти и полеразрядов микрокоманды, поступающеена вход дешифратора 24.Дешифратор 24 формирует сигнал 65 ,выборки или одной из констант нако 104202610 пителя 19 констант, или одного иэкоммутирующих элементов 20 и 21, которые передают на выход либо информацию, поступающую на вторые их входы34 и 37 с выхода регистра состоянияпроцессора 4 или с выхода регистра22, либо потенциал логической 1или 0, поступающий на третьивходы 38 и 39 коммутирующих элементов с выхода источника 23 лвгических потенциаловПолярность (0или 1) передаваемой с выходаисточника логических потенциаловинформации определяется программируемым элементом,Выбранная константа или операнд, часть разрядов которого совпадает с содержимым регистра 22 или с содержимым регистра 4 состояния процессора, поступает на второй вход блока 5, на вход-выход которого подается второй операнд иэ блока 1 сверхоперативной памяти. Арифметико-логический блок 5 выполняет операцию,ее результат записывается либо .в блоке 1 сверхоперативной памяти, либо передается н интерфейсный блок 3. Описанный алгоритм работы позволяет выполнять команды инкремента и декремента с фиксированным шагом 1,2,4, сравнение с литерой операции условных переходов и операе, ции коррекции результата при работе с числами, представленными н дноично-десятичной форме эа один машинный цикл. Кроме "того, ускоряется ныполнение команд, н которых адрес операнда задается полем разрядов команды. Тем самым повышается общее бИс тродействие процессора микроЭВМ и расширяются его функциональные воэможности,Решение может быть использованов сверхбольшой интегральной схемеоднокристальной микроЭВМ. Схеманыполнена на й = МДП технологии,содержит около 100,000 транзисторови помещена н 42-х выводной металлокерамический корпус.Использование предлагаемого процессора позволяет в однокристалльной микроЭВМ сократить аппаратурув арифметико-логическом устройствена 30, так как наличие накопителяпрограммируемых констант дает возможность заменить операции +1, -1,+ТР, -ТР,(триггер расширения, в нем,содержится перенос из старшего раэ-ряда) на + (константа 1 и костанта0000 ТР кодируется в накопителеконстант); 7, на + (константа 111,1кодируется в накопителе констант),При этом осуществляется экономияобъема накопителя микрокоманд на 5 .Техническое решение позволяетпроизводить обработку операндов заодин машинный цикл беэ увеличенияобъема накопителя микрокоманд, чтоповышает быстродействие процессораи, используя предоставленные возможности программирования коммутирующих элементов, расширить Функциональнйе возможности процессора,Предлагаемая инструкция процессора обеспечивает ему Функциональнуюгибкость, В частности, это позволяетреализовать на нем две различныесистемы команд без изменения структуры и связей, за счет перекодировкиблока микропрограммного управленияи накопителя констант.1042026 10 1 и. иго 7129/49 Тираа 706 Подписное ВНИИПИ Государственного комитета СССР по делам изобретений и открытий 113035, Москва, 3-35, Раушская наб., д. 4/Зак филиал ППП фПатент, г. Уагород, ул. Проектная,Составитель В.Латышеведактор М.Келемеш ТехредМ.Гергель Корректо

СмотретьЗаявка

2873846, 24.12.1979

ПРЕДПРИЯТИЕ ПЯ Р-6429

ДШХУНЯН ВАЛЕРИЙ ЛЕОНИДОВИЧ, КОВАЛЕНКО СЕРГЕЙ САВВИЧ, МАШЕВИЧ ПАВЕЛ РОМАНОВИЧ, ТЕЛЕНКОВ ВЯЧЕСЛАВ ВИКТОРОВИЧ, ЧИЧЕРИН ЮРИЙ ЕГОРОВИЧ

МПК / Метки

МПК: G06F 15/00

Опубликовано: 15.09.1983

Код ссылки

<a href="https://patents.su/5-1042026-processor-mikro-ehvm.html" target="_blank" rel="follow" title="База патентов СССР">Процессор микро-эвм</a>

Предыдущий патент: Устройство управления загрузкой микропрограмм

Следующий патент: Дифференцирующее устройство

Случайный патент: Контактная пара электрического соединителя