Устройство для дискретной регулировки фазы

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 1027639

Авторы: Рабкин, Филатченков

Текст

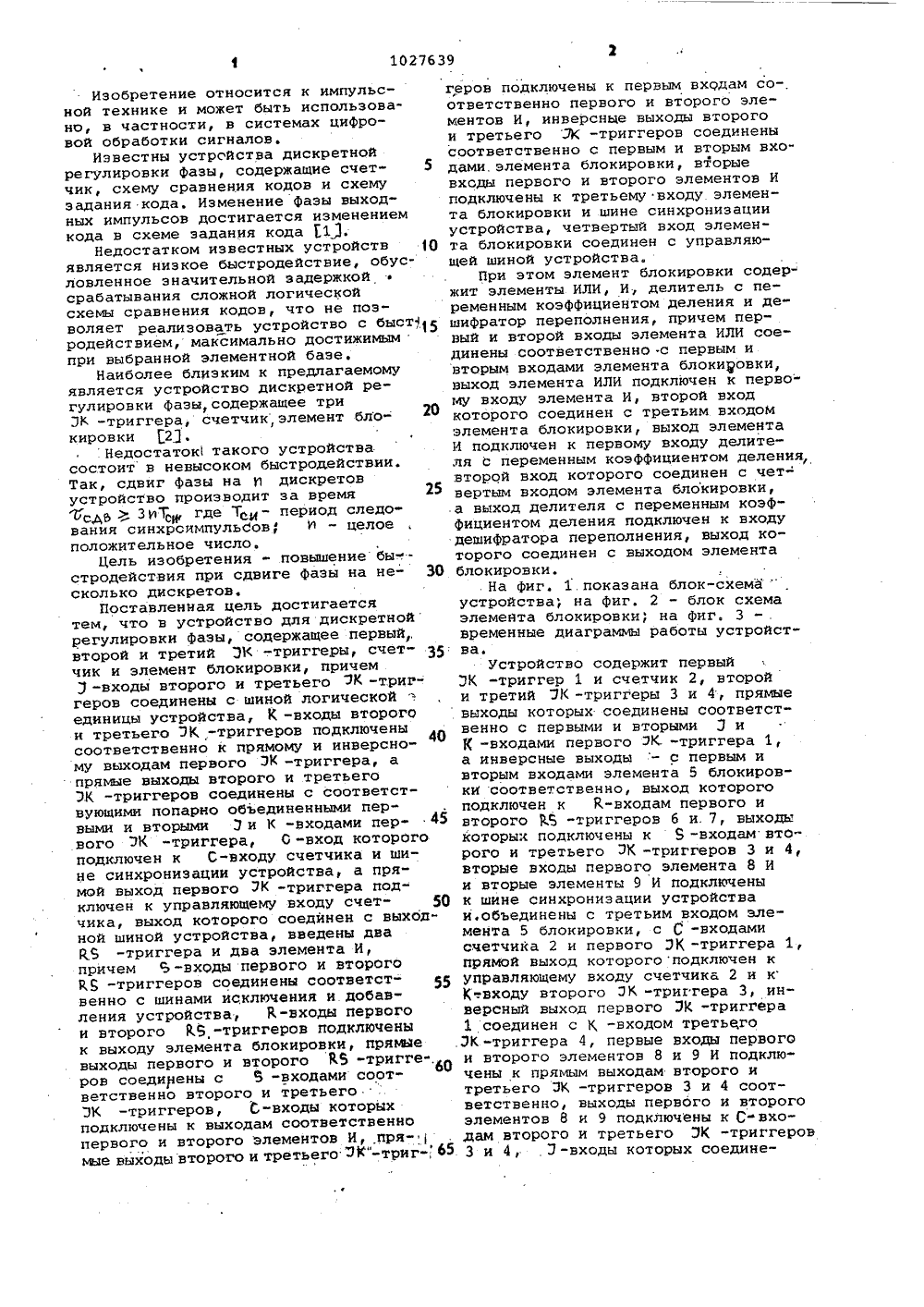

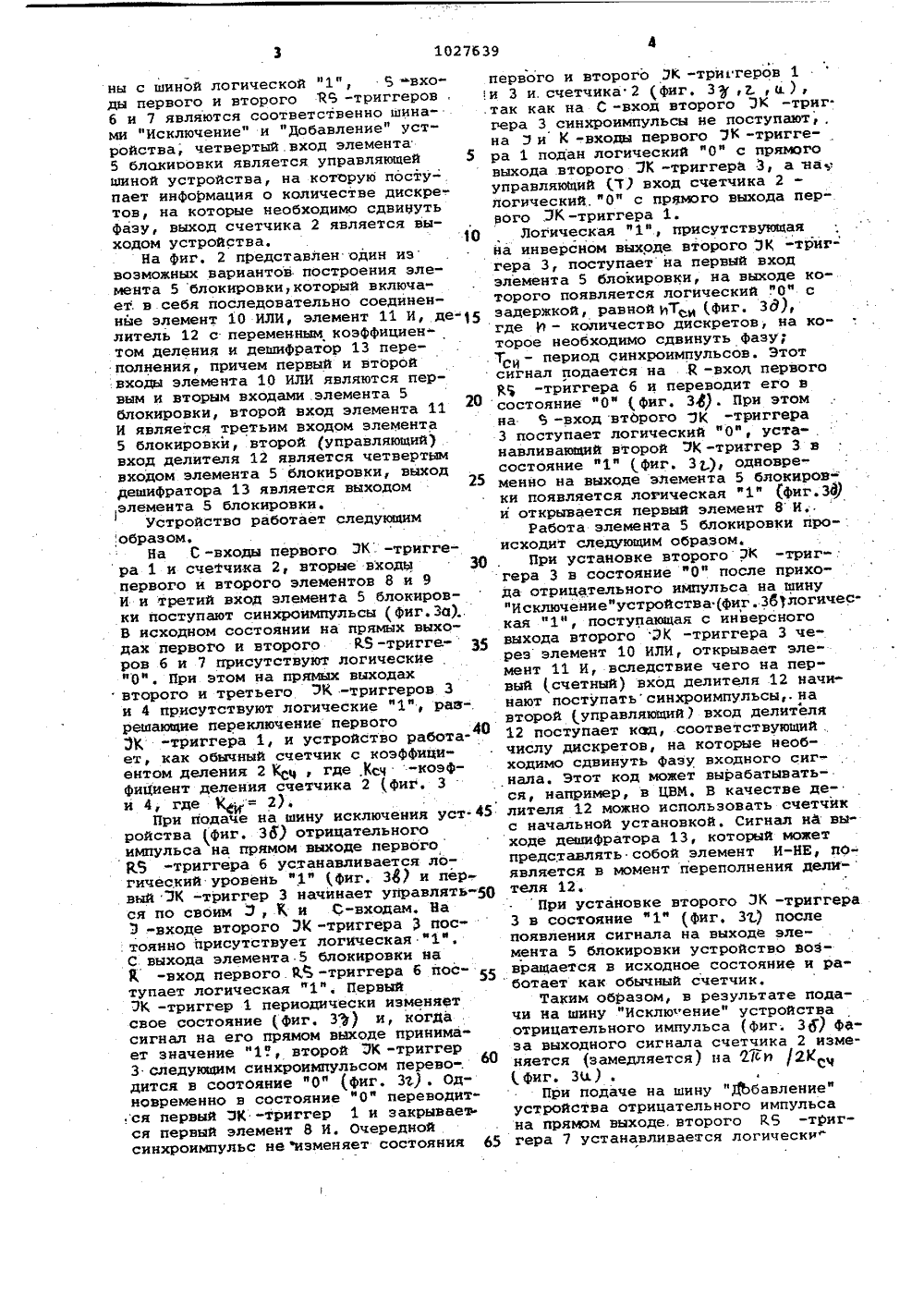

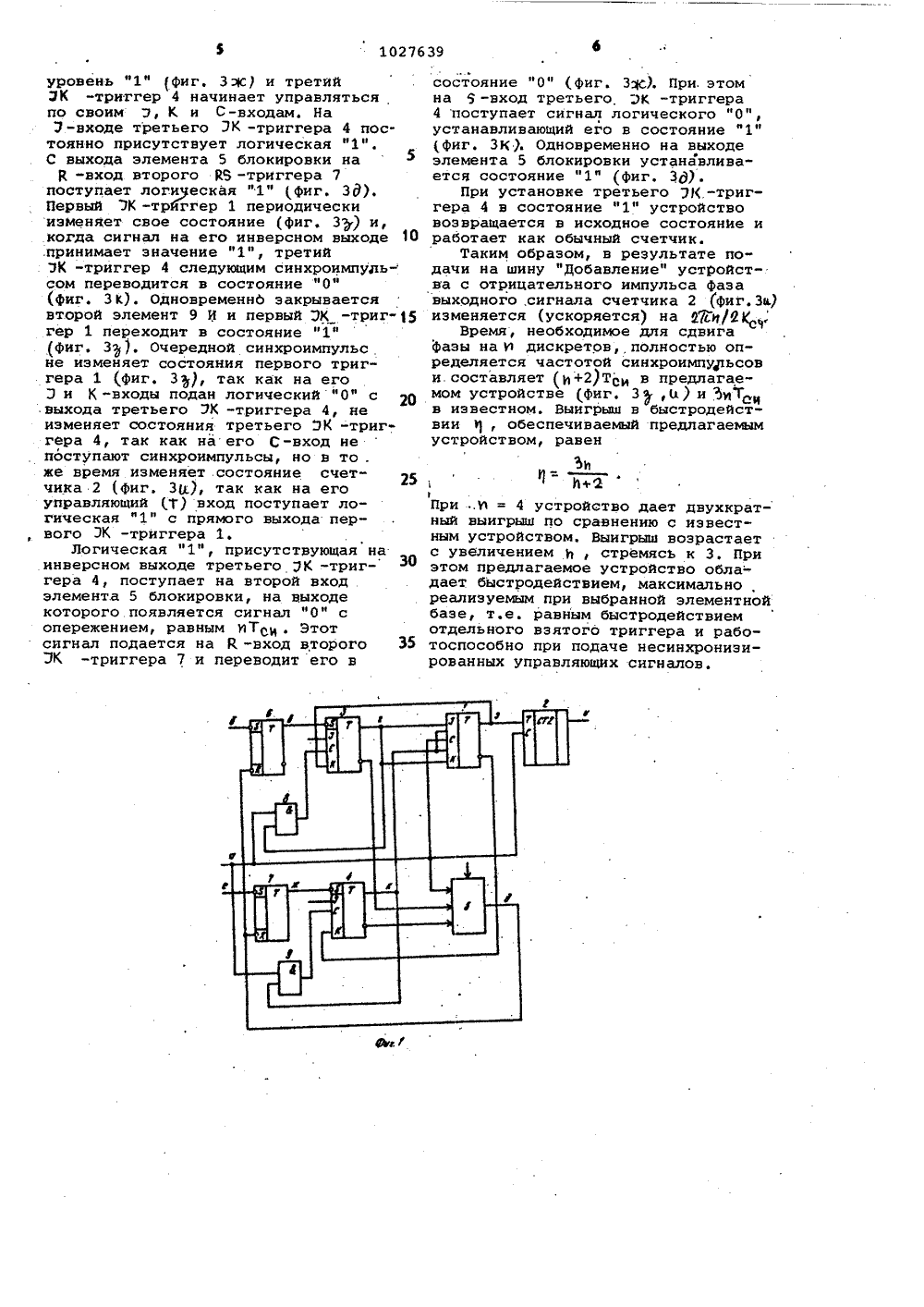

(Ю (И) . СОЮЗ СОВЕТСНИХСОЦИДЛИСТИЧЕСНИХРЕСПУБЛИК 9 С 01 К 25 0 Т СССРОПЮЫТЮ ПИСАНИ БРЕ СТВУа Н АВТОРв ч 8.8)свидетельство СССР3 К 5/153, 1976,видетельство СССР1 Й 25/00, 1981 о ГОСУДДРСТВЕННЫЙ НОМИТПО ДЕЛДМ ИЗОБ ЕТЕНИй 3 (54)(57) 1. УСТРОЙСТВО ДЛЯ ДИСКРЕТНОЙ РЕГУЛИРОВКИ ФАЗЫ, содержащее первый, второй.и третий -К -триггеры, счетчик и элемент блокировки, причем 3 -.входы второго и третьего 3 К -триггеров соединены с шиной ловической единицы устройства, Х -входы второго и третьего ЗК -триггеров подключены соответственно к прямому и инверсному выходам первого ЭК -триггера, а прямые выходы второго и третьего ЭК -триггеров соединены с соответствукщими попарно объединенными первыми и вторыми Э и К-входами первого, ЭК -триггера, С -вход которого подключен к С -входу счетчика и к шине синхронизации устройства, а прямой выход первого ЭК -триггера подключен к управляющему входу счетчика, выход которого соединен с выходной шиной устройства, о т л и" . ч а ю щ е е с я тем, что, с целью повышения быстродействия при сдвиге фазы на несколько дискретов, в него введены два И -триггера и два.элемента И, причем В -входы первого и второго Я 3-триггеров соединены соответственно с шинами исключения и добавления устройства, К -входы первого и второго К 6 -триггеров подключены к выходу элемента блокировки, прямые выходы первого и второго К 6 -триггеров соединены с 6 -входа" ми соответственно второго й .третьего ЭК -триггеров, С -входы которых подключены к выходам соответственно первого и второго элементов И,.прямые выходы второго и третьего М-триг геров подключены .к первым входам соответственно первого и второго эле" ментов И, инверсные выходы второго и третьего 3 Ктриггеров соединены соответственно с первым и вторым входами элемента блокировки, вторые входы.первого и второго элементов И подключены к третьему входу элемента блокировки и к шине синхронизацииустройства, червертый вход элемента блокировки соединен с управляющей шиной устройства,2, Устройствр по и. 1, о т л ич а ю щ е е с я тем, что элемент блокировки содержит элементы ИЛИ, д И, делитель с переменным коэффициен-том деления, дешифратор переполнения причем первый и второй входы элемента ИЛИ соединены соответственно с первым и вторым входами элемента блокировки, выход элемента ИЛИ п дключен к первому входу элемента И, второй вход которого соединен с тре- тьим входом элемента блокировки, вы- .ход элемента И подключен к первоиу входу делителя с переменным коэффкциен. том деления, второй вход которого соединен с четвертым входом элемента блокировки, а выход делителя с переменным коэффициентом деления подключен к,входу дешифратора переполнения, выход которого соединен с выходом элемента блокировки.Изобретение относится к импульсной технике и может быть использовано, в частности, в системах цифровой обработки сигналов.Известны устройства дискретнойрегулировки фазы, содержащие счетчик, схему сраннения кодов и схемузадания кода. Изменение фазы выходных импульсов достигается изменениемкода в схеме задания кода 1 ,Недостатком известных устройств 1 Оявляется низкое быстродействие, обусловленное значительной задержкойсрабатывания сложной логическойсхемы сравнения кодов, что не позволяет реализовать устройство с быст.5родействием, максимально достижимымпри выбранной элементной базе.Наиболее близким к предлагаемомуявляется устройство дискретной регулировки фазы, содержащее триЭК -триггера, счетчик, элемент бло"кировки 21.Недостаток 1 такого устройствасостоит в невысоком быстродействии,Так, сдвиг фазы на И дискретовустройство производит за времясдэ ) ЗиТИ, где Теи- период следования синхрсимпульбов; и - целоеположительное число,Цель изобретения - повышение бы .стродействия при сдвиге Фазы на несколько дискретов,Поставленная цель достигаетсятем, что в устройство для дискретнойрегулировки фазы, содержащее первыйвторой и третий Э 1( -триггеры, счет- З 5чик и элемент блокировки, причем7 -входы второго и третьего ЭК -триггеров соединены с шиной логической .единицы устройства, К -входы второгои третьего ЭК -триггеров подключенысоответственно к прямому и инверсному выходам первого ЭК -триггера, апрямые выходы второго и третьегоЭК -триггеров соединены с соответствующими попарно объединенными первыми и вторыми Э и К -входами перного 7 К -триггера, С -вход которогоподключен к С-входу счетчика и шине синхронизации устройства, а прямой выход первого ЭК -триггера подключен к управляющему входу счетчика, выход которого соединен с выходной шиной устройства, введены двай.6 -триггера и два элемента И,причем 6 -входы первого и второгоКь -триггеров соединены соотнетственно с шинами исключения и добавления устройства, К-входы первогои второго И -триггеров подключенык выходу элемента блокировки, прямйевыходы первого и второго К 5 -тригге-,ров соединены с В -входами соответственно второго и третьегоЭК -триггеров, С"входы которыхподключены к выходам соответственнопервого и второго элементов И, пря-мые выходы второго и третьего З 1"-триг-, 65 герон подключены к первым вхсдам соответственно первого и второго элементов И, инверснЫе выходы второго и третьего ЛС -триггеров соединены соответственно с первым и вторым входами. элемента блокировки, вторые входы первого и второго элементов И подключены к третьему входу элемента блокировки и шине синхронизации устройства, четвертый вход элемента блокировки соединен с управляющей шиной устройства.При этом элемент блокировки содержит элементы ИЛИ, И, делитель с переменным коэффициентом деления и дешифратор переполнения, причем первый и второй входы элемента ИЛИ соединены соответственно с первым и вторым входами элемента блокировки, выход элемента ИЛИ подключен к перво- му входу элемента И, второй вход которого соединен с третьим входом элемента блокировки, выход элемента И подключен к первому входу делителя с переменным коэффициентом деления, второй вход которого соединен с чет- вертым входом элемента блокировки, а выход делителя с переменным коэф" Фициентом деления подключен к входу дешифратора переполнения, выход которого соединен с выходом элемента блокировки.На фиг. 1 показана блок-схема " устройства; на фиг. 2 - блок схема элемента блокировки, на фиг, 3 - . временные диаграммы работы устройства.Устройство содержит первый ЭК -триггер 1 и счетчик 2, второй и третий ЭК -триггеры 3 и 4, прямые выходы которых соединены соответственно с первыми и вторыми 3 и К -входами первого ЭК- -триггера 1, а инверсные выходы :- с первым и вторым входами элемента 5 блокировки соответственно, выход которого подключен к К-входам первого и второго К 5 -триггеров б и. 7, выходы которых подключены к 5 -входам второго и третьего ЭК -триггеров 3 и 4, вторые входы первого элемента 8 И и вторые элементы 9 И подключены к шине синхронизации устройства и.объединены с третьим входом элемента 5 блокировки, с С -входами счетчика 2 и первого ЭК -триггера 1, прямой выход которого подключен к управляющему входу счетчика 2 и к К-.входу второго ЭК -триггера 3, инверсный выход первого ЭК -триггера 1 соединен с К -входом третьего ЭК -триггера 4, первые входы первого и второго элементон 8 и 9 И подключены к прямым выходам второго и третьего ЭК -триггеров 3 и 4 соответственно, выходы первого и второго элементов 8 и 9 подключены к С-входамвторого и третьего ЭК -триггеров 3 и 4, Э -входы которых соединей логической "1" 5 эхо" первого и второго ЭК -триггеров 1ды первого и второго Я 5 -триггеров , и 3 и.счетчика 2 (фиг, Зу,2 а ),б и 7 являются соответственно шина- .так как на С -вход второго ЗК -триг.ми "Исключение" и "Добавление" уст- гера 3 синхроимпульсы не поступаютро ства,йчетвертый. вход элемента на 3 и К -входы первого 7 К -тригге 5 блокировки является управляющей 5 ра 1 подан логический с ршиной устройства, на которую посту- выхода второго Э рыхо а второго ЭК -триггера 3, а на;пает информация о количестве дискре- управляющий Тдп авляющий Г 7.) вход счетчика 2тов, на которые необходимо сдвинуть логический. "0" с прямого выхода перфазу, выход счетчика 2 является вы- рого ,ЭК-триггера 1.ходом устройства, Щ Логическая "1, присутствующаяНа фиг, 2 представлен один из йа инверсном выходе второго 3 К -триг-возможных вариантов построения эле- гера 3, поступает на первый входмента 5 блокировки, который включа- , элемента 5 блокировки, на выходе коет. в себя последовательно соединен- торого появляется логический ". 0" с3ные элемент 10 ИЛИ, элемент 11 И, дезадержкой, равной ИТи (фиг. д),литель 12 с переменным коэффициен" где И - количество дискретов, на котом деления и дешифратор 13 пере- торсе необходимо сдвинуть фазу;полнения, причем первый и второй Тси - период синхроимпул ое ио синх импульсовЭтотвходы элемента 10 ИЛИ являются пер- сигнал подается на Я -вход первоговым и вторым входами .элемента 5 К -триггера б и переводит его вблокировки, второй вход элемента 11 состояние О ( фиг. 34). Пр эИ является третьим входом элемента на-вход втдрого ЭК -триггера5 блокировки, второй (управляющий) .3 поступает логический "0", уста-,вход делителя 12 является четвертым навливающий второй ЭК -триггер 3 ввходом элемента 5 блокировки, выход состояние "1" (фиг. 3), одновредешифратора 13 является выходом 25 менно на выходе элемента 5 блокиров=элемента 5 блокировки. ки появляется логическая 1 (фиг.Зд)Устройство работает следующим и открывается первый элемент 8 И,.Работа элемента 5 блокировки про-:.образом,На С -входы первого ЭК -тригге- исходит следующим образом.ра 1 и счетчика 2, вторые входы 30, При установке второго ЭК -триг-:первого и второго элементов 8 и 9 гера 3 в состояние О" после прихоИ и третий вход элемента 5 блокиров" да отрицательного импульса на шинуки поступают синхроимпульсы (фиг.За) "Исключение"устройства(фиг.ЗблогичесВ исходном состоянии на прямых выхо- кая 1", поступающая с инверсногодах первого и второго КВ -тригге- у выхода второго ЭК -триггера 3 черов б и 7 присутствуют логические рез элемент 10 ИЛИ, открывает элеО". При этом на пряьых выходах мент 11 И, вследствие чего на пер второго и третьего ЭК -триггеров 3 вый (счетный) вход делителя 12 начни 4 присутствуют логические "1, раз- нают поступатьсинхроимпульсы нап авляющий ) вход делителярешающие переключение первого . второй (управляющи ) вход д3 К - а 1 и устройство работа поступает кац, соответствующи-триггерат е необет, как обычный счетчик с коэффици- . числу дискретов, на которые неоентом деления 2 Кс , где Ксч -коэф- ходимо сдвинуть Фазу входного сигФициент деления счетчика 2 (фиг. 3 нала. Этот код мож рЧ фЭтот ко может вырабатыватьну исключения уст.45 лителя 12 можно использовать счетчикПри подаче на шину исключения уст.фиг, ЗЦ отрицательного с начальной установкой, Сигнал на выройства фиг, 1 о рто а 13 кото й можети мпульса на прямом выходе первого ходе дешифратора 13, к рыЯ 3 -триггера б устанавливается ло- представлять собой элемент И Е,е И-НЕ погический уровень 1 (фиг. 34) и пер- является в момент переполнения дели-вый 3 К -триггер 3 начинает управлятьтели 12ся по своим , К, и С-входам, На При установке второго ЭК -триггераЭ -входе второго ЭК -триггера 3 пос" 3 в состояние "1 (фиг. ЗЧ.) после:тоянно присутствует логическая 1, появления сигнала на выходе элеС выхода элемента 5 блокировки на мента 5 блокировки устройство возК -вход первого. Ю -триггера б пос вращается в исходное состояние и ратупает логическая 1. Первыйботает как обычный счетчик,ЭК -триггер 1 периодически изменяет Тахим образом, в результате подасвое состояние (Фиг. ЗЪ) и, когДа чи на шину "Исключ ение" устройствасигнал на его прямом выходе принима- отрицательного импульса (фнг. 34) Фает значение 1". второй З -триггер за выходного сигнала счетчика 2 изме У603 следующим синхроимпульсом перево-, няется (замедляется) на 2 си /2 Кдится в состояние О" (Фиг. Зг) . Од- (.Фиг. ЗО.) .новременно в состояние "О переводит При подаче на шину "ДЬбавление,ся первый ЭК -триггер 1 и закрывает устройства отрицательного импульсася первый элемент 8 И. Очередной на прямом выходе. второго К 5 -тригсинхроимпульс не изменяет состояния 65 гера 7 устанавливается логически 1027639уровень ф 1" (фиг. ЗэК) и третий РК "триггер 4 начинает управляться по своим э, К и С-входам. На Э -входе третьего ЭК -триггера 4 постоянно присутствует логическая "1", С выхода элемента 5 блокировки на К -вход второго Щ -триггера 7 поступает логическая ф 1" 1 фиг. Зд). Первый 3 К -трйггер 1 периодически изменяет свое состояние (фиг, 3) и, когда сигнал на его инверсном выходе 10 .принимает значение "1", третий ЭК -триггер 4 следующим синхроимпуль- сом переводится в состояние фОф (фиг. 3 К). Одновременнд закрывается второй элемент 9 И, и первый ЭК -триг гер 1 переходит в состояние "1 ф (Фиг. 3), Очередной синхроимпульс не изменяет состояния первого триггера 1 (фиг. 3), так как на его Э и К -входы подан логический фОф с выхода третьего ЭК -триггера 4 не20Р изменяет состояния третьего ЭК -триггера 4, так как на его С-вход не поступают синхроимпульсы, но в то . же время изменяет состояние счетчика 2 (Фиг. 30.), так как на его управляющий Т) вход поступает логическая "1" с прямого выхода первого ЭК -триггера 1.Логическая "1 ф, присутствующая на инверсном выходе третьего ЭК -триггера 4, поступает на второй вход элемента 5 блокировки, на выходе которого появляется сигнал фО" с опережением, равным ИТОИ . Этот сигнал подается на К -вход второго 35 ЭК -триггера 7 и переводит его в состояние "О" (фнг. Зс). При, этом на 5 -вход третьего Зк -триггера 4 поступает сигнал логического "О") устанавливающий его в состояние "1 ф Фиг. ЗК), Одновременно на выходе элемента 5 блокировки устанавлива" ется состояние "1" (фиг. ЗД).При установке третьего ЭК,-триггера 4 в состояние "1" устройство возвращается в исходное состояние и работает как обычный счетчик.Таким образом, в результате подачи на шину фДобавление" устройства с отрицательного импульса Фаза выходного, сигнала счетчика 2 (фиг.Зв) изменяется (ускоряется) на й(И/УКсВремя, необходимое для сдвига фазы на И дискретовполностью определяется частотой синхроимпупьсов и составляет (И+2)ТОи в предлагаемом устройстве (фиг. 3. Ь) и ЪИТП й в известном. Выигрыш в быстродействии И, обеспечиваемый предлагаемым устройством, равенЪиИ+2При И = 4 устройство дает двухкратный выигрыш по сравнению с известным устройством. Выигрыш возрастает с увеличением И , стремясь к 3. При этом предлагаемое устройство обла- дает быстродействием, максимально, реализуемым при выбранной элементной базе, т.е. равным быстродействием отдельного взятого триггера и работоспособно при подаче несинхронизированных управляющих сигналов.

СмотретьЗаявка

3411919, 24.03.1982

ПРЕДПРИЯТИЕ ПЯ В-2203

РАБКИН ВИКТОР САМУИЛОВИЧ, ФИЛАТЧЕНКОВ СЕРГЕЙ ВИКТОРОВИЧ

МПК / Метки

МПК: G01R 25/00

Метки: дискретной, регулировки, фазы

Опубликовано: 07.07.1983

Код ссылки

<a href="https://patents.su/5-1027639-ustrojjstvo-dlya-diskretnojj-regulirovki-fazy.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для дискретной регулировки фазы</a>

Предыдущий патент: Цифровой фазометр

Следующий патент: Калибратор фазы

Случайный патент: Механизм подачи