Устройство для вычисления обратной функции

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

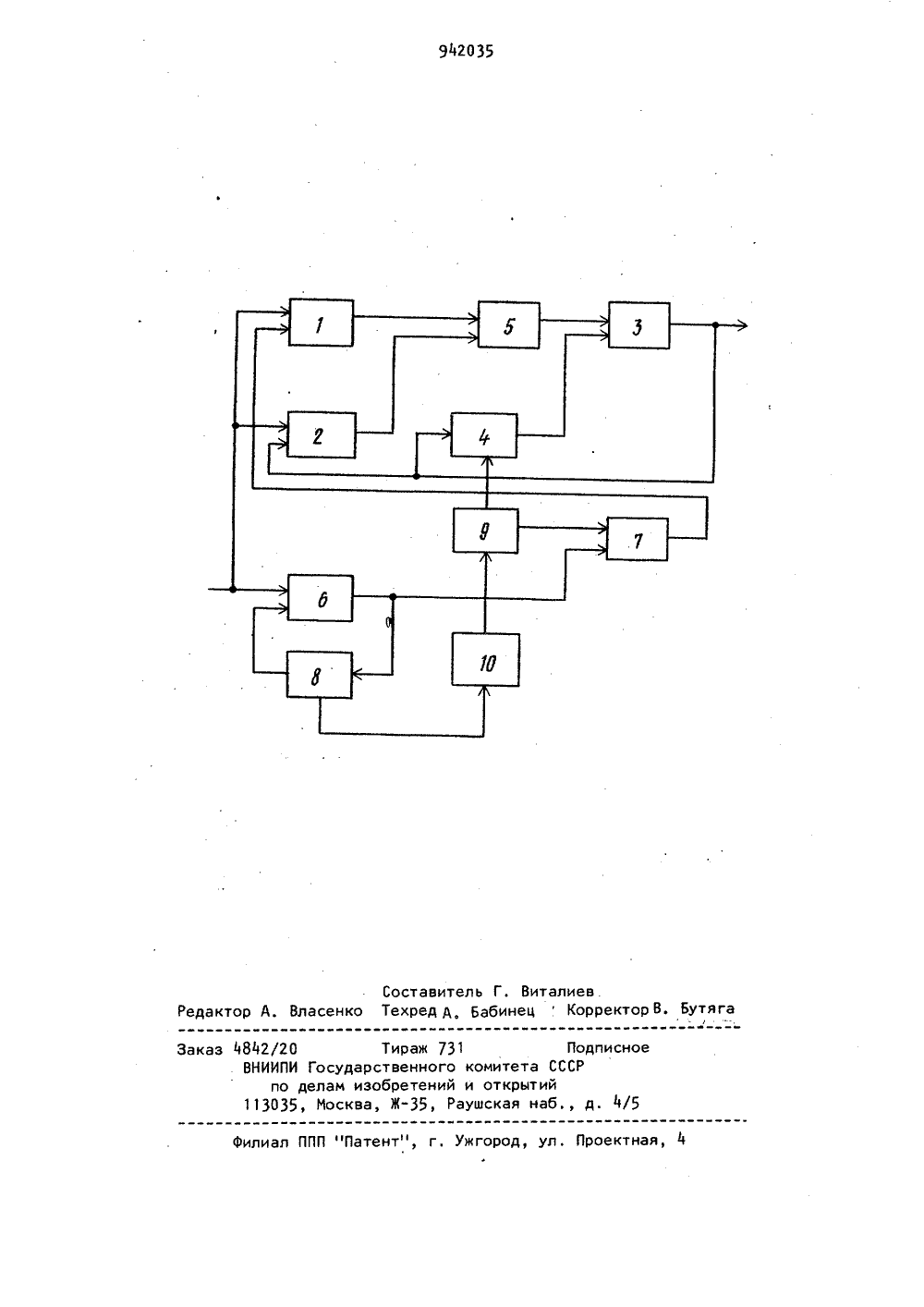

Союз Советски кСоциалистичесиикРеспублик ОП ИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ 1 ц 942035(6 ) Дополнительное к авт. свил-ву(22) Заявлено 19. 12. 80 (21) 3220523/18-24с присоединением заявки Рй -(5 )М. Кл. О 06 Р 15/328 Ьеудерстккииый комитет СССР ио аелеи изобретений и открытий3 Опубликовано 07, 07, 82, Бюллетень Ют 25 Дата опубликования описания 07.07,82(72) Авторы изобретения Таганрогский радиотехнический институт,., им, В.Д Калмыкова(54) УСТРОЙСТВО ДЛЯ ВЫЧИСЛЕНИЯ ОБРАТНОЙ ФУНКЦИИ15 2 о Изобретение относится к вычислительной технике и может быть использовано при построении специализированных вычислительных устройств,Известны вычислительные устройст 5 ва для воспроизведения обратных функций 1 и21.Недостатками известных устройств являются низкая скорость вычислений и значительные аппаратурные затраты,Наиболее близким по технической сущности к предлагаемому устройству является устройство, содержащее три цифровых интегратора, один из которых (третий) является следящим, причем первые входы первого и второго интеграторов соединены со входом устройства, выходы первого и второго интеграторов соединены соответственно с первым и вторым входами третьего интегратора, выход которого соединен со вторыми входами первого и второго интеграторов (,3. 21При вычислении Функции у = - дляхзнацений х, приближающихся к нулю,погрешность вычислений в указанномустройстве резко возрастает,Целью изобретения является повышение точности вычислений для значений х, близких к нулю.С этой целью в устройство длявычисления обратной Фучкции, содержащее первый, второй и третий интеграторы, причем вход устройства соединен с первыми входами первого и второго интеграторов, а выход третьегоинтегратора подключен ко второмувходу второго интегратора, введенычетвертый интегратор, первый, второйи третий сумматоры, регистр сдвига,регистр коррекции и коммутатор, приэтом первый и второй входы первогосумматора соединены с выходами соответственно первого и второго интегратора, а выход первого сумматораприсоединен к первому входу третьего,ральных функций интеграторов 1;2 и4 и в регистр 8 заносятся соответственно величины босо х 1 ух . Вычисление функции у =нацйнается в устройстве с момента подачи на вход устройства приращенийд. Приращения д поступают на первыевходы интеграторов 1 и 2 и сумматора6. Проходя через сумматор 6 и накапо ливаясь в регистре 8, приращения добразуют текущее значение переменнойх, которое поступает на вход коммутатора 10. В этом коммутаторе в зависимости от значений х производится - 15 формирование корректируЮщего множителя с, значение.которого записывается в регистр 9, Значение с.вырабатывается близким или равным х,лно кратное 2, так, чтобы х о . 2 о Например, если х = 0,126, то сс == 0,125 = 2 . Из регистра 9 значение о параллельным кодом передаетсяна второй вход интегратора 4, апоследовательным кодом - на входсумматора 7, где из него вычитаетсязначение х, поступающее из сумматора6, Образованная в сумматоре 7 разность сС- х поступает на второйвход интегратора 1 С выходов интег 30 35 4 О 45 50 3, 94интегратора, выход которого соединенс первым входом четвертого интегратора, а выход четвертого интегратора подключен ко второму входу третьего интегратора, первый и второйвходы второго сумматора соединенысоответственно со входом устройстваи первым выходом регистра сдвига,а выход второго сумматора подключенко входу регистра сдвига и первомувходу третьего сумматора, вход коммутатора соединен со вторым выходомрегистра сдвига, а выход - со входомрегистра коррекции, параллельный и:последовательный выходы которого подклюцены соответственно ко второмувходу четвертого интегратора и второму входу третьего сумматора, выход которого соединен со вторымвходом первого интегратора, причем,выход третьего интегратора являетсявь 1 ходом устройства.За счет введения новых блокови связей в предлагаемом устройствезначительно повышается устойчивостьи точность вычислений для значенийх, приближающихся к нулю,На цертеже приведена функциональная схема устройства.Устройство содержит первый, второй, третий и четвертый интеграторы .1 - 4 (интегратор 3 - следящий),первый, второй и третий сумматоры5 - 7, регистр 8 сдвига, регистр 9коррекции и коммутатор 10. Первыевходы интеграторов 1 и 2 соединенысо входом устройства, а выходысо входами сумматора 5, выход которого соединен с первым входом интегратора 3, выход интегратора 3 соединен с выходом устройства, вторымвходом интегратора 2 и первым входом интегратора 4, Первый вход сумматора б соединен со входом устройства, второй вход - с первым выходомрегистра 8, а выход - с первымвходом сумматора 7 и входом регистра8. Второй выход регистра 8 соединенсо входом коммутатора 10, выход которого соединен со входом регистра9, первый выход которого соединенсо вторым входом интегратора 4, авторой выход - со вторым входом сумматора 7. Выход сумматора 7 соединенсо вторым входом интегратора 1,Работа устройства заключаетсяв следующем,Перед началом выцислений навходы начальных значений подынтег 2035 4 ратора 1 и 2 на входы сумматора 5поступает приращение дх, умноженноесоответственно на величины оС - х и у.Полученная сумма ( о - х)дх.+ у. дх свыхода сумматора 5 поступает на первый вход следящего интегратора 3. Свыхода следящего интегратора снимается приращение ду,поступающее навторой вход интегратора 2 и на первый вход интегратора 4. С выхода интегратора 4 приращение ду, умноженное на величину с(., поступает на второй вход следящего интегратора 3.Предлагаемое устройство реализует дифференциальное уравнение ду = - 1(с- х)дх - удх(1)1Ф. при заданных начальных условиях, решением которого является функция1у =, ДифФеренциальному уравнению (1) соответствует разностное урав- нение у:(2 - - - ) у. + (-1+ - ).у, (2) Х 4 Ц х 144 ОС( о по которому ведутся вычисления вустройстве. Разностная схема (2)должна быт ь устой чи вой, т . еиметьрешение, сводящееся к решению дифференциального уравнения (1) приЬ. Устойчивость схемы (2) определяется следующим образом. Представим(2) в виде 5 где Если. оСх 1 и Ь-э О, то из 1,3) получаем Ц Кгауф" й С, где С = ехр(ф ф)А лМ = , х-а, Ь. Таким образом, из ограниченностиоператора Йследует устой чи вост ьи сходимость (2). За счет выборапараметра ол достигается ограниченность оператора В для всех х Е 1.а,Ь 1,в то время как в известном устрой- зестве С = 1 и ограниченность оператора имеет место не для всех значений х а, Ъ.Иетодическая погреш-.ность равна(4) Следовательно, введение параметра незначительно увеличивает объем оборудования, но позволяет вести вычис ления на всем интервале изменения переменной при заданной точности, так как вычислительная схема становится устойчивой и методическая погрешность Ь 0.15Предлагаемое устройство предназначено для использования в навигационных вычислителях, системах цифрово,го управления станками, в работах, микрокалькуляторах и другой радиоэлектронной аппаратуре. В = 2- --- -1+ -х 1 Ь Ъ 4с(В евклидовом пространстве имеем ьх Ьх 942035 6формула изобретенияУстройство для вычисления обрат-,ной Функции, содержащее первый, второй и третий интеграторы, причемвход устройства соединен с первымивходами первого и второго интеграторов, а выход третьего интегратора.подключен ко второму вхбду второгоинтегратора, о т л и ч а ю щ е е 19 с,я тем, что, с целью повышенияточности вычислений, оно содержит,четвертый интегратор, первый, второйи третий сумматоры, регистр сдвига,регистр коррекции и коммутатор, при1 этом первый и второй входы первогосумматора соединены с выходами соответственно первого и второго интег-ратора, а выход первого сумматораприсоединен к первому входу третьегоинтегратора, выход которого соединенс первым входом четвертого интегратора, а выход четвертого интегратора подключен ко второму входутретьего интегратора, первый и второй входы второго сумматора соединены соответственно со входом устройства и первым выходом регистра сдвига, а выход второго сумматора подключен ко входу регистра сдвига ипервому входу третьего сумматора,вход коммутатора соединен со вторымвыходом регистра сдвига, а выходсо входом регистра коррекции, параллельный и последовательный выходы3 которого подключены соответственноко второму входу четвертого интегра.тора и второму входу третьего сумматора, выход которого соединен совторым входом первого интегратора,причем выход третьего интегратораявляется выходом устройства,Источники информации,принятые во внимание при экспертизе1. Патент США й 3648038,кл. С 06 Г 7/39, 1971.2. Авторское свидетельство СССРИ 546881, кл. а 06 Г 7/38, 1977.3. Неслуховский К,С. ЦиФровыедифференциальные анализаторы, И.,942035 Составитель Г. Виталиев.Редактор А. Власенко Техред А, БабинецКорректор В. Бутягае а Ю сно д 4/ лиал ППП "Патент", г. Ужгород, ул. Проектная, 4Ф каз 4842/20 Тираж 73 ВНИИПИ Государственного по делам изобретений 113035, Москва, Ж, РПокомитета СССРи открытийущская наб.,

СмотретьЗаявка

3220523, 19.12.1980

ТАГАНРОГСКИЙ РАДИОТЕХНИЧЕСКИЙ ИНСТИТУТ ИМ. В. Д. КАЛМЫКОВА

ЛЕДОВСКОЙ МИХАИЛ ИВАНОВИЧ, АРСЕНИ ВЛАДИМИР ФЕДОРОВИЧ, СКАКУН АЛЕКСАНДР ВАСИЛЬЕВИЧ, АБРАМОВИЧ ВЛАДИМИР САМУИЛОВИЧ, РОМАНЕНКО РОМАН АЛЕКСЕЕВИЧ

МПК / Метки

МПК: G06F 17/13

Метки: вычисления, обратной, функции

Опубликовано: 07.07.1982

Код ссылки

<a href="https://patents.su/4-942035-ustrojjstvo-dlya-vychisleniya-obratnojj-funkcii.html" target="_blank" rel="follow" title="База патентов СССР">Устройство для вычисления обратной функции</a>

Предыдущий патент: Цифровой функциональный преобразователь

Следующий патент: Устройство для вычисления коэффициентов обобщенных функций хаара

Случайный патент: Устройство для определения коэффициентов внешнего и внутреннего трения сыпучих материалов