Система обработки информации

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 922712

Авторы: Кабалевский, Солохин, Степченков, Филин

Текст

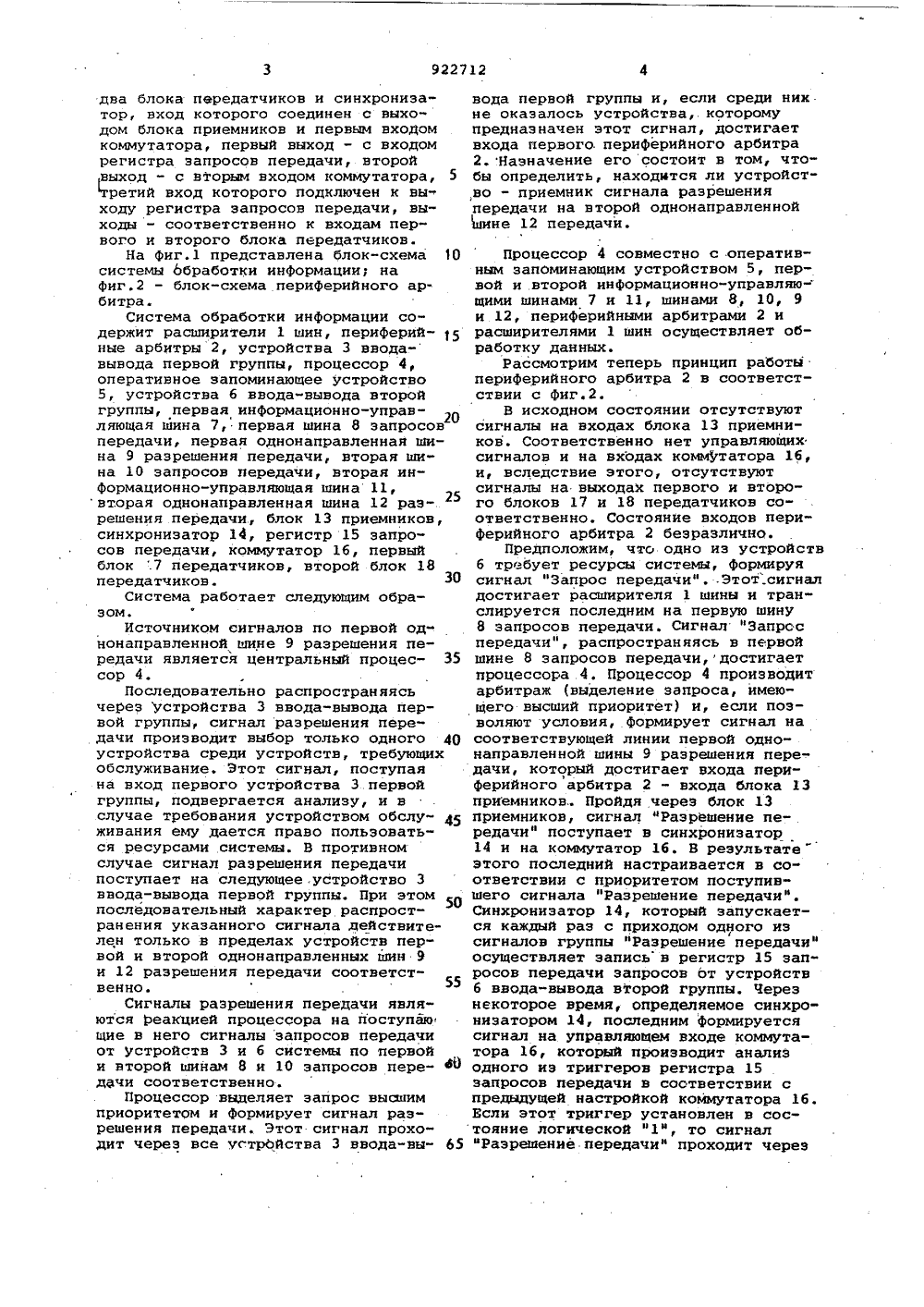

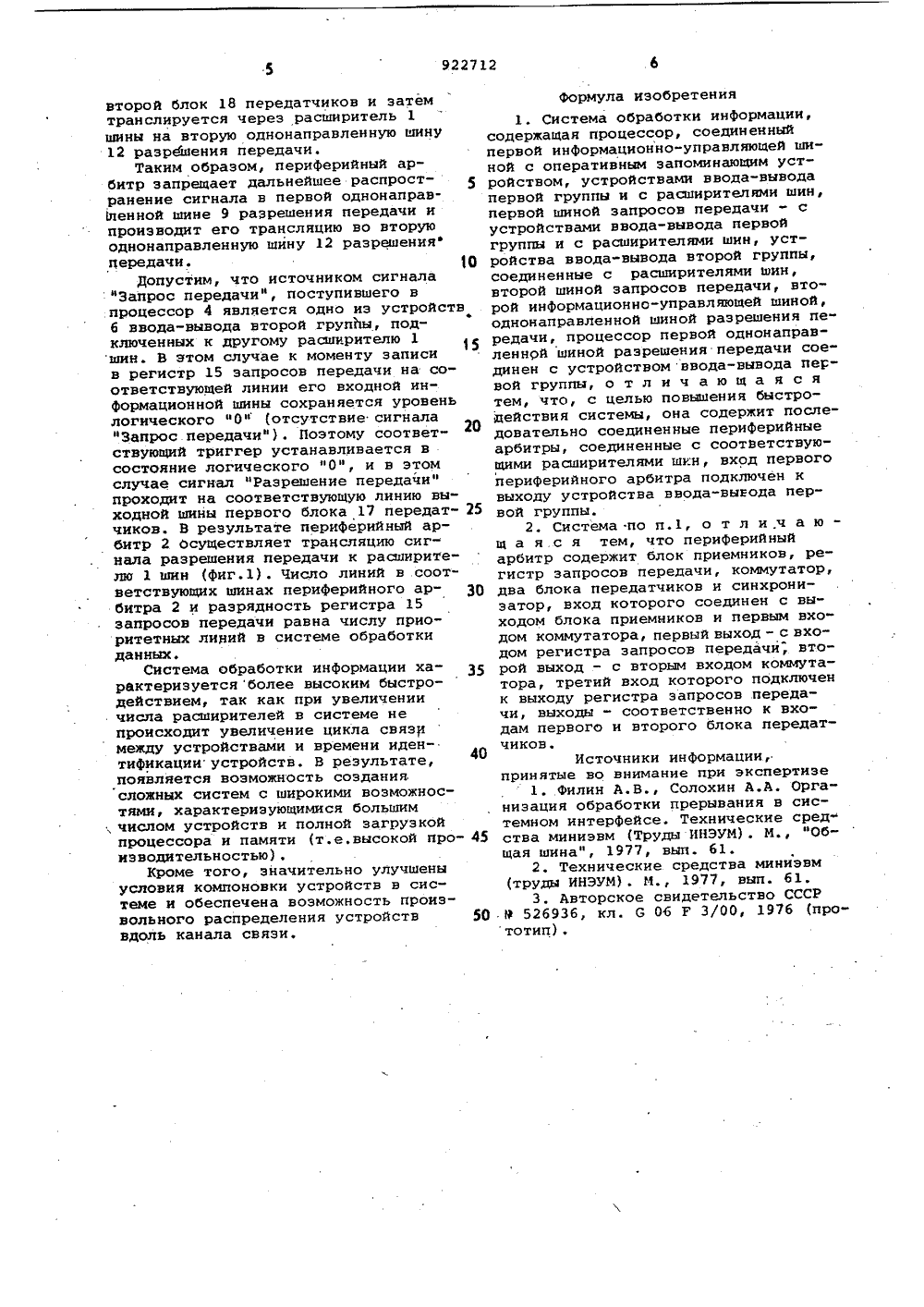

щ 922712 ОПИСАНИЕ ИЗОБРЕТЕНИЯ Своз СоветскикСоциалистическихРеспублик К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ(1)М Кп 3 с присоединением заявки Но 6 06 Р 3/04 Государственный комитет СССР по делам изобретений и открытий(23) Приоритет 1 3 УДК б 2-7 83,673(088.8) Опубликовано 230482 Бюллетень йо 15э Дата опубликования описания 230482(72) Авторыизобретения А,В.Филин, А.А.Солохин, Ю.А.Степченков и А.Н.Кабалевский ститут электронных управл витель шин(54) СИСТЕМА ОБРАБОТКИ ИНФОРМАЦИ вйода-выв ширителям вывода вт ысИзобретение относится к вычислительной технике, в частности,к сложным цифровым системам обработки информации (СОИ) со множеством устройств ввода"вывода.Создание эффективных СОИ приводит к увеличению числа устройств, под- ключаемых к системе. Однако неограниченно наращивать число устройств нельзя из-за ограниченных возможнос.- тей нагрузочной способности и геометрической длины канала связи, соединяющего устройства системы.Известна СОИ, содержащая процессор, магистральный канал связи, опе ративное запоминающее устройство, устройства ввода-вывода 11 и 121 .Недостатком этой системы является низкое быстродействие и невысокая нагрузочная способность канала связи.Наиболее .близким техническим решением к изобретению является система обработки информации,.содержащая процессор, соединенный первой инфор мационно-управляющей шиной с оперативным запоминающим устройством, устройствами ввода-вывода первой группы и с расширителями шин, первой шиной запросов передачи - с устройствами 30 ода первой группы и с раси шин, устройства вводаорой группы, соединенные с расширителями шин второй шиной запросов передачи, второй информационно-управляющей шиной и второй однонаправленной шиной разрешения пере дачи, процессор первой однонаправленной шиной разрешения передачи соединен с устройствами. ввода-вывода первой группыО 1.Недостатком такой системы является относительно низкое быстродействие при увеличении числа устройств в системе, обусловленное увеличением времени обмена между устройствами, расположенными на разных секциях канала связи.Цель изобретения - повышение б тродействия системы.Поставленная цель достигается тем, что система содержит последовательно соединенные периферийные арбитры, соединенные с соответствующиМи расширителями шин, вход первого периферийного арбитра подключен к выходу устройства ввода-вывода первой группы. Кроме того, периферийный арбитр содержит блок приемников, ре" гистр запросов передачи, коммутатор,10Процессор 4 совместно с оперативным запоминающим устройством 5, первой и второй инФормационно-управляю-щими шинами 7 и 11, шинами 8, 10, 9и 12, периферийными арбитрами 2 ирасширителями 1 шин осуществляет обработку данных.Рассмотрим теперь принцип работыпериферийного арбитра 2 в соответстствии с фиг.2,20В исходном состоянии отсутствуютсигналы на входах блока 13 приемников. Соответственно нет управляющихсигналов и на входах коммутатора 16,и, вследствие этого, отсутствуютсигналы на выходах первого и второго блоков 17 и 18 передатчиков соответственно. Состояние входов периферийного арбитра 2 безразлично.Предположим, что одно из устройствб требует ресурсы системы, Формируя30 сигнал "Запрос передачикЭтот".сигналдостигает расширителя 1 шины и транслируется последним на первую шину8 запросов передачиСигнал "Запроспередачи", распространяясь в первой35 шине 8 запросов передачи,достигаетпроцессора 4. Процессор 4 производитарбитраж (выделение запроса, имеющего высший приоритет) и, если позволяют условия, Формирует сигнал на40 соответствующей линии первой однонаправленной шины 9 разрешения передачи, который достигает входа пери"ферийного арбитра 2 - входа блока 13приемников Пройдя через блок 13приемников, сигнал фРаэрешение передачи" поступает в синхронизатор14 и на коммутатор 16. В результате "этого последний настраивается в соответствии с приоритетом поступившего сигнала "Разрешение передачи"Синхронизатор 14, который запускается каждый раэ с приходом одного изсигналов группы "Разрешение передачикосуществляет записьв регистр 15 зап"росов передачи запросов Ьт устройств6 ввода-вывода второй группы. Черезнекоторое время, определяемое синхронизатором 14, последним формируетсясигнал на управляющем входе коммутатора 16, который производит анализ40 одного из триггеров регистра 15запросов передачи в состветствии спредыдущей настройкой коммутатора 16.Бсли этот триггер установлен в состояние логической ф 1", то сигнал 65 два блока передатчиков и синхронизатор, вход которого соединен с выходом блока приемников и первым входомкоммутатора, первый выход - с входомрегистра запросов передачи, второйвыход - с вторым входом коммутатора, третий вход которого подключен к выходу регистра запросов передачи, выходы - соответственно к входам первого и второго блока передатчиков.На Фиг.1 представлена блок-схемасистемы 6 бработки информации; на фнг.2 - блок-схема периферийного арбитра.Система обработки информации содержит расширители 1 шин, периферийные арбитры 2, устройства 3 ввода- вывода первой группы, процессор 4, оперативное запоминающее устройство5, устройства б ввода"вывода второйгруппы, первая информационно-управляющая шина 7, первая шина 8 запросов передачи, первая однонаправленная шина 9 разрешения передачи, вторая шина 10 запросов передачи, вторая информационно-управляющая шина 11, вторая однонаправленная шина 12 разрешения передачи., блок 13 приемников, синхронизатор 14, регистр 15 запросов передачи, коммутатор 1 б, первый блок .7 передатчиков, второй блок 18 передатчиков.Система работает следующим образом.Источником сигналов по первой од" нонаправленной шине 9 разрешения передачи является центральный процессор 4.Последовательно распространяясь через устройства 3 ввода-вывода первой группы, сигнал разрешения передачи производит выбор только одного устройства среди устройств, требующих обслуживание. Этот сигнал, поступая на вход первого устройства 3 первой группы, подвергается анализу, и в случае требования устройством обслуживания ему дается право пользоваться ресурсами системы. В противном случае сигнал разрешения передачи поступает на следующее устройство 3 ввода-вывода первой группы. При этом последовательный характер распространения укаэанного сигнала действителен только в пределах устройств первой и второй однонаправленных шин 9 и 12 разрешения передачи соответственно.Сигналы разрешения передачи являются реакцией процессора на йоступаю щие в него сигналы запросов передачи от устройств 3 и б системы по первой и второй шинам 8 и 10 запросов передачи соответственно.Процессор выделяет запрос высшим приоритетом и формирует сигнал разрешения передачи. Этот сигнал проходит через все устройства 3 ввода-вывода первой группы и, если среди никне оказалось устройства,.которомупредназначен этот сигнал, достигаетвхода первого. периферийного арбитра2.Назначение его состоит в том, чтобы определить, находятся ли устройство - приемник сигнала разрешенияпередачи на второй однонаправленнойанне 12 передачи. фРаэрешение передачик проходит через35 второй блок 18 передатчиков и затем транслируется через расширитель 1 шины на вторую однонаправленную шину 12 разрйаения передачи.Таким образом, периферийный арбитр запрещает дальнейшее распространение сигнала в первой однонаправ(ленной шине 9 разрешения передачи и производит его трансляцию во вторую однонаправленную шину 12 раэрешенияф передачи, 0Допустим, что источником сигнала фЗапрос передачик, поступившего в процессор 4 является одно из устройств 6 ввода-вывода второй группы, подключенных к Другому Расширителю 1 шин. В этом случае к моменту записи в регистр 15 запросов передачи на соответствуюцей линии его входной ин-. формационной шины сохраняется уровень логического "Оф (отсутствие сигнала фЗапрос передачи"). Поэтому соответствующий триггер устанавливается в состояние логического "О", и в этом случае сигнал "Разрешение передачи" проходит на соответствуюцую линию выходной шины первого блока 17 передат чиков. В результате периферийный арбитр 2 Осуществляет трансляцию сиг" нала разрешения передачи к расширителю 1 шин (фиг.1). Число линий в соответствующих шинах периферийного ар- у) битра 2 и разрядность регистра 15 запросов передачи равна числу приоритетных линий в системе обработки данных.Система обработки информации характеризуется более высоким быстродействием, так как при увеличении числа расширителей в системе не происходит увеличение цикла связи между устройствами и времени идентификации устройств. В результате, появляется воэможность создания. сложных систем с широкими воэможностями, характеризующимися большим ,числом устройств и полной загрузкой процессора и памяти (т.е.высокой про изводительностью).Кроме того, значительно улучшены условия компоновки устройств в системе и обеспечена воэможность произвольного распределения устройств 50 вдоль канала связи. Формула изобретения1. Система обработки информации, содержащая процессор, соединенный первой информационно-управляюцей шиной с оперативным запоминаюцим устройством, устройствами ввода-вывода первой группы и с расширителями шин, первой шиной запросов передачи - с устройствами ввода-вывода первой группы и с расширителями шин, устройства ввода-вывода второй группы, соединенные с расширителями вин, второй шиной запросов передачи, второй информационно-управляющей шиной, однонаправленной шиной разрешения передачи, процессор первой однонаправленной виной разрешения передачи соединен с устройством ввода-вывода первой группы, о т л и ч а ю щ а я с я тем, что, с целью повышения быстродействия системы, она содержит после" довательно соединенные периферийные арбитры, соединенные с соответствующими расширителями шкн, вход первого периферийного арбитра подключен к выходу устройства ввода-вывода первой группы.2. Система.по п.1, о т л и.ч а ющ а я с я тем, что периферийный арбитр содержит блок приемников, регистр запросов передачи, коммутатор, два блока передатчиков и синхронизатор, вход которого соединен с выходом блока приемников и первым входом коммутатора, первый выход - с входом регистра запросов передачи, второй выход - с вторым входом коммутатора, третий вход которого подключен к выходу регистра запросов передачи, выходы - соответственно к входам первого и второго блока передатчиков.Источники информации, принятые во внимание при экспертизе1. Филин А.В., Солохин А.А. Организация обработки прерывания в системном интерфейсе. Технические сред" ства миниэвм (Труды ИНЭУМ)М., 1 Общая шина", 1977, вын. 61.2. Технические средства миниэвм (труды ИНЭУМ). М., 1977, вып. 61.3. Авторское свидетельство СССР Р 526936, кл. 0 06 Г 3/00, 1976 (прототип).

СмотретьЗаявка

2604988, 01.03.1978

ИНСТИТУТ ЭЛЕКТРОННЫХ УПРАВЛЯЮЩИХ МАШИН

ФИЛИН АДОЛЬФ ВАСИЛЬЕВИЧ, СОЛОХИН АЛЕКСАНДР АНДРЕЕВИЧ, СТЕПЧЕНКОВ ЮРИЙ АФАНАСЬЕВИЧ, КАБАЛЕВСКИЙ АЛЕКСАНДР НИКОЛАЕВИЧ

МПК / Метки

МПК: G06F 3/04

Метки: информации

Опубликовано: 23.04.1982

Код ссылки

<a href="https://patents.su/4-922712-sistema-obrabotki-informacii.html" target="_blank" rel="follow" title="База патентов СССР">Система обработки информации</a>

Предыдущий патент: Устройство для ввода информации

Следующий патент: Мультиплексный канал

Случайный патент: Многоклапанный ветряной двигатель с вертикальною осью