Параллельно-последовательный аналого-цифровой преобразователь

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

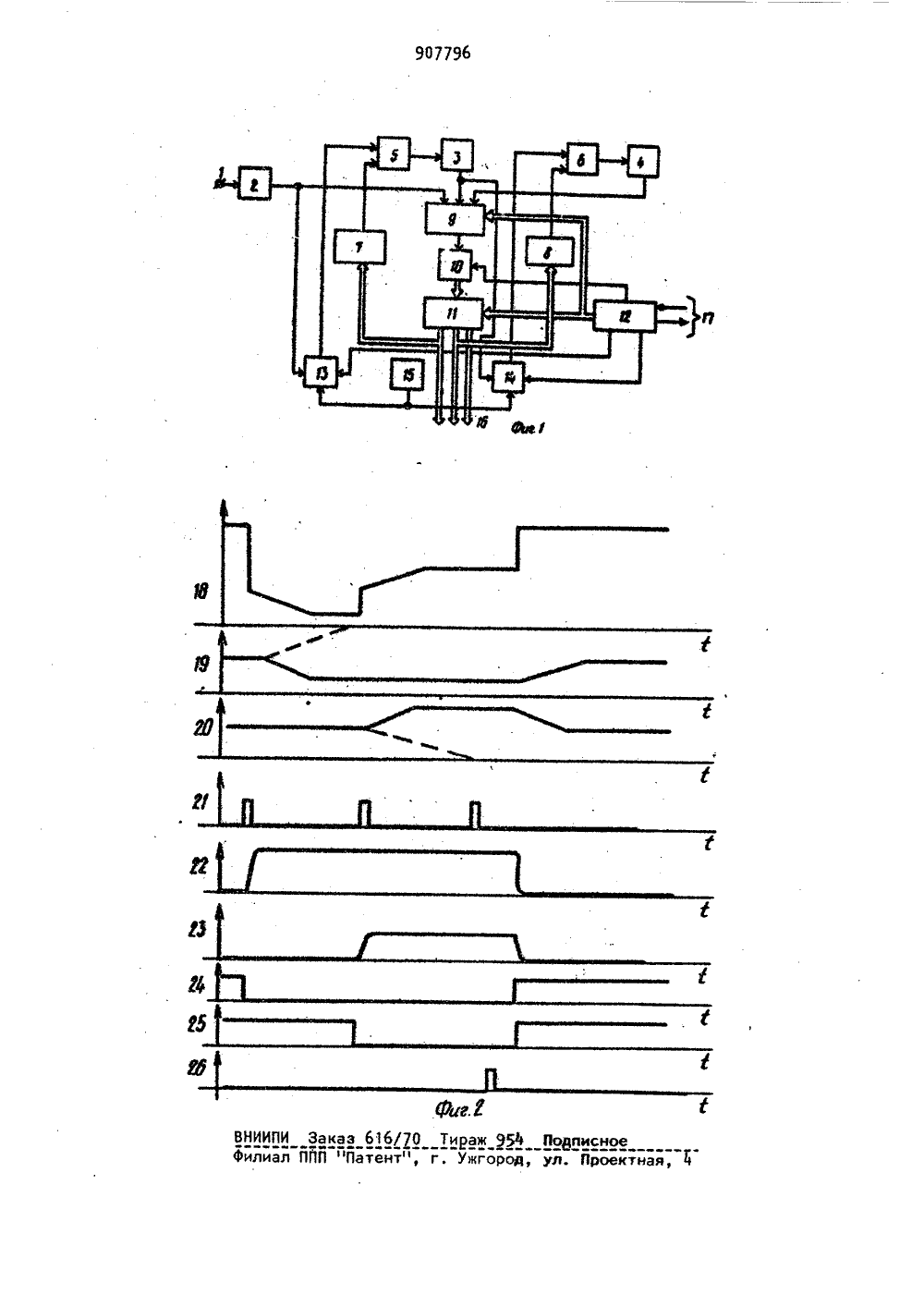

2) Автори нзобретеинн И. Лукьяно оителев чтут учно-исследовательский иномеханики) Занвнтель сесоюэны 54) ПАРАЛЛЕЛЬНО-ПОСЛЕДОВАТЕЛЬНЫЙ АНАЛОГО-ЦЙфРОВ 1:РЕОБРАЗОВАТЕЛЬ з последовательеобразователь,Изобретение относится к импульсн технике и используется при создании управляющих вычислительных комплекИ вестен параллельно-последовательный аналого"цифровой преобразователь, содержащий преобразователь параллельного считывания, регистр, первый и второй цифро-аналоговые преобразователи, коммутатор, первый и второй аналоговые сумматоры, первый, второй и третий усилители, блок управления и входную вину, при этом входная шина через первый усилитель соединена с первым входом коммутатора, второй и третий входы которого соединены соответственно через второй и третий усилители с выходами первого и второго аналоговых. сумматоров, выход коммутатора через преобразователь параллельного считывания соединен с первыми входами регистра, соединенного вторыми входами с первыми выходами блока уп" равления и с четвертыми входами коммутатора, первый и вторые выходы регистра соединены с входами соответ"ственно первого и второго цифро-аналоговых преобразователей ( ЦАП), выходы которых соединены с первыми вхо-,дами соответственно первого и второго аналоговых сумматоров, а второйвход преобразователя параллельногосчитывания соединен с вторым выходом0блока управления. Кроме этого, в немвыход первого усилителя соединен свторым входом первого аналогового сумматора, а выход второго усилителясоединен с вторым входом второго1 Заналогового сумматора 1 .Недостатком данного преобразователя является низкое быстродействие.Цель изобретения - повышениебыстродействия,Поставленная цель достигаетсятем, что в параллельноный аналого-цифровой прсодержащий входную шину, которая96 4 блока 12, выходные сигналы 22 и 23соответственно цифро-аналоговых преобразователей 7 и 8, сигналы 24 и25 на управляющих входах соответственно переключателей 13 и 14, выхбдной интерфейсный сигнал 26 блока 12,Преобразователь работает следующим образом.Преобразование начинается с приходом импульса по интерфейсному входу 17 по которому блок 12 вырабатывает сигналы на первых выходах, поступающие на четвертые входы коммутатора 9 и на вторые входы регистра 11.В результате коммутатор 9 подключает на вход преобразователя 1 О сигнал с выхода усилителя 2, обеспечивающего необходимую нагрузочную способность входному аналоговому сигналу, поступающему через входную шинуна вход этого усилителя. В регистре11 открываются входы старших разрядовдля приема параллельного кода с выходов преобразователя 10. После этогоблок 12 формирует первый импульс считывания 21, поступающий на второйвход преобразователя 10. Импульсныйкод, образованный на выходах последнего записывается в старшие разрядырегистра 11. Выходы этих разрядоввоздействуют на первый ЦАП 7, на выходе которого формируется сигнал 22,поступающий на первый вход сумматора 5, на второй вход которого начинает поступать сигнал с выхода усилителя 2 через переключатеЛь 13, таккак блок 12 изменяет сигнал 24 наего управляющем входе одновременнос появлением первого импульса считывания 21,Поскольку до этого переключения на входе усилителя 3 входной сигнал равен выходному сигналу источника 15, значение которого равно.йц 2 ф 1 (где И" максимально возможное значенйе выходного сигнала усилителя 3, равное максимальному значению выходного сигнала усилителя 2; К- число разрядов, получаемых в каждом такте преобразователя), а коэффициенты .усиления, усилителей 3 и 4 равны значению 2", то выходной сигнал 19 усилителя 3 равен половине его возможного максимального значения. Поэтому при переходе ко второму такту изменение сигнала на выходе усилителя 3 происходит в два раза быс 3 9077через первый усилитель соединена спервым входом коммутатора, второйи третий входы которого соединенысоответственно через второй и третий усилители с выходами первого ивторого аналоговых сумматоров, выход коммутатора через преобразователь параллельного считывания соединен с первыми входами регистра, вторые входы которого соединены с первыми выходами блока управления и счетвертыми входами коммутатора, первые и вторые выходы регистра соединены с входами соответственно первого и второго цифро-аналоговых пре.образователей, выходы которых соединены с первыми входами соответствен"1но первого и второго аналоговых сумматоров, второй вход преобразователяпараллельного считывания соединен свторым выходом блока управления, дополнительно введены источник напря"жения и два переключателя, причемвыход источника напряжения соединенс первыми входами переключателей,второй вход и выход первого переключателя соединены соответственно свыходом первого усилителя и с вторым входом первого аналогового сумматора, второй вход и выход второгопереключателя соединены соответст"венно с выходом второго усилителя ис вторым входом второго аналоговогосумматора, а третьи входы первогои второго переключателей соединенысоответственно с третьим и с четвертым выходами блока управления.На фиг. 1 приведена структурнаясхема предложенного устройства; нафиг. 2 " временные диаграммы работыосновных узлов устройства при вы"полнении аналого-цифрового преобра"зователя.Параллельно-последовательный аналого-цифровой преобразователь содер"жит входную шину 1,.усилители 2, 3и 4, аналоговые сумматоры 5 и 6, цифро-аналоговые преобразователи 7 и 8,коммутатор 9, преобразователь параллельного считывания 10, регистр 11,блок управления 12, переключатели о13 и 14, источник напряжения 15, выходные шины результирующего кода 16и интерфейсные вход и выход 17,На фиг. 2 обозначены сигнал 18на выходе коммутатора 9, сигналы 19и 20 на выходах соответственно усилителей 3 и 4, импульсы 21 считывания, Формируемые на втором выходеЪ907796 5трее, так как оно определяется половиной диапазона изменения входного сигнала. Время изменения определяется пунктирными линиями, обозначенными на диаграмме сигнала 19. 5После выполнения первого считыва"ния блок 12 изменяет сигналы на первых выходах гак, что коммутатор 9на вход преобразователя 1 О подключает выход усилителя 3, а также открывает для приема средние разрядырегистра 11. Через время, определяемое максимально возможным изменением выходного сигнала усилителя3, блок 12 формирует второй импульс 15считывания 21, и код с выходов преобразователя 10 записывается в средние разряды регистра 11.В результате этого начинает изменяться сигнал 23 на выходе вто- горого ЦАП 8.После второго считывания блок 12снова изменяет сигналы на первыхсвоих выходах, а также на управляющем входе переключателя 14. В регистре, 11 открываются входы младшихразрядов, коммутатор подключает навход преобразователя 10 выход усилителя 4, а переключатель 14 подаетна второй вход выходной сигнал уси влителя 3. После этого начинает изменяться сигнал 20 на выходе усилителя4.Максимально возможное изменениесигнала на выходе.Через время, определяемое максимально возможным изменением сигналана выходе усилителя 3 ( пунктирныелинии на диаграмме сигнала 20 1,блок 12 формирует третий импульс считывдниЯ 21, по котОРОму пРОиЗВОДится 4 взапись кода в младшие разряды регистра 11. На этом процесс преобразования заканчивается, а блок 12 вырабатывает выходной интерфейсный сигнал26, по которому можно снимать кодрезультата преобразования с выходов16 всех разрядов регистра 11.После того, как код результатасчитан с выходов регистра 11, блок12 устанавливает в исходное состояние разряды регистра 11, изменяетуправляющие сигналы 24 и 25 на управляющих входах переключателей 13и 14, а также изменяет сигналы насвоих первых выходах, подключая ко55входу преобразователя 10 выход усилителя 3, чем подготовляется очеоедное преобразование,6Таким образом, введение новых элементов и их взаимосвязей позволяет в два раза сократить время изменения сигнала йа выходе усИлителей 3 и 4, чем существенно повышается быстродействие преобразования,Формула изобретения Параллельно-последовательный аналого-цифровой преобразователь, содержащий входную шину, которая через первый усилитель соединена с первым входом коммутатора, второй и третий входы которого соединены соответственно через второй и третий усилители с выходами первого и второго аналоговых сумматоров, а выход коммутатора через преобразователь параллельного считывания соединен с первыми входами регистра, вторые входы которого соединены с первыми выходами блока управления и с четвертыми входами коммутатора, первые и вторые выходы регистра соединены с входами соответственно первого и второго цифро-аналоговых преобразователей, выходы которых соединены с первыми входами соответственно первого и второго аналоговых сумматоров, второй вход преобразователя параллельного считывания соединен с вторым выходом блока управления, о т л и ч а ю щ и й с я тем, что, с целью повышения быстродействия, в него введены источник напряжения и два переключателя, причем выход источника напряжения соединен с первыми входами переключателей, второй вход и выход первого переключателя соединены соответственно с выходом первого усилителя и с вторым входом первого аналогового сумматора, второй вход и выход второго переключателя соединены соответственно с вы" ходом второго усилителя и с вторым входом второго аналогового сумматора, а третьи входы первого и второго переключателей соединены соответственно с третьим и с четвертым выходами блока управления. Источники информации,принятые во внимание при экспертизе1.нЕЕЕ 1 пйегпас 1 опа 1 Сопчепй 1 опкееогд" 1966, ч.14, й 3, р. 39-43,119. 2 (прототип).

СмотретьЗаявка

2947993, 30.06.1980

ВСЕСОЮЗНЫЙ НАУЧНО-ИССЛЕДОВАТЕЛЬСКИЙ ИНСТИТУТ ЭЛЕКТРОМЕХАНИКИ

ВОИТЕЛЕВ АЛЕКСАНДР ИЛЬИЧ, ЛУКЬЯНОВ ЛЕВ МИХАЙЛОВИЧ

МПК / Метки

МПК: H03K 13/03

Метки: аналого-цифровой, параллельно-последовательный

Опубликовано: 23.02.1982

Код ссылки

<a href="https://patents.su/4-907796-parallelno-posledovatelnyjj-analogo-cifrovojj-preobrazovatel.html" target="_blank" rel="follow" title="База патентов СССР">Параллельно-последовательный аналого-цифровой преобразователь</a>

Предыдущий патент: Следящий аналого-цифровой преобразователь

Следующий патент: Преобразователь частоты в напряжение

Случайный патент: Способ получения производных нортропанола или их солей