Демодулятор сигналов с фазоразностной модуляцией

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

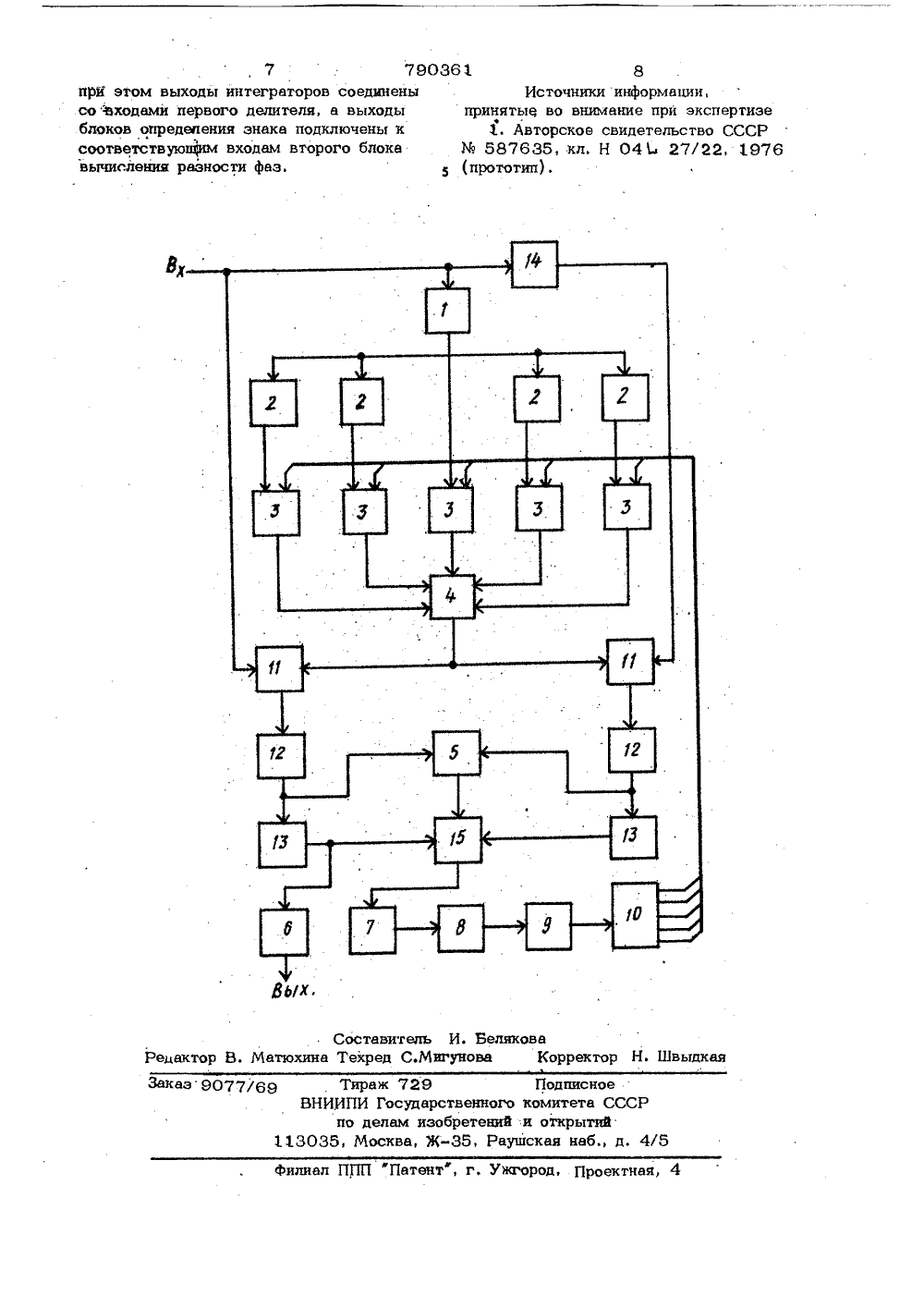

ОПИСАНИЕИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз СоветскихСоциалистическихРеспубпиии 790361(53)М. Кд. Н 04. 27/22 Веударстееиимй комитет СССР ао делам изобретений и открытий(53) УДК 621 .394.3.42(088.8) Дата опубликования описания 25.12.80 13Изобретение относится к технике радиосвязи, в частности к демодуляторам сигналов с фазоразностной. модуляцией (ФРМ), и может быть использовано в каналах связи с неопределенной частотой и фазой.5Для повышения помехоустойчивости демодуляторов ФРМ в условиях неста-. бильной несущей частоты применяют автоматическую подстройку частоты и10 фазы применяемого сигнала при использовании ФРМ первого порядка, либо 1 принцип многоканального построения демодуляторов ФРМ второго порядка с автоматическим выбором канала, в хотором паразитный фазовый набег имеет нви 15 , меньшее значение.Известен демодулятор сигналов с 1 ФРМ, который содержит блок автовыбора каналов, общий элемент ИЛИ, после-. довательно соединенные ограничитель и элемент задержки, каждый канал состоит нз последовательно соединенных элемента ИЛИ, фазового детектора, фильъ 2.рв нижних частот, регенератора; блока вычисления разностей фаз и ключа, а также порогового блока, двух дополни- .тельных ключей и фазоврвщателей, . входы которых подключены к выходу элемента задержки, при этом выход фильт-, ра нижних частот подхлючен ко входу порогового блоха, выходы которого подключены к управляющим входам дополнительных ключей, выходы которых соединены со входами элемента ИЛИ, инрормационные входы дополнительных ключей всех каналов, кроме первого, соединены с выходами соответствующих фазоврвщвтелей, а входы дополнительных ключей первого канала соединены соответственно с выходом элемента задержки и выходом фазоврвщателя, выход ограничителя подключен ко вторым входам фазовых детекторов каждого из каналов, выходы фильтров нижних частот каждого из каналов соединены со входами блока автовыбора каналов, выходы которого подключены х управляющим входам соот790361 3ветствуюших ключей и ко входу общего элемента ИЛИ, выходы ключей всех каналов соединены с остальными входами общего элемента ИЛИ 1.Однако практическая реализация демодулятора при большом числе каналов (более трех) нецелесообразна нз-за усложнения схемы, так как пропорционально числу кеналов возрастает элементный объем, снижается надежность работы и увеличивается потребляемая мощность.Цель изобретения - повышение помехо устойчивости при автокорреляционном приеме.Для этого демодулятор сигналов с ФРМ содержит элемент задержки, выход которого подключен ко входам фазовращателей, выходы которых соединены с первыми входами соответствующих ключей, выходы которых подключены ко входам элемента ИЛИ, выход которого соединен с первыми входами перемножителей, выходы которых через интеграторы подключены ко входам блоков определения знака, при этом второй вход одного перемножителя соединен со входом элемента задержки и со входом соответствующего фазовращателя,. выход которого подключен ко второму входу другого пере- множителя, а выход элемента задержки соединен с первым входом соответствующего ключа, выход которого подключен к соответствующему входу элемента ИЛИ, причем выход соответствующего блока определения знака соединен со входом первого блока вычисления разности фаз, последовательно соединенные первый делитель, второй блок вычисления разности фаэ, первый накапливающий сумматор, второй делитель, второй накапливаю. ший сумматор и дешифратор, выходы которого подключены ко вторым входам ключей, при этом выходы интеграторов соединены со входами первого делителя, а выходы блоков определения знака подключены к соответствующим входам вто рого блока вычисления разности фаэ. На чертеже представлена структурная электрическая схема демодулятора.Демодулятор содержит элемент задержки 1, фаэоврашатели 2, ключ 3, элемент ИЛИ 4, первый делитель 5, пер.вый блок 6 вычисления разности фаэ, первый накапливающий сумматор 7, втв рой делитель 8, второй накапливающий сумматор 9, дешифратор 10, перемножители 11, интеграторы 1.2, блоки 13 опре.деления знака, фазоврашатель 14, второй блок 15 вычисления разности фаз. 4Если на перемножитель, последовательно с которым включен интеграторподать два фазоманипулированных сигнала,один из которых задержан на время, равное длительности посылки, то напряжениена выходе интегратора пропорциональнокосинусу разности фаз между сигналамидвух соседних посылок соьъР, Включение двух каналов, синфаэного и квадратурного, позволяет вычислить напряжения, пропорциональные соВдР для синфазного канала и ьн дР для квадратурного канала. По значениюЬп ьФ- дФф ЮР,соЬ дР с учетом знаков в обоих каналах, можновосстановить значение разности фаэ ЬР .Иэ-за нестабильности несущей частотык переданному значению,рдо 0 20бавляется паразитный набег по фазе, равный дР,с,рдьоТ, который приводит кснижению помехоустойчивости. Таким образом, (Р 1 25 гарцем, = дЬедед+д с,д,= ЯСР+ ЬФоУсредняя результаты измерения ЬРрцна интервале времени, равном М посылкам, путем суммирования с последующимделением, можно при помощи накапЗ 0 ливаюшего сумматора и дешифраторауправлять фазоврашателями, подключенными к выходу элемента задержки, и, таким образом, компенсировать параэитныйфазовый набег, повышая помехоустойчивость демодулятора.Работает демодулятор следующим образом.Сигнал, приходящий на .вход демодулятора, поступает на первый вход перемножителя 11 синфазного канала непосредственно, а на первый вход перемножителя 11 квадратурного канала через фазовращатель 14, кроме того, онпоступает на вход элемента задержки 1,где задерживается на время, равное длительности одной элементарной посылки.Сигнал на выходах двух соседних фаэовращателей 2 сдвинут относительнодруг друга на угол, равный/Й , причемсдвиг по фазе относительно сигнала, снимаемого с.элемента задержки 1, производится как в положителЬную, так и вотрицательную стороны. Максимальныйсдвиг составляет90 ф . В каждыймомент времени ко вторым входам 55перемножителей 1 1 подключен толькоодин из фазовращателей 2 при помощисоответствукнцего ключа 3. Управлениеключами 3 производится дешифратором10. При нулевой расстройке несущей частоты сигнал на вторые входы перв- множителей 11 поступает непосредственно с выхода элемента задержки 1, минуя фаэовращатели 2. Перемножители 11 и последовательно включенные с ними интеграторы 12 вычисляют напряжения, пропорциональные синусу и косинусу разности фаз между двумя соседними посылками. Делитель 5 вычисляет отноше ние Ьп ЬР-"фМР, блок 15 вычисленияЮОЬ ЬРразности фаз с учетом знаков 4 РЬР и СОЬДР, вырабатываемых блоками 13 определения знака, определяет разность И фаз ЬР между соседними посылками. Если значения разностей фаз вследствие манипуляции попадают во 2-ю или 3-ю четверть, то они переводятся путем вычитания 180 в Х-ю или 4-ю четверть. 20ООтсчет углов производится со знаками "плюс" для первой четверти и минус для четвертой четверти. Первый накапливаваюший сумматор 7 суммирует значения ния АР на интервале и 1 посылок. Де 25 литель 8 делит суммарное значение Е ЬР на И), вычисляя среднее значение ЬРср . Второй накапливающий сумматор 9 суммирует ДРр. и управляет работой дешифратора 10. 30Дешифратор 10 в зависимости откода сигнала, поступающего с выхода сумматора 9, вырабатывает по одному из выходов сигнал для отпирания одного иэ соответствующих ключей 3. Предположим, в момент включения демодулятора дешифратор 10 под действием сигнала с накапливающего сумматора 9 установлен в такое состояние, что открыт 40 ключ 3, вход которого соединен с выходом элементе задержки 1, Это означает, что Фс в момент включения на выходе сумматора 9 произвольно установлена в нулевое состояние, т.е.ЮР ;-О, 45 Если расстройка несущей частоты сигнала отсутствует, то ДФсР, вычисленное через ПТ посылок, равно нулю, и нуль, добавленный в некапливаюший сумматор 9, не изменяет состояния дешифратора 10.При расстройке несущей частоты, ДР1 не равно нулю, в накапливающий сумма 55тор 9 добавляется число, соответствующее ЬРцР,ЬЬЛ, выход сумматора 9 изменяет свое состояние и дешифратор 10 выдает команду на включение соответствуюшего ключа, который подключает ко входу перемножителей 11. тот фаэоврашатель 2. фаза выходного сигнала которого скомпенсировела бы паразитный набег по фазе между посылками, вызванный уходом несущей частоты сигнала от номинальной.Блок 6 вычисления разности фазпредназначен для устранения обратнойработы, которая может возникнуть приЬРР =180, Выход блока 6 является0выходом демодулятора.Таким образом, в демодуляторе помехоустойчивость определяется сдвигом фаэ между двумя соседними фазоврашателями, число которых можно брать достаточно большим, не усложняя схемы демодулятора. Например, увеличение числа фазовращателей в два раза увеличивает разрядность сумматоров и дешифратора всего лишь на один разряд.формула изобретенияДемодулятор сигналов с фазоразностной модуляцией, содержащий элемент задержки, выход которого подключен ко входам фазовращателей, выходы которых соединены с первыми входами соответствукнцих ключей, выходы которых подключены ко входам элемента ИЛИ, выход которого соединен с первыми входами перемножителей, выходы которых через интеграторы подключены ко входам блоков определения знака, при этом второй вход одного перемножителя соединен со входом элементе задержки и со входом соответствующего фезоврешателя, выход которого подключен ко второму входу другого перемножителя, а выход элемента задержки соединен с первым входом соответствующего ключа; выход которого подключен к соответствующему входуэлемента ИЛИ, причем выход соответствующего блока определения знака соединен со входом первого блока вычисления разности фаз, о т л и ч а ю щ н йс я тем, что, с целью повышения помехоустойчивости при автокорреляционном приеме, введены последовательно соединенные первый делитель, второй блок вычисления разности фаэ, первый накапливающий сумматор второй делитель, второй накапливающий сумматор ,и дешифратор, выходы которого подключены ко вторым входам ключей,ель И, Мигуно в Редактор В. М Заказ9077/6 Н. Ш оррек 2 илиал ППП "Патент", г. Ужгород, Проектная 7 790прй этом выходы интеграторов соединенысоЪходами первого делителя, а выходыблоков определения знака подключены ксоответствующим входам второго блокавычисления разности фаз. ир ВНИИПИ Гос по делам 3035, Москв361 8Источники информации,принятые во внимание при экспертизеФ1. Авторское свидетельство СССРМ 587635, кл. Н 04 Ь 27/22, 1976(прототип)9 Подписноеарственного комитета СССРзобретений и открытийЖ, Раушская набд, 4

СмотретьЗаявка

2700795, 25.12.1978

ПРЕДПРИЯТИЕ ПЯ Р-6510

ЕВДОКИМОВ ВЛАДИМИР КУЗЬМИЧ, СИДОРОВ НИКОЛАЙ МИХАЙЛОВИЧ

МПК / Метки

МПК: H04L 27/227

Метки: демодулятор, модуляцией, сигналов, фазоразностной

Опубликовано: 23.12.1980

Код ссылки

<a href="https://patents.su/4-790361-demodulyator-signalov-s-fazoraznostnojj-modulyaciejj.html" target="_blank" rel="follow" title="База патентов СССР">Демодулятор сигналов с фазоразностной модуляцией</a>

Предыдущий патент: Устройство для формирования фазоманипулированного сигнала

Следующий патент: Автоматический номеронабиратель

Случайный патент: Крюк