Аналоговый оптимизатор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 769566

Автор: Трофимов

Текст

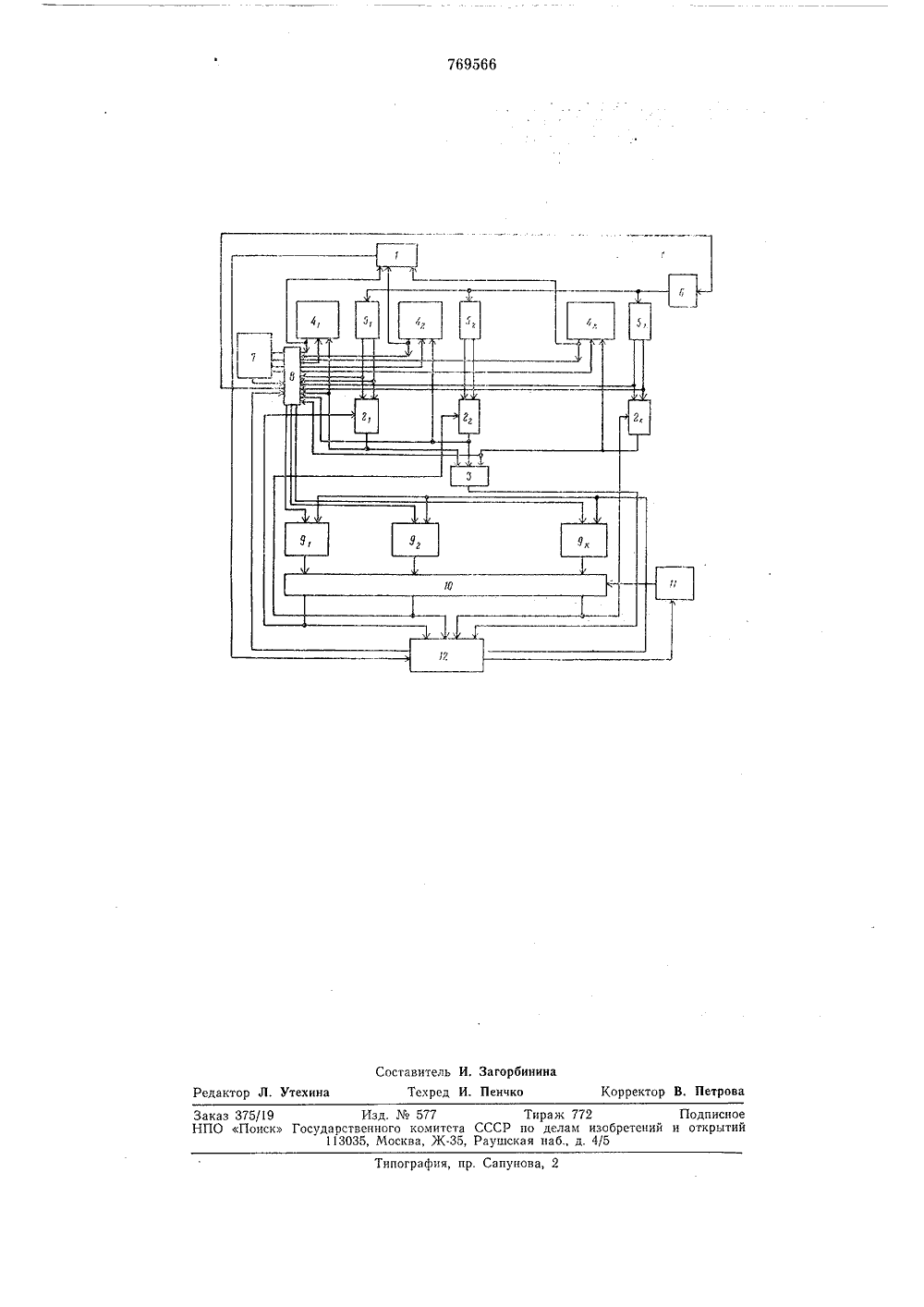

О П И С А Н И Е (111769566ИЗОБРЕТЕНИЯ Союз Советских Социалистических Республик(45) Дата опубликования описания 07.10.8 1) М 1 Улзб 066 7/48Сл 066 7/122 сударствекнык комите СССР о делам изобретений(54) АНАЛОГОВЫЙ ОПТИМИЗАТО 0 Изобретение относится к вычислительнойтехнике и предназначено для получения целочисленных решений прямой и обратной задач оптимального резервирования при любых законах распределения времени между отказами устройств.Предлагаемое техническое решение является усовершенствованием известного устройства, описанного в авт. свид.419917. 1Аналоговый оптимизатор по основномуизобретению содержит й блоков нелинейности, выходы которых соединены со входами блока перемножения, /е блоков умножения на постоянный коэффициент, выходы 15 которых соединены со входами сумматора и первыми входами соответствующих блоков нелинейности, переключатель, Й схем установки затрат, блок развертки и блок измерения градиента, первый и второй 20 входы которого через переключатель подключены ко вторым входам и выходам блоков нелинейности, Выход блока развертки соединен со входами Й схем установки затрат, первый и второй выходы каждой из которых соединены со входами соответствующего блока умножения на постоянный коэффициент и через переключатель с третьим и четвертым входами блока измерения градиента. 30 Недостатком такого оптимизатора являются малые точность и быстродействие, связанные с большим объемом переключений, ручных регулировок и измерений, выполняемых оператором в процессе решения с субъективными ошибками.Целью изобретения является повышение точности работы и быстродействия аналогового оптимизатора.Эта цель достигается тем, что в аналоговый оптимизатор введены /с блоков памяти, блок сравнения, интегратор и блок синхронизации, первый выход которого через интегратор соединен с управляющим входом блока сравнения, выходы которого подключены к дополнительным входам блоков умножения на постоянный коэффициент и к группе входов блока синхронизации, второй выход которого соединен с дополнительным входом переключателя, дополнительные выходы которого подключены к первым входам блоков памяти, вторые входы которых соединены с третьим выходом блока синхронизации, первый и второй входы которого подключены соответственно к выходам блока перемножения и сумматора.На чертеже приведена структурная схема предлагаемого аналогового оптимизатора. Он состоит из блока перемножения 1, йблоков умножения на постоянный коэффициент 2 - 2 ь сумматора 3, А блоков нелинейности 4 - 4 ь схем установки затрат5 - 5 ь блока развертки 6, блока измерения градиента 7, переключателя 8, й блоков памяти 9 - 9 ь блока сравнения 10,интегратора 11 и блока синхронизации 12.Блоки нелинейности 4 - 4 позволяютвоспроизводить любой формы нелинейныефункции одной переменной, Число блоковй выбирается любым, Выход каждого блока подключен ко входу блока перемножения 1, а вход каждого блока соединен свыходом соответствующего блока умножения 2. Кроме того, переключателем 8 входи выход каждого блока нелинейности 4могут поочередно подключаться к блоку измерения градиента 7.Блоки умножения 2 - 2, выполнены наоперационных усилителях, коэффициентыкоторых меняются дискретно в пределах 1,2, , п за счет изменения входных сопротивлений, переключаемых, например, шаговым искателем по сигналам с блока сравнения 10.Выходы блоков 2 - 2 подключены ксумматору 3 и через переключатель 8 кблоку развертки 6.Сумматор 3 состоит из операционногоусилителя в режиме суммирования с коэффициентом, равным единице по каждомувходу, п вольтметра. Все его входы подключены к выходам блоков умножения2 - 2 ь а выход - к блоку 12.Блок измерения градиента 7 состоит изэлектромеханического вибратора, операционных усилителей в режиме инвертирования и суммирования, аналогового блокаделения двух переменных и вольтметров.Переключателем 8 первые два входа блока7 могут одновременно подключаться ковходу и выходу каждого блока нелинейности 4 - 4 ь третий и четвертый входы - квыходам каждой пары усилителей схемустановки затрат 5 5 ь а выход блока7 - ко входам блоков памяти 9 - 9.Блок развертки 6 состоит из сдвоенногопотенциометра, питающегося двумя одинаковыми по абсолютной величине, но разными по знаку постоянными напряжениями.Движок сдвоенного потенциометра перемещается по сигналам с блока 12, например,с помощью следящей системы. Вход блока6 подключен через переключатель 8 к выходам блоков умножения 2 - 2 ь а выходыподключены на А входных сопротивленийсхемы установки затрат 5 - 5 ьСхемы установки затрат 5 - 5 к состоятиз переменных сопротивлений и операционных усилителей в режиме инвертирования.Переключатель 8 может быть выполнен,например, в виде автоматического электромеханического коммутатора на щаговых искателях и реле, управляемого по сигналамс блока 12,5 10 15 20 25 Зо 35 40 45 50 55 60 65 Блоки памяти 9, - 9 к выполнены на операционных усилителях с запоминанием результата при остановке решения. Первыйвход каждого блока памяти 9 через переключатель 8 подключен к выходу блока измерения градиента 7, Вторые входы блоковпамяти 9 - 9 подключены к выходуСброс блока 12. Выход каждого блокапамяти подключен ко входу блока сравнения 10,Блок сравнения 10 является (1+1)-входовым устройством, на Й входов которогоподключены выходы й блоков памяти9 - 9 ь а на (1+1)-й вход подключен выход интегратора 11. Выходы блока 10 подключены к блоку 12 и ко входам соответствующих блоков умножения 2 - 2 ь.Вход интегратора 11 подключен к первому выходу блока 12, а выход - к (1+1) -мувходу блока сравнения 10.Блок 12 содержит генератор тактовыхимпульсов, две схемы сравнения напряжений, схему возврата блоков памяти 9 - 9в исходное состояние, вольтметры и коммутирующие устройства. Входы блока 12 соединены с й выходами блока сравнения 10,выходами блока перемножения 1 и сумматора 3. Первый выход блока 12 подключенко входу интегратора 11, второй - ко входупереключателя 8, третий - ко вторым входам Сброс блоков памяти 9 - 9 а,Исходными данными для решения задачявляются структурная схема системы, состоящая из Й последовательно соединенныхучастков резервирования, таких, что отказлюбого одного участка приводит к отказувсей системы; экспериментальные или расчетные зависимости р; =(с;, и;), при любых законах распределения случайных величин и любых режимах работы участков,где и.; - число параллельно включаемых на-м участке элементов от 1 до и, р; - вероятность безотказной работы -го участкарезервирования за время выполнения задания, с; - затраты на каждый нерезервированный участок (=1, 2., й),Обозначим через с затраты (вес, стоимость, габариты и пр.), допускаемые навсю резервированную систему, через р -заданный уровень безотказной работы резервированной системы.Перед решением выбирается число блоков нелинейности 4 - 4 ц равное Й. Накаждом из блоков набираются, например,при решении прямой задачи оптимальногорезервирования соответствующие функцииРг=1(сь ц;), =1, й, Коэффициенты всехблоков умножения 2 - 2, устанавливаютсяравными единице, а на сумматоре 3 устанавливается опорное напряжение, пропорциональное допускаемым затратам с. По сигналу Пуск с блока 12 приходит первый тактовый импульс, и выполняется первый шаг решения, При этом блок изме 76956640 45 50 55 рения градиента 7 переключателем 8 подключается к клеммам первого блока нелинейности 4 и первой схемы установки затрат 50 а также к первому блоку памяти 9 ь Напряжение на третьем и четвертом входах блока измерения градиента 7 модулируется вибратором и подается на вход блока нелинейности 4 ь С его выхода снимается модулированное напряжение, которое преобразуется в переменное напряжение, пропорциональное по амплигуде приращению функции рна шаге сь Зто напряжение подается как делимое на вход блока деления в блоке измерения градиента 7. На другой вход блока деления подается как делитель напряжение, полученное как разность напряжений на третьем и четвертом входах блока измерения градиента 7, Напряжение Ьс выхода блока 7 подается на вход блока памяти 9 и запоминается.С приходом второго тактового импульса переключатель 8 подключает входы и выход блока измерения градиента 7 к клеммам следующих блока нелинейности 4, схемы установки затрат 5, блока памяти 9 и аналогично запоминается величина Л и т. д. до последнего блока нелинейности 4.При этом напряжения с выходов блоков умножения 2 - 2 последовательно синхронно подаются переключателем 8 на вход блока развертки 6. Его следящая система перемещает движок сдвоенного потенциометра, последовательно обеспечивая равенство напряжений на выходе каждого блока 2 - 2 и на выходе блока развертки 6. По окончании первого цикла замеров и запоминания по сигналу с блока 12 запускается интегратор 11, с выхода которого на (й+ 1)-й вход блока сравнения 10 подается линейно убывающее напряжение. Как только линейно убываюгцее напряжение по абсолютной величине станет равным какому- либо одному из напряжений Ь;, =1, й оказавшемуся максимальным среди всех остальных, с соответствующего выхода блока сравнения 10 подается сигнал на соответствующий блок умножения 2;, =1, й, и его коэффициент увеличивается на единицу.Одновременно с третьего выхода блока 12 подается импульс Сброс на вторые входы блоков памяти 9 - 9, и блоки памяти возвращаются в исходное состояние, с первого - сигнал на переключатель 8, и клеммы блоков 4, 50 9 снова подключают 5 0 15 20 25 Зо 35 ся к блоку измерения градиента 7. Интегратор 11 возвращается в исходное состояние автоматически.С приходом следующего тактового импульса начинается выполнение второго шага решения, и цикл повторяется,После выполнения Л шагов решения напряжение на выходе сумматора 3 может быть равным нулю (наложенное ограничение по затрате израсходовано точно) либо больше нуля (перерасход). В последнем случае уменьшается на единицу коэффициент того блока умножения, у которого на Ж-м шаге этот коэффициент был увеличен на единицу. Оценивается показание прибора сумматора 3 и, если оно по абсолютной величине меньше любого из значений сь тс решение закончено.Напряжение на выходе блока перемножения 1 соответствует достигнутому значению целевой функции для всей резервированной системы, напряжение на выходе сумматора 3 соответствует суммарной затрате, а зафиксированный коэффициент каждого блока умножения 2 =1, Й соответствует числу параллельно включенных устройств на каждом участке резервирования.Благодаря введению новых элементов и связей устройство обеспечивает более высокую точность и быстродействие получения статистических характеристик проектируемой аппаратуры,Формула изобретения Аналоговый оптимизатор по авт. свид. Л 419917, о т л и ч а ю щ и й с я тем, что, с целью повышения точности работы и быстродействия, в него введены Й блоков памяти, блок сравнения, интегратор и блок синхронизации, первый выход которого через интегратор соединен с управляющим входом блока сравнения, выходы которого подключены к дополнительным входам блоков умножения на постоянный коэффициент и к группе входов блока синхронизации, второй выход которого соединен с дополнительным входом переключателя, дополнительные выходы которого подключены к первым входам блоков памяти, вторые входы которых соединены с третьим выходом блока синхронизации, первый и второй входы которого подключены соответственно к выходам блока перемножения и сумматора.769566 Составитель И, Загорбинина Техред И. Пенчко Корректор В. Петрова Редактор Л. Утехина Заказ 375/19 Изд. Ма 577 Тираж 772 ПодписноеНПО Поиск Государственного комитета СССР по делам изобретений н открытий113035, Москва, Ж, Раушская наб., д. 4/5 Типография, пр. Сапунова, 2

СмотретьЗаявка

2666387, 25.09.1978

ПРЕДПРИЯТИЕ ПЯ А-7672

ТРОФИМОВ ВЛАДИСЛАВ ДМИТРИЕВИЧ

МПК / Метки

МПК: G06G 7/48

Метки: аналоговый, оптимизатор

Опубликовано: 07.10.1980

Код ссылки

<a href="https://patents.su/4-769566-analogovyjj-optimizator.html" target="_blank" rel="follow" title="База патентов СССР">Аналоговый оптимизатор</a>

Предыдущий патент: Устройство для моделирования диффузионных процессов

Следующий патент: Устройство для моделирования систем энергоснабжения

Случайный патент: Способ получения -органосилилметиленлактамов