Интерполятор

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Номер патента: 765821

Авторы: Коробейников, Кургаев

Текст

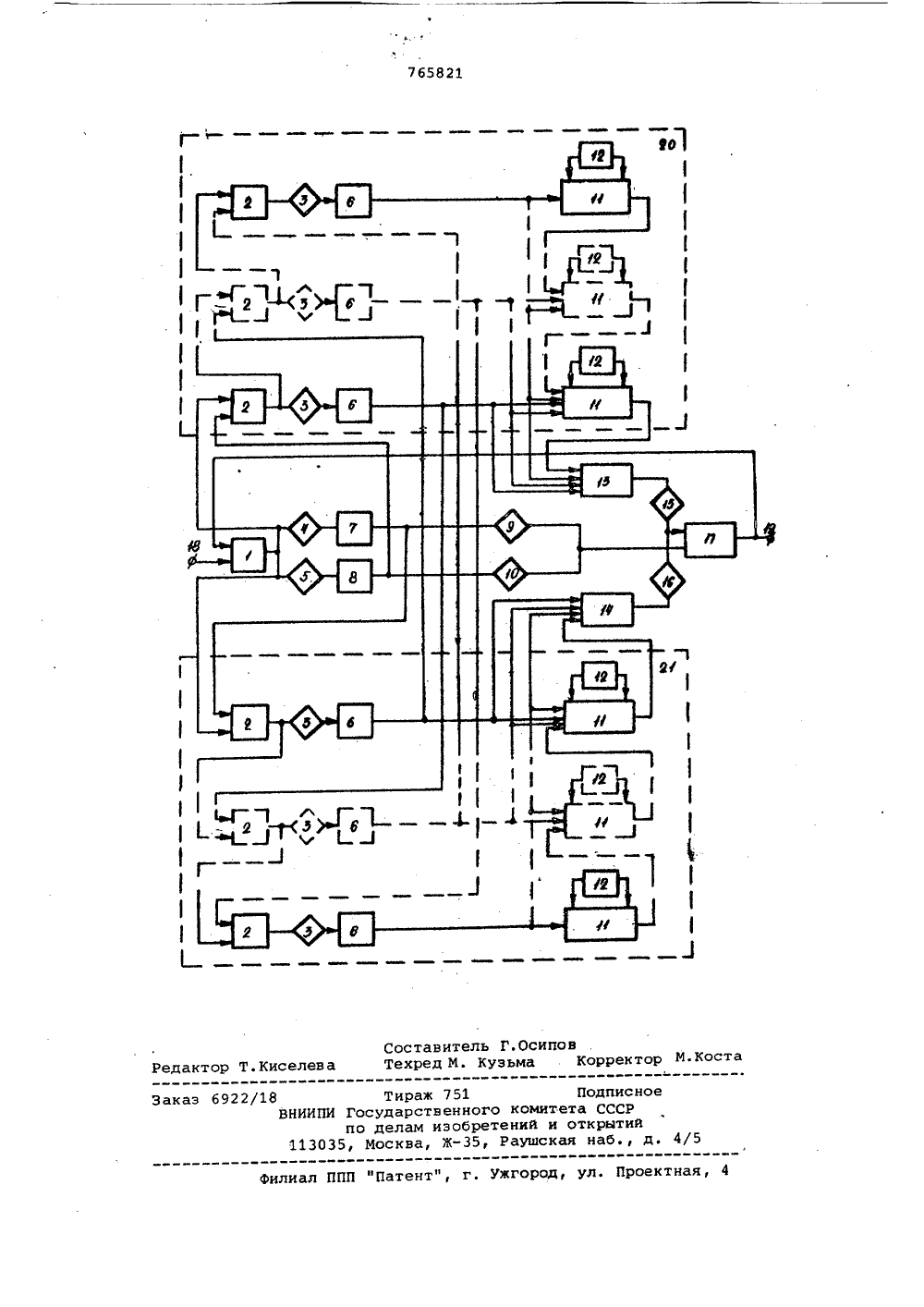

(51)М, Кл,8 Сч 06 6 7/30 Государственный комитет СССР по делам изобретений и открытий(72) Авт р. изобретения А.ф. Кургаев и В.Н. Коробейников Ордена Ленина институт кибернетики Академии наук Украинской ССР(71) Заявитель 154) ИНТЕРПОЛЯТОР Изобретение относится к вычислитель" ной технике и может быть использовано для воспроизведения функций при выводе информации на индикаторы, граФопостроители и исполнительные ме ханизмы в управляющих вычислительных системах.Известен линейный интерполятор с компенсацией инструментальной погрешности, использующий отрицатель О ную обратную связь для компенсации на каждом последующем шаге ошибок интегрирования, накопленных на предыдущем шаге и содержащий последовательно соединенные цифроаналоговый 15 преобразователь, сумматор, ключ, аналоговое запоминающее устройство и интегратор, выход которого подключен к другому входу сумматора 11 .Недостатком этого устройства яв" 20 ляется высокая погрешность, связанная с аппроксимацией исходной Функции кусочно-линейными отрезками, а также с тем, что процесс запоминания приращения функции происходит 25 одновременно с процессом интегрирования этого приращения.Наиболее близким к предлагаемому по технической сущности является интерполятор произвольного порядка, ис 2пользующий отрицательную обратнуюсвязь для компенсации на каждом последующем шаге инструментальных оши-бок интегрирования, накопленных напредыдущем шаге (2,Более высокая точность достигается за счет увеличения порядка восстанавливающего полинома.Недостатком является наличие погрешности восстановления Функции, обусловленной тем, что процесс фиксацииприращений накладывается на процессинтегрирования этих приращений.Цель изобретения - повышение точности.Цель достигается тем, что интерполятор, содержащий выходной интегратор, выход которого подключен к одному из входов первого сумматора, дру-,гой вход которого является входом интерполятора, выход первого сумматорачерез первый ключ связан с входом первого запоминающего элемента, и первый блок нелинейной интерполяции, содержащий ряд цепей, каждая из которыхсостоит иэ последовательно соединенных сумматора, ключа, запоминающегоэлемента и интегратора, входы сумматора первой цепи подключены соответственно к выходу первого сумматора ик выходу первого запоминающего элеменга, первый нход сумматора каждой последующей цепи соединен с выходом сумматора предыдущей цепи, другой входинтегратора предыдущей цепи соединенс выходом интегратора последующейцепи, выход запоминакцего элементакаждой цепи соединен с остальнымивходами интеграторов всех предыдущихцепей, в цепи обратной связи интег-ратора каждой цепи блока нелинейнойинтерполяции включен разрядный ключ,дополнительно содержит второй блокнелинейной интерполяции, выполненный аналогично первому блоку нелинейной интерполяции, второй и третий сумматоры, второй запоминающий 5элемент и пять ключей, при этом выход первого сумматора через второйключ соединен с входом второго запоминающего элемента, выходы первогои второго запоминающих элементов , 2 рсоответственно через третий и четвер-,тый ключи соединенц с первым входомвыходного интегратора,выходы интегратора первой цепи к эапомкнающих элементов всех цепей первого блока нелинейной интерполяции подключены к нхо"дам второго сумматора, выходя интегратора первой цепи и запоминающих элементов нсех . цепейвторого блока нелинейной интерполяцииподключены к нходам третьего сумматора, выходы второго и третьего сумматоров соединены с вторым входом выходного интегратора соответственночерез пятый и шестой ключи, входысумматора первой цепи второго блоканелинейной интерполяции соединенысоответственно с выходом первогосумматора и с выходом второго запоминающего элемента, вторые входы сумматоров второй и всех последующих 40цепей каждого блока нелинейной интерполяции соединены с выходами запоминающих элементов предыдущих по номеру цепей другого блока нелинейнойинтерполяции. 45На чертеже представлена блок-схемаустройства.Она содержит сумматоры 1 и 2, ключи 3-5, эапоминанщие элементы 6-8,ключи 9 и 10, интеграторы 11, раэ- ррядные ключи 1, сумматоры 13 к 14,ключи 15 и 1 б, ньжодной интегратор 17вход 18, выход 19 интерполятора, блоки 20 и 21 нелинейной интерполяции.Интерполятор работает следующим образом,На вход 18 в момент времени с сЭпериодом Т, ран ным постоянной времени интеграторон 11 и 17 поступаетступенчатое напряжение, величина каждой ступеньки соответствует значению бОинтерполируемой функции н указанныймомент времени.Работа интерполятора различна длячетных и нечетных периодон интерполирования. В четные интервалы времени замкнуты ключи 4, 10 и 16, а такжеключи 3 и 12 второго блока нелинейной интерполяции, остальные ключи "5, 9 и 15, а также ключи 3 и,12 первого блока нелинейной интерполяцииразомкнуты. В нечетные интернаты вре-,мени разомкнуты ключи 4, 10 и 16, атакже ключи 3 и 12 второго блока нелинейной интерполяции, ключи 5,9 и15, а также ключи 3 и 12 первого блока нелинейной интерполяции при этомзамкнуты.В четные интервалы времени интеграторы 11, входааие в состав блока 20,с помощью ключей 12 устанавливаютсяв начальное состояние, а его запоминающие элементы с ключами 3 подключаются к выходам сумматоров 2, ПервЫй блок 21 ,нелинейной интерполяции н четные интервалы времени черезсумматор 14 подключается ко входу.интегратора 17,Таким образом, н четные интервалывремени происходит подготовка к работе второго блока 20 нелинейной интерполяции - начальная установка егоинтеграторов 11 и запоминание на элементах б значений напряжений, поступающих с выходов соответствующих сумматоров 2, а первый блок 21 нелинейной интерполяции в эти периоды времени участвует в формировании выходногонапряжения интерполятора.В нечетные интервалы нремени происходит подготовка к рабое первого блока нелинейной интерполяции 21, в товремя как второй блок нелинейнойинтерполяции 20 участвует н формировании выходного напряжения кнтерполятораПри этом на выходе сумматора 1 вырабатывается текущее значение разнос"ти между входным и выходным напряжениями интерполятора, т.е, первое приращение, которое н течение четногоинтервала времени Т запоминается взапоминающем элементе 7, а в нечетныеинтерналы времени - в запоминающемэлементе 8,В течение одного, например, четного интервала интерполирования интер"полятор работает следующим образом.На выходе сумматора 2 первой цепиблока 20 вырабатынается текущее значение приращения второго порядка, какразность между текущим значением первого приращения, формируемым на выходе сумматора 1, и значением первогоприращения, запомненным в элементе 8н предыдущем (нечетном) интервалевремени.Аналогично, на выходе сумматора 2последней .(а-той) цепочки блока 20н четные интервалы времени вырабатывается текущее значенйе приращения(в+1-го порядка, как разность междутекущим значением приращения а-го порядка, Формируемым на выходе суммато-ра 2 предпоследней цепи блока 20, изначением приращения 1 п-го порядка с выхода элемента 6 предпоследней цепи блока 21, запомненным в предыдущем интервале времени.С выходов сумматоров. 2 цепочек блока 20 аналоговые напряжения, равные приращениям интерполируемой функции фсоответствующего порядка, череззамкнутые ключи 3 поступают на запоминакюцие элементы б этих же цепей ив течение четного интервала временизапоминаются в них.К моменту окончания четного интервала времени Т в запоминающем элементе 7 содержится величина аналогового напряжения, равная первому приращению интерполируемой функции, а 15в запоминающих элементах 6 второгоблока 20 нелинейной интерполяции - величины аналогового напряжения, рав"ные второму и высшим приращениям ичтерполируемой функции. В это время 20на входы интегратора 17 поступают напряжения с выхода запоминающего элемента 8 и (через замкнутый ключ 16и сумматор 14) напряжение от первогоблока нелинейной интерполяции 21,Приэтом интеграторы 11, сумматор 14и интегратор 17 вырабатьн ают интерполирующий лолином, поступающий навыход 19.Во время следующего (нечетного)интервала времени в результатепереключения всех ключей из замкнутого состояния в разомкнутое и наоборот функции блоков нелинейной интерполяции 20 и 21 меняются.Описанный процесс работы интерполятора повторяется. В результатена выходе 19 образуется кусочнонелинейное напряжение, которое интерполирует значения воспроизводимой функции. 40Точность интерполяции повышена засчет разделения во времени процессовзапоминания приращений и их интегрирования. Технико-экономический эффект обусловлен тем, что повышение точности 45 достигнуто при существенном снижении требований по быстродействию к каждому в отдельности запоминающему элементу.50Формула изобретения Интерполятор, содержащий выходной интегратор, выход которого подключен к одному из входов первого сумматора, другой вход которого является входом интерполятора выход первого сумматора через первый ключ связан с входом первого запоминающего элемента, и первый блок нелинейной интерполяции, содержащий рядцепей, каждая из которых состоит изпоследовательно соединенных сумматора, ключа, запоминающего элементаи интегратора, входы сумматора первойцепи годключены соответственно к выходу первого сумматора и к выходупервого запоминающего элемента, первый вход сумматора каждой последующей цепи соединен с выходом сумматора предыдущей цепи, другой вход интегратора предыдущей цепи соединенс выходом интегратора последующейцепи, выход запоминающего элементакаждой цепи соединен с остальнымивходами интеграторов всех предыдущихцепей, в цепи обратной связи интегратора каждой цепи блока нелинейнойинтерполяции включен разрядный ключ,о т л и ч а ю щ и й с я тем, что,с целью повышения точности, интерполятор дополнительно содер кит вторсйблок нелинейной интерполяции, выполнее 111 ый а 11 алогично перво.ту блоку нелинейной интерполяции, второй и третий сумматоры, второй запоминающийэлемент и пять к.1 поче 13, при этом выход первого сумматора через второйключ соединен с входом второго запоминающего элемента, выходы первого ивторого запоминающих элементов соответственно через третий и четвертыйключи соединены с первым входомвыходного интегратора, выходы интегратора первой цепи и запоминающихэлементов всех цепей первого блоканелинейной интерполяции подключенык входам второго сумматора, выходыинтегратора первой цепи и запоминающих элементов всех цепей второго блока нелинейной интерполяции подключенык входам третьего сумматора, выходывторого и третьего сумматоров соединены с вторым входом выходного интегратора соответственно через пятыйи шестой ключи, входы сумматора первой цепи второго блока нелинейной интерполяции соединены соответственнос выходом первого сумматора и с выходом второго запоминающего элемента,вторые входы сумматоров второй и всехпоследующих цепей каждого блока нелинейной интерполяции соединены с выходами запоминающих элементов предыдущих по номеру цепей другого блоканелинейной интерполяции. Источники информации,принятые во внимание при экспертизе 1. Авторское свидетельство СССР Р 36494 3, кл. С 06 С 7/30, 1971,2, Авторское свидетельство СССР Р 480094, кл. С 1 06 б 7/30, 1973 (прототип).765821 Составитель Г.ОсиповРедактор Т.Киселева Текред М. Кузьма Корректор М Ко 922/18ВНИ к 30 илиал ППП "Патентф, г. Ужгород, Ул. Проектная, 4 Тираж 751 Государственн по делам иэоб Москва, ЖПодписноео комитета СССРтений и открытийРаушская наб., д. 4/5

СмотретьЗаявка

2688954, 28.11.1978

ОРДЕНА ЛЕНИНА ИНСТИТУТ КИБЕРНЕТИКИ

КУРГАЕВ АЛЕКСАНДР ФИЛИПОВИЧ, КОРОБЕЙНИКОВ ВАЛЕРИЙ НИКОЛАЕВИЧ

МПК / Метки

МПК: G06G 7/30

Метки: интерполятор

Опубликовано: 23.09.1980

Код ссылки

<a href="https://patents.su/4-765821-interpolyator.html" target="_blank" rel="follow" title="База патентов СССР">Интерполятор</a>

Предыдущий патент: Функциональный генератор

Следующий патент: Устройство для моделирования судовой газотурбинной установки

Случайный патент: Измерительный коммутатор