Цифровой генератор функций

Похожие патенты | МПК / Метки | Текст | Заявка | Код ссылки

Текст

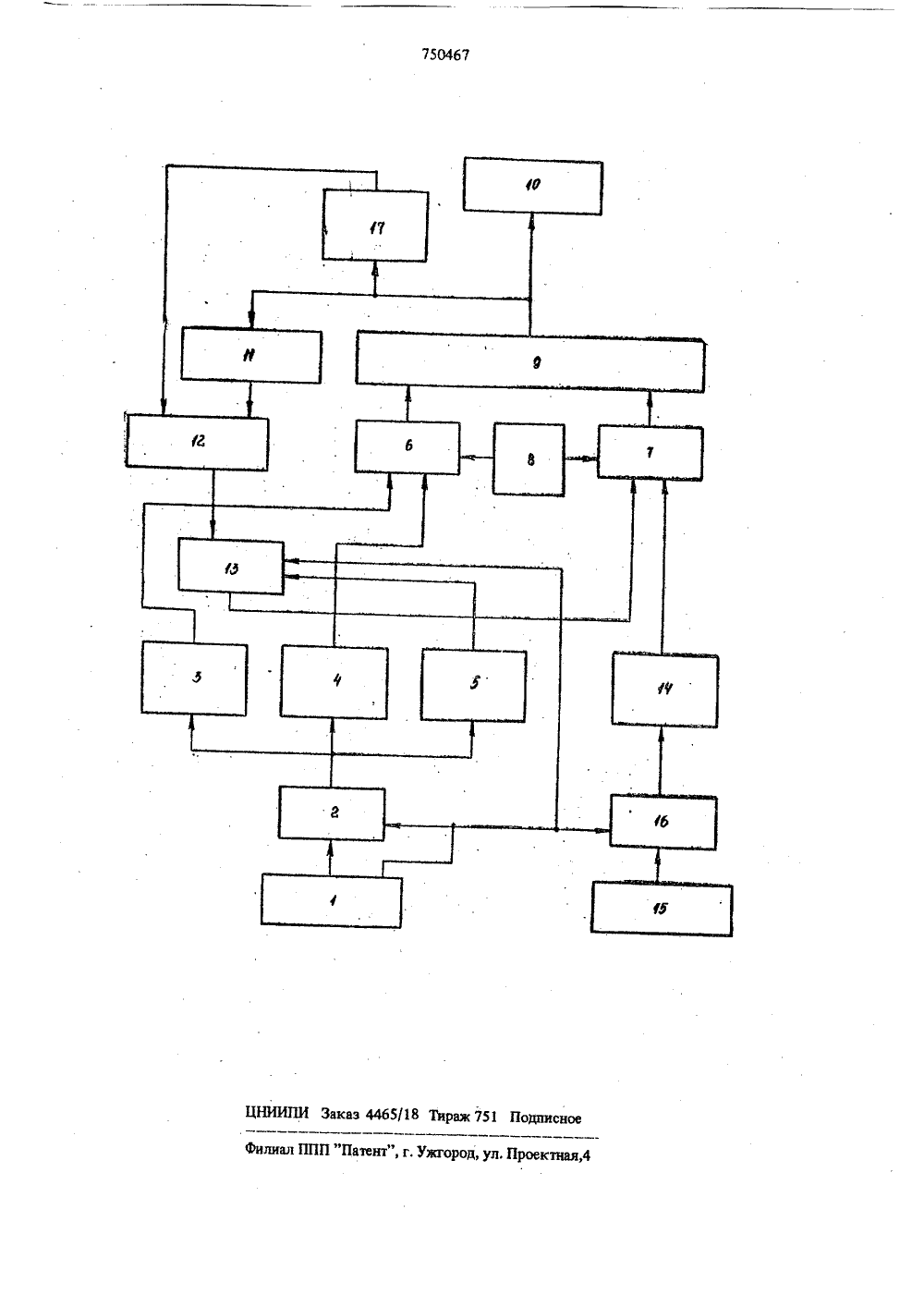

О П И С А Н И Е750467ИЗОБРЕТЕН ИЯК АВТОРСКОМУ СВИДЕТЕЛЬСТВУ Союз Советски кСоцнелистнчески креспублик(23) Приоритет вв делам изобретений н вткрытнй(088.8) Дата опубликования описания 23,07,80(71) Заявитель Омский политехнический институт(54) ЦИФРОВОЙ ГЕНЕРАТОР ФУНКЦИЙ Изобретение относится к вычислительнойтехнике и может быть использовано для аппаратурной реализации аналитических функцийв специализированных и универсальных быстро.действующих цифровых вычислительных ма.Известно устройство, содержащее преобра.зователь временного интервала в последовательность импульсов, блок весовых коэффициентов, выходной счетчик-регистр, блок де.10кодирования и блок памяти 1),Недостатки - большой объем памяти инизкое быстродействие.Известен также цифровой генератор функций, содержащий регистр младших и регистрстарших разрядов аргумента, первый, второйтретий, четвертый и пятый блоки памяти,первый и второй коммутаторы, сумматор, буферный регистр, регистр результата и блокуправления, причем выход регистра старшихразрядов подключен к адресным входам первого, второго и третьего блоков памяти,выходы первого и второго блоков памятичерез первый коммутатор подключены к первому, а выход второго коммутатора - ко второму входу сумматора, выход которого подключен ко входу буферного регистра и регистра результата, выходы блока управления подключены к управляющим входам первого и второго коммутатора. Кроме того, он со. держит блок сдвига и преобразователь прямого кода в дополнительный, причем выход регистра младших разрядов аргумента подклю чен к адресному входу четвертого блока памяти, выход которого соединен с первым входом второго коммутатора, выход сумма., тора подключен к адресному входу пятого блока памяти, выход которого, а также выход буферного регистра соединен с соответствующимивходамиблока сдвига, выход блока сдвига подключен к информационному, а выход третьего блока памяти - к управляющему входу преобразователя прямого кода в дополнительный, выход которого подключен ко второму входу второго коммутатора 2.Недостатком данного цифрового генератора функций является относительно большая суммар.ная емкость используемых в нем блоков памяти,750467 10 15 20 ЭО что ограничивает применение его в универ.салыпях ЦВМ,Цель изобретения - сокращение объемаоборудования при незначительном (не превосходящем времени одного сложения) уменьшениибыстродействия устройства,Поставленная цель достигается тем, что визвестное устройство введены второй преобразователь прямого кода в дополнительныйи блок коррекции, причем первый выходрегистра старних разрядов аргумента подключен ко входу блока коррекции, а второйвыход подключен к управляющим входамблока коррекции, второго преобразователя пря.мого кода в дополнительный, и второму уп.равляющему входу первого преобразователяпрямого кода, в дополнительный, выход блокакоррекции подключен. ко входам первого,второго и третьего блоков памяти, выход регистра младших разрядов аргумента подклю.чен к входу второго преобразователя прямогокода в дополнительный, выход которого под.ключен ко входу четвертого блока памяти. На чертеже представлена блок. схема пред лагаемого устройства.Устройство состоит из последовательно соединенных регистра 1 старших разрядов аргу. мента и блока 2 коррекции, выход которого подключен к адресным входам первого, вто. рого и третьего блоков 3, 4, 5 памяти из первого и второго коммутаторов 6 и 7, управляющие входы которых подсоединены к блоку 8 управления, а выходы - к первому и второму входам сумматора 9. Выход сумматора 9 подключен ко входам регистра 10 ре. зультата и буферного регистра 11, а выход буферного регистра 11 через первый вход блока 12 сдвига и первый преобразователь 13 прямого кода В дополнителъеыи ко входу 40 второго коммутатора 7; другой вход которого соединен с выходом четвертого блока 14 памяти, Кроме того, в состав устройства входят последовательно соединенные регистр 15 младших разрядов аргумента и второй преоб разователь 16 прямого кода в дополнитель. ный, выход которого подключен к адресному входу четвертого блока 14 памяти, а также пятый блок 17 памяти, адресный вход которого соединен с выходом сумматора 9, а выход подключен к второму входу блока 12 сдвига, Выходы первого и второго блоков 3 и 4 памяти подключены ко входам первого коммутатора 6, а выход третьего блока 5 памяти - к первому управляющему входу первого преобразователя 13 прямого кода в дополнительный. Кроме того, младший разряд регистра 1 старших разрядов аргумента подключен к управляющим входам второго преоб 4разователя 16 прямого кода в дополнительный, блока коррекции 2 и ко второму управляющему входу первого преобразователя 13 прямого кода в дополнительный.Работа цифрового генератора функций осуществляется следующим образом.В первом такте работы устройства, в зависимости от значения младшего разряда хх регистра старних разрядов аргумента, значе. ния узловой точки ХО и приращения аргумента дХ хранящихся соответственно на ре.)гистрах старших и младших разрядов аргумен. та 1 и 15 с помощью блока коррекции 2 и второго преобразователя 16 прямого кода в дополнительный преобразуются в значения Е и ЬЕ в соответствии с соотношениями:О,ЕСЛ 4 Х:О дХ,Есло Х=оо КО х +2:, езди Х=т 2 -дх, Есина Х=Х Значение приращения Ь 7, поступает на ад. ресный вход четвертого блока памяти, в кото. ром хранится таблица значений Ь 2 д 2 и с выхода этого блока памяти значение бф дЕ передается через второй коммутатор 7 на второй вход сумматора 9. Одновременно, в этом жс такте, значение ЕО, образованное на выходе блока 2 коррекции, поступает на адресные входы первого, второго и третьего блоков 3, 4, 5 памяти хранящих соответственно, таблицы значений р(7 ) о р(ф ) В первом такте работы устройства первый коммутатор 6 подключает к сумматору 9 выход первого блока 3 памяти, так что на выходе сумматора 9 в результате сложения поступивших на входы чисел 10 Г(2и оУ Л 2. образуется значение Соз (Л;)11 Ц, характеристика которого запоминается на буферном регистре 11, а мантисса передается на адресный вход пятого блока 17 памяти,хранящего таблицу значений 2.Во втором такте работы мантисса логариф. ма СОЯ ЬХР (ЕОпоступившая на адресный вход пятого блока 17 памяти, потенцируется таблицей, хранящейся в этом блоке памяти, и с помощью блока 12 сдвига, учитывающим характеристику бф (.1 Е " "11 (К , сдвигается на требуемое чйсло разрядов, образуя значение ЛЕ) Р(ЕО которое передается на первый преобразователь 13 прямого кода в дополнительный. Этотпреобразователь в случае 8 Яп " (Е ) =1 на.первом управляющем входе и 91(Х)= на втором управляющем входе, а также в случае 3 Яп(РДо) =-1 ) б (Хк) =-1 на этих входах выдает на выход число, по.750467 ступающее на его вход, а при других состоя.ниях управляющих входов образует дополни.тельный вход из числа на входе, взятого собратным знаком, так что на выходе преобразователя 13 прямого кода в дополнительныйвсегда образуется значение81 т(Х)Г(2. )ЬХ=Вфп(Г(Е ИС 1 п(Х )ДХР(Е )Это значение Ьо(Х)Ь 2 Г (Е) поступаетчерез второй коммутатор 7 на сумматор 9,складываясь на нем со значением Г(Е,),поступившим в этом же такте через первый. коммутатор 6 с выхода первого блока 3памяти. В результате сложения образуетсясогласно соотношения. Р(х) =Р(2 ) 9 п(Р (Х5 П(Х ) Жй+Иф й) ) искомое значе.ние функции Ь (Х) которое запоминаетсяна регистре 1 О результата.Сокращение объема оборудования, т.е. ем.кости блоков памяти в рассматриваемом устройстве, связано с меньшей, чем у Хо, раз.рядностью узловых точек Л, .Расчеты показывают, что для функцииг (Х) =ЙЯХ 0(Х( 3/4 и для разряднойсетки 1 э = 24, О = 398 Кбит,Й = 269 Кбит и, таким образом, выигрышв суммарной емкости блоков памяти превышает 32%. Для функции гг(х) =ГХ,1/16( Х ( 1 и О =24, имеем, соответственно Й = 665 Кбит и О = 365 Кбит, авыигрыш в суммарной емкости превышает55%. АФормула изобретения буферный регистр и регистр результата, причем выходы первого и второго блоков па.мяти через первый коммутатор второго блоков памяти через первый коммутатор подклю.ченык первому, а выход четвертого блокапамяти через второй коммутатор подключенко второму входам сумматора, выход кото.рого подключен ко входам буферного регистра результата и пятого блока памяти, выход 10 которого подключен ко входу блока сдвига,второй вход которого подключен к выходубуферного регистра, а выход - ко входупервого преобразователя прямого кода вдополнительный, управляющий вход которого 15 подключен к выходу третьего блока памяти,а выход подключен ко второму входу второго коммутатора, выходы блока управления подключены к управляющим входампервого и второго коммутаторов, о т л и ч а ю щ и й с я тем, что, с целью сокра.щения объема оборудования, в него введенывторой преобразователь прямого кода в дополнительный и блок коррекции, причем пер.вый выход регистра старших разрядов аргу мента подключен ко входу блока коррекции,а второй выход - подключен к управляю.щим входам блока коррекции, второго пре.образователя прямого кода в дополнительныйи второму управляющему входу первого пре. ЗО образователя прямого кода в дополнительный,выход блока коррекции подключен ко входампервого, второго и третьего блоков памяти,выход регистра младших разрядов аргумента подключен к входу второго преобразоваЗ 5 теля прямого кода в дополнительный, выходкоторого подключен ко входу четвертого блокапамяти.Цифровой генератор функций, содержащий регистр старшего разряда аргумента, регистр младшего разряда аргумента, первый, второй, третий, четвертый и пятый блоки памяти, первый преобразователь прямого кода в дополнительный, блок сдвига, блок управления, первый и второй коммутаторы, сумматор, буферный регистр и мутаторы, сумматор,Источники информации,принятые во внимание при экспертизе1, Авторское свидетельство СССР Н 451989,кл. 6 06 Г 1/02, 1973,2. Авторское свидетельство СССР по заявкеИф 2528831/18 - 24, кл. 6 06 Е 1/02, 20.09,77ф 5 (прототип) .

СмотретьЗаявка

2631175, 08.06.1978

ОМСКИЙ ПОЛИТЕХНИЧЕСКИЙ ИНСТИТУТ

ПОТАПОВ ВИКТОР ИЛЬИЧ, ФЛОРЕНСОВ АЛЕКСАНДР НИКОЛАЕВИЧ, ПЛОТНИКОВ МИХАИЛ ЮРЬЕВИЧ

МПК / Метки

МПК: G06F 1/02

Метки: генератор, функций, цифровой

Опубликовано: 23.07.1980

Код ссылки

<a href="https://patents.su/4-750467-cifrovojj-generator-funkcijj.html" target="_blank" rel="follow" title="База патентов СССР">Цифровой генератор функций</a>

Предыдущий патент: Цифровой генератор случайных процессов

Следующий патент: Устройство для синхронизации импульсов

Случайный патент: Устройство для разравнивания песка в легкоатлетической яме